Fターム[5F110HK08]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961)

Fターム[5F110HK08]の下位に属するFターム

Fターム[5F110HK08]に分類される特許

101 - 120 / 618

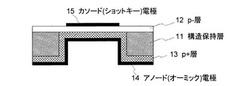

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】ダイヤモンド半導体からなるドリフト層と、半絶縁性ダイヤモンド層を有する構造保持材と、ダイヤモンド半導体からなるコンタクト層とを備えるダイヤモンド電子素子であって、前記構造保持材は、開口部を有し、前記ドリフト層の一方の面に積層されており、前記コンタクト層は、前記開口部内において、前記ドリフト層に直接積層されており、また、アノード電極は、前記開口部内の前記コンタクト層に設け、カソード電極は前記ドリフト層の他方の面に設けて、例えば、ショットキーバリアダイオードを実現する。単結晶ダイヤモンド基板の一方の基板面に欠陥層を形成した後、該基板面上に前記ドリフト層を成膜し、半絶縁性ダイヤモンド層を選択的に成長させて開口部を有する構造保持材を形成した後、前記基板はスマートカット法により素子部より分離する。

(もっと読む)

半導体記憶装置

【課題】メモリデータを外部回路を用いずに、コピーを行う半導体記憶装置を提供することを課題とする。

【解決手段】複数のメモリセルの第一端子が共通接続されたビット線と、ビット線に接続され、読み出し時にビット線を特定の電位にプリチャージするプリチャージ回路と、メモリセルから読み出したデータ、もしくはメモリセルへの書き込みデータを一時的に保持する容量素子を有するデータ保持回路と、データ保持回路で保持しているデータの反転データをビット線に出力する反転データ出力回路とを有し、反転データ出力回路は、データ保持回路で保持しているデータの反転データの出力を制御する手段を有する構成とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、書き込みワード線に電気的に接続する容量素子またはノイズ除去回路を設けることで、駆動回路等からメモリセルに入力されうる制御信号とは異なる短パルスやノイズ等の信号を低減または除去することができる。これにより、メモリセルが有するトランジスタが瞬間的にオンすることでメモリセルに書き込まれたデータが消失してしまう誤動作を防ぐことが可能である。

(もっと読む)

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】半絶縁性単結晶ダイヤモンド基板の一方の面に、p−ダイヤモンド層からなるドリフト層を成膜し、該ドリフト層の上にp+ダイヤモンド層からなるコンタクト層を成膜する工程と、前記基板の他方の面に開口部をエッチングにより形成して、前記基板を構造保持材として前記ドリフト層の一部が露出した露出部を形成する工程と、前記露出部にカソード電極を設け、前記コンタクト層にアノード電極を設ける工程とにより、ダイヤモンド電子素子の積層構造を形成する。ドリフト層を基板上に直接成膜するので、欠陥密度の減少した素子を得ることができる。

(もっと読む)

半導体装置、パワーダイオード及び整流器

【課題】高耐圧、低逆方向飽和電流、高いオン電流などの電気特性を有する半導体装置を提供することである。なかでも、非線形素子より構成されるパワーダイオード及び整流器を提供することである。

【解決手段】第1の電極と、第1の電極を覆うゲート絶縁層と、ゲート絶縁層と接して且つ第1の電極と重畳する酸化物半導体層と、酸化物半導体層の端部を覆う一対の第2の電極と、一対の第2の電極及び酸化物半導体層を覆う絶縁層と、絶縁層に接して且つ一対の第2の電極の間に設けられる第3の電極と、を有し、一対の第2の電極は酸化物半導体層の端面に接する半導体装置である。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタを備える画像表示装置、薄膜トランジスタの製造方法、画像表示装置の製造方法

【課題】作製コストを低減させることが可能な、薄膜トランジスタ、薄膜トランジスタを備える画像表示装置、薄膜トランジスタ及び画像表示装置の製造方法を提供すること。

【解決手段】第一基板と、当該第一基板上に設けられたゲート電極と、前記第一基板及び前記ゲート電極上に設けられたゲート絶縁膜と、当該ゲート絶縁膜上に設けられた半導体層と、当該半導体層上に設けられた保護膜と、前記半導体層及び前記保護膜上に設けられたソース電極及びドレイン電極と、を備え、前記保護膜は、前記半導体層を設けた後に連続して設けられていることを特徴とする薄膜トランジスタとしたもの。

(もっと読む)

半導体装置及びその駆動方法

【課題】半導体装置における電界の集中を緩和する。

【解決手段】ゲート電極とドレイン電極を重畳させずに設け、且つ上面において、ゲート電極とドレイン電極の間には電界制御電極が設けられている。そして、ゲート電極と半導体層の間、及び電界制御電極と半導体層の間には、それぞれ絶縁層が設けられており、電界制御電極と半導体層の間に設けられた絶縁層は、ゲート電極と半導体層の間に設けられた絶縁層よりも厚い。さらには、この半導体装置を駆動させるに際して、電界制御電極の電位は、ソース電位以上であってゲート電位より低ければよく、例えば、電界制御電極とソース電位を接続させることでこのような構成を実現することができる。

(もっと読む)

半導体装置

【課題】メモリセルの保持データが多値化された場合であっても正確なデータを保持することが可能なメモリセルを有する半導体装置を供給すること。

【解決手段】半導体装置に、酸化物半導体によってチャネル領域が形成されるトランジスタのソース及びドレインの一方が電気的に接続されたノードにおいてデータの保持を行うメモリセルを設ける。なお、当該トランジスタのオフ電流(リーク電流)の値は、極めて低い。そのため、当該ノードの電位を所望の値に設定後、当該トランジスタをオフ状態とすることで当該電位を一定又はほぼ一定に維持することが可能である。これにより、当該メモリセルにおいて、正確なデータの保持が可能となる。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体性酸化物を用いた半導体装置は、可視光や紫外光を照射することで電気的特性が変化する。このような問題に鑑み、半導体性酸化物膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】亜鉛のように400〜700℃で加熱した際にガリウムよりも揮発しやすい材料を酸化ガリウムに添加したターゲットを用いて、スパッタリング方法で成膜したものを400〜700℃で加熱することにより、添加された材料を膜の表面近傍に偏析させ、かつ、その酸化物を結晶化させる。さらに、その上に半導体性酸化物膜を堆積し、熱処理することにより結晶化した酸化物の結晶構造を引き継いだ結晶を有する半導体性酸化物を形成する。

(もっと読む)

電子装置とその作製方法およびスパッタリングターゲット

【課題】絶縁性酸化物の量産性を高めこと、また、そのような絶縁性酸化物を用いた半導体装置に安定した電気的特性を付与すること、信頼性の高い半導体装置を作製する。

【解決手段】亜鉛のように400〜700℃で加熱した際にガリウムよりも揮発しやすい材料を酸化ガリウムに添加したターゲットを用いて、DCスパッタリング、パルスDCスパッタリング等の大きな基板に適用できる量産性の高いスパッタリング方法で成膜し、これを400〜700℃で加熱することにより、添加された材料を膜の表面近傍に偏析させる。膜のその他の部分は添加された材料の濃度が低下し、十分な絶縁性を呈するため、半導体装置のゲート絶縁物等に利用できる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の優れたトランジスタを作製する。

【解決手段】基板上に酸化物絶縁膜を形成し、該酸化物絶縁膜上に酸化物半導体膜を形成した後、酸化物半導体膜に含まれる水素を除去させつつ、酸化物絶縁膜に含まれる酸素の一部を脱離させる温度で加熱した後、該加熱された酸化物半導体膜を所定の形状にエッチングして島状の酸化物半導体膜を形成し、島状の酸化物半導体膜上に一対の電極を形成し、該一対の電極及び島状の酸化物半導膜上にゲート絶縁膜を形成し、該ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法

【課題】薄膜トランジスタを作製する際、従来のCVD法により形成される膜よりも高品

質の膜を形成すること、熱酸化法で形成される膜と同等又はそれ以上の品質の膜を基板に

影響を及ぼさない温度で形成することを目的とする。

【解決手段】ガラス基板、所定のパターンに形成された非晶質シリコンを含む半導体膜、

ゲート電極及び該ゲート電極から延びた配線、ゲート絶縁膜となる絶縁膜、保護膜の少な

くとも一つに対し、ガラス基板の温度を該ガラス基板の歪点より100℃以上低い温度と

し、低電子温度且つ高電子密度でプラズマ酸化又はプラズマ窒化をおこなう。

(もっと読む)

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、上下をゲート電極で挟んだ酸化物半導体を用いた薄膜トランジス

タで構成する。同一基板上に画素部及び駆動回路を設けることによって製造コストを低減

する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた半導体装置は、可視光や紫外光を照射することで電気的特性が変化する。このような問題に鑑み、酸化物半導体膜を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを課題の一とする。

【解決手段】酸化物絶縁層上に膜厚が1nm以上10nm以下の第1の酸化物半導体層を形成し、加熱処理により結晶化させ、第1の結晶性酸化物半導体層を形成し、その上に第1の結晶性酸化物半導体層よりも厚い第2の結晶性酸化物半導体層を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体装置

【課題】SOI構造の単結晶半導体層(SiGe層/歪みSi層/SiGe層)上のMISFETの提供

【解決手段】半導体基板1に選択的に設けられた第1のトレンチの下部側面及び底面に絶縁膜3が設けられ、側面絶縁膜3間の底面絶縁膜3上に空孔4が設けられ、空孔4及び側面絶縁膜3上には単結晶半導体層が設けられ、半導体層は絶縁膜2が埋め込まれた第2のトレンチにより、島状に絶縁分離され、歪みSi層6直上にはゲート酸化膜11を介してゲート電極12が設けられ、半導体層には、ゲート電極12に自己整合してn型ソースドレイン領域(8、9)が、ゲート電極12の側壁のサイドウォール13に自己整合して、n+型ソースドレイン領域(7、10)がそれぞれ設けられ、ゲート電極12(配線図示せず)及びn+型ソースドレイン領域にはバリアメタル16を有する導電プラグ17を介してバリアメタル19を有する配線20が接続されているMISFET。

(もっと読む)

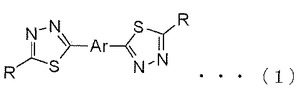

新規液晶性化合物および該化合物を含有する有機半導体素子

【課題】有機半導体材料として有用な、適度なホールおよび電子輸送特性を有する、可視光透過性の液晶性化合物を提供する。

【解決手段】式(1)で表される化合物による。

[式(1)において、Rは独立して、水素または炭素数1〜24のアルキルであり、このアルキルにおける任意の−CH2−は−O−、−S−、−CO−または−SiH2−で置き換えられてもよく、任意の−(CH2)2−は−CH=CH−または−C≡C−で置き換えられてもよく、任意の水素はハロゲンで置き換えられていてもよく;Arはナフチレン、アントリレン、フェナントリレンまたはすべての水素がハロゲンで置き換えられたフェニレンであり、ナフチレン、アントリレンおよびフェナントリレンにおける任意の水素はハロゲンで置き換えられてもよい。]

(もっと読む)

ジチエノベンゾジチオフェン誘導体からなる有機半導体材料前駆体、インク、絶縁部材、電荷輸送性部材、有機電子デバイス

【課題】印刷等の簡便なプロセスで成膜できる溶解性を有し、成膜後は簡単な処理により不溶化し、後工程でのダメージを軽減できると共に、不溶化処理後は良好な半導体特性を示すジチエノベンゾジチオフェン誘導体からなる有機半導体材料前駆体、該前駆体を含有するインク、該インクを用いて作製された絶縁部材、電荷輸送性部材、有機電子デバイスの提供。

【解決手段】下記一般式(I)で表されるジチエノベンゾジチオフェン誘導体からなることを特徴とする有機半導体材料前駆体。

〔上記式中、X及びYは、外部刺激によりXとYが結合してX−Yとして一般式(I)の化合物から脱離する基を表し、R1及びR2はそれぞれ独立に、アルキル基、又はアリール基を表し、R3〜R10はそれぞれ独立に、水素、アルキル基、アルコキシ基、アルキルチオ基、又はアリール基を表す。〕

(もっと読む)

101 - 120 / 618

[ Back to top ]