Fターム[5F110HK08]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961)

Fターム[5F110HK08]の下位に属するFターム

Fターム[5F110HK08]に分類される特許

81 - 100 / 618

有機トランジスタの製造方法

【課題】電界効果移動度が高い有機トランジスタを製造する方法を提供すること。

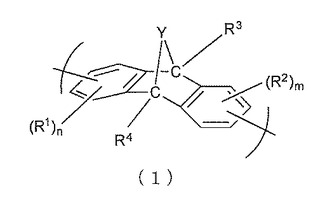

【解決手段】式

[式中、R1及びR2は、それぞれ独立に、置換基を表す。R3及びR4は、それぞれ独立に、水素原子又は置換基を表す。n及びmは、それぞれ独立に、0〜3の整数を表す。Yは、2価の基を表す。R1が複数個ある場合、及びR2が複数個ある場合、それらは同一でも相異なってもよい。]で表される構造単位を含む化合物を含有する有機膜を形成する工程と、Yで表される2価の基の少なくとも一部を脱離させて、有機半導体層を製造する工程とを、有する、ゲート電極、ソース電極、ドレイン電極及び有機半導体層を有する有機トランジスタの製造方法。

(もっと読む)

有機薄膜、有機薄膜の製造方法、電界効果トランジスタ、有機発光素子、太陽電池、表示装置用アレイ及び表示装置

【課題】有機分子の配向性が制御されて十分な機能を有する有機薄膜及びその製造方法、並びに該有機薄膜を用いた有機電子デバイス及び表示装置の提供。

【解決手段】基材60上に第一の有機分子61を化学結合させて立設し、点在させ、第二の有機分子62を導入し、第一の有機分子61に対して第二の有機分子62を配列させて、有機薄膜6を形成する。第一の有機分子61及び第二の有機分子62が有機半導体分子である、かかる有機薄膜を、有機半導体層として設け、電界効果トランジスタとする。

(もっと読む)

チャネルエッチ型薄膜トランジスタとその製造方法

【課題】半導体層の膜厚均一性を向上させたチャネルエッチ型TFTとその製造方法を提供する。

【解決手段】酸化物半導体からなるチャネル層4を形成した後、該チャネル層4の上にIn、Zn、Gaを含む酸化物からなり、上記酸化物半導体よりもエッチングレートが速く、抵抗率が3.38×107Ωcm以下である犠牲層5を形成し、その上にソース電極6及びドレイン電極7を形成して、該ソース電極6とドレイン電極7の間に露出した犠牲層5をウェットエッチング除去することにより、半導体層膜厚の均一性を向上させ、TFT特性とその均一性と、をより向上させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して、歪みSi層6を挟み、左右にSiGe層5を有する構造からなる第1のエピタキシャル半導体層及び歪みGe層8を挟み、左右にSiGe層7を有する構造からなる第2のエピタキシャル半導体層が島状に絶縁分離されて設けられ、歪みSi層6には概略チャネル領域が形成され、SiGe層5には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成された包囲型ゲート電極構造のNチャネルのMISFETと、歪みGe層8には概略チャネル領域が形成され、SiGe層7には概略高濃度のソースドレイン領域(14、15)が形成された包囲型ゲート電極構造のPチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】本発明は、安定した特性を示す金属酸化物半導体を用いた薄膜トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明の薄膜トランジスタは、ゲート電極1と、ゲート電極1上に設けられたゲート絶縁膜2と、ゲート絶縁膜2上に設けられたドレイン電極3B,4Bと、ゲート絶縁膜2上にドレイン電極3B,4Bと隣接して設けられ、金属酸化物半導体で構成されたチャネル層5とを備え、ドレイン電極3B,4Bは、ゲート電極1への電圧印加によりチャネル層5に形成される反転層101と接触すべくゲート絶縁膜2上に設けられ、チャネル層5を構成する金属酸化物半導体よりも酸化物生成自由エネルギーが若干小さい金属酸化物半導体で構成された第1ドレイン電極3と、第1ドレイン電極3上に設けられ、金属で構成された第2ドレイン電極4とを備える。

(もっと読む)

マイクロローディング効果を軽減するためのSiGe埋め込みダミーパターンを備えたSiGe装置

【課題】SiGe装置を取り囲んで、SiGeのエピタキシャル成長時にマイクロローディング効果を軽減できるように特別に設計されたSiGe埋め込みダミーパターンを備えた改良されたSiGe装置を提供する。

【解決手段】マイクロローディング効果を軽減するためのダミーパターンを備えた半導体装置は、内部領域200と外部領域400の間に中間環状領域300が設けられた半導体基板1と、基板上、内部領域200に設けられたSiGe装置100と、基板上、中間環状領域300に設けられた複数のダミーパターン20とを含む。複数のダミーパターン20のうち少なくとも1つがSiGeを含む。

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

有機素子材料

【課題】高温での処理を行わないで架橋させることが可能な有機素子材料を提供すること。

【解決手段】フッ素原子を含む基を有する繰り返し単位と、光二量化反応性基を有する繰り返し単位とを有する高分子化合物を含む有機薄膜トランジスタ絶縁層材料。フッ素原子を含む基の好ましい例は、水素原子がフッ素で置換されたアリール基、水素原子がフッ素で置換されたアルキルアリール基、特に水素原子がフッ素で置換されたフェニル基、水素原子がフッ素で置換されたアルキルフェニル基である。光二量化反応性基の好ましい例は、2位の水素原子がアリール基で置換されたビニル基、2位の水素原子がアリールカルボニル基で置換されたビニル基である。

(もっと読む)

半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

電荷注入特性が高い有機薄膜トランジスタ

【課題】トランジスタ特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタ、及びその製造方法を提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、該第1導電層は、塗布法を用いて形成されたものであり、該第1導電層の端部は該第2導電層の端部と比較して電極ブロックの内側に位置している有機薄膜トランジスタ。

(もっと読む)

半導体装置

【課題】表示装置に用いられるトランジスタは、より高耐圧なものが求められており、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図る。

【解決手段】チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられたトランジスタを有する半導体装置である。バッファ層は、チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にあって、特にドレイン端近傍の電界を緩和して、トランジスタの耐圧を向上させるように設けられる。

(もっと読む)

半導体装置の作製方法及び表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して、信頼性の高い半導体

装置を作製する方法を提供する。

【解決手段】基板上に導電層を形成し、該導電層上に光透過層を形成し、該光透過層上か

らフェムト秒レーザを照射して、該導電層及び該光透過層を選択的に除去する工程を有す

る。なお、該導電層の端部は、該光透過層の端部より内側に配置されるように該導電層及

び該光透過層を除去されていてもよい。また、フェムト秒レーザを照射する前に、該光透

過層表面に撥液処理を行ってもよい。

(もっと読む)

積層構造のソース・ドレイン電極を有する有機薄膜トランジスタ

【課題】柔軟性及び耐久性に優れ、素子特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタを提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、第1導電層は、酸化タングステン、酸化銀、酸化銅、酸化亜鉛、銀塩、銀及び銅からなる群から選ばれる1種以上の材料を含み、該第2導電層は、Ag、Al、Au、Cd、Co、Cr、Cu、Fe、Mg、Mo、Ni、Pb、Pd、Pt、Sn、Ta、Ti、V、W、Zn、Zr、及びこれらの金属のいずれかを含む合金からなる群から選ばれる1種以上の材料を含む、有機薄膜トランジスタ。

(もっと読む)

フェノール性水酸基含有芳香族ポリアミド樹脂を含有する絶縁層を有する有機半導体素子並びにその製造方法

【課題】本発明のフェノール性水酸基含有芳香族ポリアミド樹脂を含有する有機絶縁層を用いた有機半導体素子は、トランジスタ特性及び耐湿熱性等の耐久性に優れており、実用性の高い有機半導体素子を提供する。

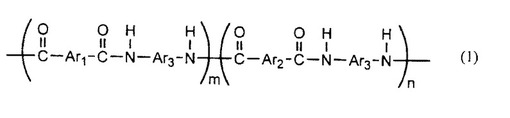

【解決手段】下記式(1)で表されるフェノール性水酸基含有芳香族ポリアミド樹脂を含有する有機絶縁層を有する有機半導体素子。

(式(1)中、各構造単位の平均重合度m及びnはm+n=2〜200であり、Ar1及びAr3は2価の芳香族基、Ar2はフェノール性水酸基を有する2価の芳香族基を表す。)

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置を提案することを課題とする。

【解決手段】基板上に形成されたゲート電極と、ゲート電極上に形成された酸素過剰のSiOX膜と、SiOX膜上に形成された酸化物半導体膜と、を有する半導体装置。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワーMISFETを提供する。

【解決手段】半導体層101を挟んでゲート電極102aとソース電極103a、ドレイン電極103bを形成し、半導体層のうちゲート電極102aとドレイン電極103bとの間にこれらが重ならない領域を設ける。この領域の長さを0.5μm乃至5μmとする。このようなパワーMISFETのドレイン電極とソース電極の間に100V以上の電源と負荷を直列に接続し、ゲート電極102aに制御用の信号を入力して使用する。

(もっと読む)

81 - 100 / 618

[ Back to top ]