Fターム[5F110HK08]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961)

Fターム[5F110HK08]の下位に属するFターム

Fターム[5F110HK08]に分類される特許

121 - 140 / 618

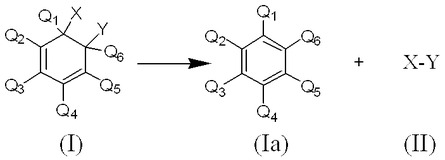

置換基脱離化合物とそれから得られる有機半導体材料、それを用いた有機電子デバイス、有機薄膜トランジスタおよびディスプレイ装置

【課題】高い有機溶媒溶解性を有し、低いエネルギー付与で有機半導体化合物に変換可能な置換基脱離化合物と、これを用いた有機電子デバイスを提供する。

【解決手段】一般式(I)で表され、エネルギー付与により一般式(Ia)で表される化合物と一般式(II)で表される化合物に変換可能なことを特徴とする置換基脱離化合物。

[式(I)、(Ia)、(II)中、XおよびYは水素原子もしくは脱離性置換基を表し、該XおよびYのうち一方は脱離性置換基であり、他方は水素原子である。Q1乃至Q6は水素原子、ハロゲン原子または、一価の有機基である。]

(もっと読む)

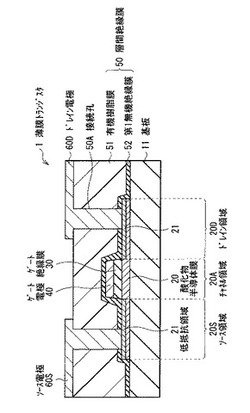

薄膜トランジスタおよび表示装置

【課題】層間絶縁膜に起因する不良を抑え、セルフアライン構造の薄膜トランジスタの信頼性を向上させることが可能な薄膜トランジスタおよびこれを備えた表示装置を提供する。

【解決手段】酸化物半導体膜20に接して、有機樹脂膜51を含む層間絶縁膜50を設ける。層間絶縁膜50の厚みを厚くして、ゲート絶縁膜30およびゲート電極40の段差を確実に被覆し、ソース電極60Sおよびドレイン電極60Dの断線あるいは短絡など、層間絶縁膜50に起因する不良を抑える。層間絶縁膜50は、有機樹脂膜51および第1無機絶縁膜52の積層構造を有していることが好ましい。酸素や水分などに対するバリア性の高い第1無機絶縁膜51により、酸化物半導体膜20への水分の混入や拡散を抑え、薄膜トランジスタ1の信頼性を向上させる。

(もっと読む)

非晶質酸化物、及び電界効果型トランジスタ

【課題】TFTの活性層等に適用できる新規な非晶質酸化物を提供する。

【解決手段】非晶質酸化物が所定の材料を含み、電子キャリア濃度が1018/cm3未満であることを特徴とする。

(もっと読む)

非晶質酸化物、及び電界効果型トランジスタ

【課題】TFTの活性層等に適用できる新規な非晶質酸化物を提供する。

【解決手段】非晶質酸化物が層厚方向に組成が変化する薄膜からなり、電子キャリア濃度が1018/cm3未満であることを特徴とする。

(もっと読む)

半導体構造体及びその製造方法

【課題】 埋め込み型DRAM構造のための半導体構造体及びその製造方法を提供する。

【解決手段】 ノード誘電体及び深いトレンチを充填する導電性トレンチ充填領域がセミコンダクター・オン・インシュレータ(SOI)層の上面とほぼ同一面となる深さにまで窪まされる。浅いトレンチ分離部が深いトレンチの上部の一方の側に形成され、一方深いトレンチの上部の他方の側は、導電性充填領域の半導体材料の露出された表面となる。選択的エピタキシャル成長プロセスが、レイズド・ソース領域及びレイズド・ストラップ領域を付着するために行われる。レイズド・ソース領域は、SOI層内のプレーナ・ソース領域上に直接形成され、そしてレイズド・ストラップ領域は、導電性充填領域上に直接形成される。レイズド・ストラップ領域は、プレーナ・ソース領域及び導電性充填領域の間の導電性通路を与えるためにレイズド・ソース領域に接触する。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置

を提供することを課題の一とする。また、同一基板上に複数種類の薄膜トランジスタの構

造を作製して複数種類の回路を構成し、増加する工程数が少ない半導体装置の作製方法を

提供することを課題の一とする。

【解決手段】絶縁表面上に金属薄膜を成膜した後、酸化物半導体層を積層し、その後、加

熱処理などの酸化処理を行うことで金属薄膜の一部または全部を酸化させる。また、論理

回路などの高速動作を優先する回路と、マトリクス回路とで異なる構造の薄膜トランジス

タを配置する。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI構造の縦型のMISFETの提供

【解決手段】Si基板1上に、一部に空孔4を有する絶縁膜2が設けられ、空孔4上及び絶縁膜2の一部上に横方向半導体層6が設けられ、半導体層6の側面の一部に導電膜3が接して設けられ、絶縁膜2により素子分離されている。半導体層6上の、空孔4直上部に縦方向半導体層7が設けられ、半導体層7の上部にドレイン領域(10,9)が設けられ、離間し、相対して下部にソース領域8が設けられ、ソース領域8は延在して、半導体層6全体に設けられている。半導体層7の全側面には、ゲート酸化膜11を介してゲート電極12が設けられ、ドレイン領域10、ゲート電極11及び導電膜3を介したソース領域8には、バリアメタル18を有する導電プラグ19を介してバリアメタル21を有する配線22が接続されている縦型のMISFET。

(もっと読む)

半導体装置

【課題】電気特性が良好な半導体装置を提供する。または、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】逆スタガ型の薄膜トランジスタにおいて、ゲート絶縁膜と、ソース配線及びドレイン配線として機能する配線との間に、微結晶シリコン膜及び一対のシリコンカーバイド膜を有し、微結晶シリコン膜はゲート絶縁膜側に形成され、一対のシリコンカーバイド膜は配線側に形成される。電気特性が良好な半導体装置を、生産性高く作製することができる。

(もっと読む)

電界効果トランジスタ、およびその製造方法

【課題】高い移動度、低いオン抵抗を備えたノーマリオフ型の電界効果トランジスタを提供する。

【解決手段】III族窒化物系化合物半導体からなるチャネル層104と、前記チャネル層上に形成されたAlInGaNからなる界面層106と、前記界面層上に形成され、前記界面層に達するリセス部を備えたIII族窒化物系化合物半導体からなる電子供給層108と、前記リセス部を挟んで、前記電子供給層108上に形成されたソース電極110およびドレイン電極112と、前記リセス部の内表面に形成された絶縁膜120と、前記絶縁膜上に形成されたゲート電極114とを備える。

(もっと読む)

液晶表示装置及び電子機器

【課題】TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおかつコストを抑えることができる液晶表示装置の提案を課題とする。

【解決手段】画素部に液晶素子と、液晶素子に印加される電圧を制御するTFTとを有する画素が設けられており、駆動回路が有するTFTと、液晶素子に印加される電圧を制御するTFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を間に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成された一対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純物が添加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを特徴とする液晶表示装置。

(もっと読む)

薄膜トランジスタ、薄膜集積回路装置及びそれらの製造方法

【課題】低価格化の要請に応えることができ、半導体膜として用いた酸化物半導体膜にダメージを与えない手段を含む薄膜トランジスタ及びその製造方法、並びにその薄膜トランジスタを含む集積回路及びその製造方法を提供する。

【解決手段】基材1上に酸化物半導体膜3をパターン形成する工程と、活性化処理により酸化物半導体膜3にソース・ドレイン接続領域3s,3dを形成する工程と、ソース・ドレイン接続領域3s,3dが形成された酸化物半導体膜3を覆うように、塗布法、反応性スパッタリング法又はパルスプラズマCVD法でゲート絶縁膜4を形成する工程と、ゲート絶縁膜4にコンタクトホール5を開けてソース・ドレイン電極6を前記ソース・ドレイン接続領域3s,3dに接続するとともに酸化物半導体膜3上にゲート電極7を形成する工程と、を少なくとも有する製造方法により上記課題を解決する。

(もっと読む)

半導体装置の製造方法

【課題】半導体層上に良好な結晶性を有するエピタキシャル結晶を成長させることができる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板10上に絶縁膜を介して形成された前駆体膜から所定の方向に延びるナノワイヤ14を形成し、形成したナノワイヤ14の両側面及び上面にゲート絶縁膜を介してナノワイヤ14の所定の方向と交差するようにゲート電極18を形成し、形成したゲート電極18の両側面にゲート側壁22を形成し、ゲート側壁22の形成後に露出するナノワイヤ14の表面にエピタキシャル結晶を成長させてエピタキシャル層24を形成し、エピタキシャル層24を形成した後、ナノワイヤ14に不純物を導入してエクステンション領域を形成する、ことを含む。

(もっと読む)

強誘電性電界効果トランジスタデバイス

発光装置

【課題】TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおかつ

コストを抑えることができる発光装置の提案を課題とする。

【解決手段】画素部に発光素子と、発光素子への電流の供給を制御するTFTとを有する

画素が設けられており、駆動回路が有するTFTと、発光素子への電流の供給を制御する

TFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を間

に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成された一

対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純物が添

加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを特徴と

する発光装置。

(もっと読む)

電界効果トランジスタ(FET)およびそれを形成する方法

薄膜トランジスタ、発光装置及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の向上を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおける半導体膜5b、6bを、n型の結晶性シリコンを含む下層部51、61とp型の結晶性シリコンを含む上層部52、62との二層構造にすることによれば、薄膜トランジスタ5、6の半導体膜5b、6bにおけるオン電流の経路がインキュベーション層5c、6cにあたらないように電流経路を上層部52、62寄りにシフトさせることができ、オン電流の経路を半導体膜5b、6bにおける結晶化領域Rにすることによって、薄膜トランジスタ5、6のオン電流の向上を図ることができる。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるチャネル保護膜6d(5d)に鋭角なエッジ部6p(5p)を設けて、そのエッジ部6d(5d)でソース電極6i(5i)と不純物半導体膜6g(5g)の積層体を破断するようにして、その積層体がチャネル保護膜6d(5d)の上面に重ならない構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制することができ、チャネルの乱れを抑えることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

半導体装置とその製造方法、及び半導体装置の評価方法

【課題】チャネルに応力が印加されるMOSトランジスタの特性のばらつきを防ぐことができる半導体装置の製造方法を提供すること。

【解決手段】半導体基板10の上にゲート絶縁膜を形成する工程と、ゲート絶縁膜の上にゲート電極14cを形成する工程と、ゲート電極14cの側面にサイドウォール15a、15bを形成する工程と、サイドウォール15a、15bを形成した後に、有機アルカリ溶液又はTMAHをエッチング液として用いて、ゲート電極14cの横の半導体基板10に穴10a、10bを形成する工程と、穴10a、10bにソース/ドレイン材料層18a、18bを形成する工程とを有する。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに表示装置

【課題】 ソース・ドレイン電極と半導体膜との接触抵抗を低減し、移動度特性を向上した薄膜トランジスタを提供する。さらに、それを用いた高性能の表示装置を提供する。

【解決手段】 板上に形成されたゲート電極と、前記ゲート電極を覆うようにして前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体膜と、少なくとも各々の一部が前記半導体膜上に形成され、ソース電極及びドレイン電極として機能する一対の電極と、を具備する薄膜トランジスタであって、前記半導体膜は、GeあるいはSi及びGeを含有し、前記一対の電極の各々は、ボロンあるいはV族元素を含有する金属膜で形成され、前記一対の電極の各々と前記半導体膜との間に、ジャーマノシリサイドあるいは金属−Ge間化合物が形成されている。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタのオン電流の安定を図る。

【解決手段】ELパネル1において、駆動素子として用いるスイッチトランジスタ5、駆動トランジスタ6などの薄膜トランジスタにおけるソース電極6i(5i)と不純物半導体膜6g(5g)の積層体の一部が、チャネル保護膜6d(5d)における膜厚の厚い一端側に重なる構造にすることで、チャネルとなる領域を覆うチャネル保護膜6d(5d)に作用するバックゲート効果を抑制することができ、チャネルの乱れを抑えることができるので、薄膜トランジスタ6(5)のオン電流(Id)を従来のものより増加させ、好適な値に安定させることを可能にした。

(もっと読む)

121 - 140 / 618

[ Back to top ]