Fターム[5F110HK08]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961)

Fターム[5F110HK08]の下位に属するFターム

Fターム[5F110HK08]に分類される特許

21 - 40 / 618

π電子共役系化合物前駆体を用いた電子デバイス用インク組成物ならびにその用途

【課題】前駆体膜を変換して得られた半導体膜の導電率の向上。その有機膜を電極と有機半導体の間に配置することで、電極と半導体層の接触抵抗を低減すること。その結果として、接触抵抗が改善された高性能の電気特性を得ることが可能な電子デバイス用インク組成物ならびにそれを用いた電子デバイス、電界効果トランジスタ、およびその製造方法を提供すること。

【解決手段】電子デバイス用インク組成物であって、少なくともπ電子共役系化合物前駆体と、前記π電子共役系化合物のドーパントと、前記π電子共役系化合物前駆体とドーパントを溶解させる溶媒を含有することを特徴とするインク組成物。

(もっと読む)

液晶表示装置

【課題】TFTの工程を複雑化させることなくシステムオンパネル化を実現し、なおかつコストを抑えることができる液晶表示装置の提案を課題とする。

【解決手段】画素部に液晶素子と、液晶素子に印加される電圧を制御するTFTとを有する画素が設けられており、駆動回路が有するTFTと、液晶素子に印加される電圧を制御するTFTとは、ゲート電極とゲート電極上に形成されたゲート絶縁膜と、ゲート絶縁膜を間に挟んでゲート電極と重なっている第1の半導体膜と、第1の半導体膜上に形成された一対の第2の半導体膜とを有し、一対の第2の半導体膜には一導電型を付与する不純物が添加されており、第1の半導体膜はセミアモルファス半導体で形成されていることを特徴とする液晶表示装置。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かす、適切な構成を備えた保護回路等を提供する。

【解決手段】ゲート電極101を被覆するゲート絶縁層102と、ゲート絶縁層102上においてゲート電極101と重畳する第1酸化物半導体層103と、第1酸化物半導体層103上においてゲート電極と端部が重畳し、導電層105aと第2酸化物半導体層104aが積層された一対の第1配線層38及び第2配線層39とを有する非線形素子170aを用いて保護回路を構成する。ゲート絶縁層102上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子170aの特性を向上させることができる。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能および製造安定性を向上させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、第1の面および第2の面を有する有機半導体部と、第1の面に隣接されたソース電極部と、第2の面に隣接されたドレイン電極部とを備える。ソース電極部およびドレイン電極部のうちの少なくとも一方は、有機半導体部よりも高導電性の有機半導体材料を含む高導電性電極部である。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体装置の作製方法

【課題】薄膜トランジスタのしきい値電圧を制御するため、薄膜トランジスタのチャネル形成領域の上下にゲート絶縁膜を介してゲート電極を設けた際に、プロセス数の増加を招くことなく、電気特性の優れた薄膜トランジスタを備えた半導体装置を得る。

【解決手段】酸化物半導体層131の上方に設ける第2のゲート電極133を形成するとき、酸化物半導体層131のパターニングと同時に形成することで、第2のゲート電極133の作製に要するプロセス数の増加を削減する。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

酸化物半導体膜の成膜方法、半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタと比較して信頼性が劣る場合があった。そこで、信頼性が高い酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】酸化物半導体膜に含まれる水素、窒素および炭素などの不純物は酸化物半導体膜の半導体特性を低下させる要因となる。例えば、酸化物半導体膜に含まれる水素および窒素は、酸化物半導体膜を用いたトランジスタのしきい値電圧をマイナス方向へシフトさせてしまう要因となる。また、酸化物半導体膜に含まれる窒素、炭素および希ガスは、酸化物半導体膜中に結晶領域が生成されることを阻害する。そこで、酸化物半導体膜の不純物濃度を低減することで、高い信頼性を有するトランジスタを作製する。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを

目的の一つとする。

【解決手段】酸化物半導体層に対して、窒素、または希ガス(アルゴン、ヘリウムなど)

の不活性気体雰囲気下、或いは減圧下で脱水化、又は脱水素化処理のための加熱処理を行

い、酸素、酸素及び窒素、又は大気(好ましくは露点−40℃以下、より好ましくは−5

0℃以下)雰囲気下で加酸化処理のための冷却工程を行うことで高純度化及びI型化した

酸化物半導体層を形成する。該酸化物半導体層を含む薄膜トランジスタを有する半導体装

置を作製する。

(もっと読む)

代用ソース/ドレインフィンFET加工

【課題】finFETにおける高集積化可能な、高濃度ソースドレインの形成方法の提供。

【解決手段】ソース領域、ドレイン領域およびソース領域とドレイン領域の間のチャネル領域を有するフィンを形成する。チャネル領域にダイレクトコンタクトする絶縁層と、絶縁層にダイレクトコンタクトする伝導性のゲート物質とを有するゲートスタックを形成する。チャネル領域を残したまま、ソース領域およびドレイン領域をエッチング除去する。ソース領域およびドレイン領域に隣接したチャネル領域の両側にソースエピタキシー領域およびドレインエピタキシー領域を形成する。ソースエピタキシー領域およびドレインエピタキシー領域は、エピタキシャル半導体を成長させながら、その場ドープされる。

(もっと読む)

表示装置

【課題】ゲート絶縁層として要求される耐圧や容量を確保しつつ、外光反射率によるコントラストの劣化を抑えやすくした表示装置を提供する。

【解決手段】透明基板GAと、透明基板GAの上側に形成されるゲート電極GTと、ゲート電極GTの上側に形成される微結晶半導体層MSと、ゲート電極GTと微結晶半導体層MSの間に形成されて、微結晶半導体層MSの外方に延在するゲート絶縁層GIと、ゲート絶縁層GIの微結晶半導体層MSの外方に延在する部分の上面に接して、窒化ケイ素で形成される第2の窒化ケイ素層NI2と、を有し、ゲート絶縁層GIは、第1の窒化ケイ素層NI1と、第1の窒化ケイ素層NI1の上側に形成されて微結晶半導体層MSに接する酸化ケイ素層OIと、を含み、ゲート絶縁層GIは、微結晶半導体層MSの下側の部分よりも第2の窒化ケイ素層NI2の下面に接する部分で薄く形成される、ことを特徴とする表示装置。

(もっと読む)

薄膜トランジスタ及びそれを用いた電子デバイス

【課題】優れた電気特性、大気安定性を有した薄膜トランジスタ及びそれを用いた電子デバイスをウェットプロセスにて作製するための、π電子共役系化合物前駆体、及びトランジスタ構造を提供する。

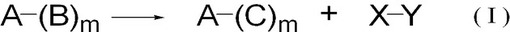

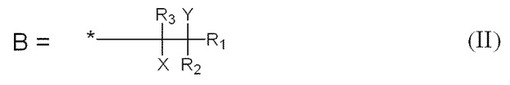

【解決手段】少なくとも下記一般式(I)で示される工程により得られる有機膜を用いたトップゲート型薄膜トランジスタ。

(もっと読む)

(もっと読む)

薄膜トランジスタ及びそれを用いた電子デバイス

【課題】特定構造のπ電子共役化合物前駆体を含む薄膜中の該前駆体のπ電子共役化合物への変換が、基板の耐熱温度に制限されることなく、且つ大気下で進行する、有機膜の製造方法。

【解決手段】π電子共役化合物前駆体A−(B)mを含む薄膜中の該前駆体A−(B)mが、活性エネルギー線の照射により、π電子共役系化合物A−(C)mと脱離性化合物X−Yに変換される。A−(B)m→A−(C)m+X−Y

(Aはπ電子共役系置換基、Bは溶媒可溶性置換基、mは自然数である。)

(もっと読む)

半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを

課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を

用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導

体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時

に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

電子デバイス及び半導体装置の製造方法

【課題】簡素な装置で、短時間にて形成することができ、しかも、電極と能動層との間のコンタクト抵抗の低減を確実に図ることができる電荷注入層を備えた電子デバイスを提供する。

【解決手段】電子デバイスは、第1電極15、第1電極と離間して設けられた第2電極15、及び、第1電極15の上から第2電極15の上に亙り設けられた、有機半導体材料から成る能動層14を少なくとも備えており、第1電極15と能動層14との間、及び、第2電極15と能動層14との間には、電荷注入層16が形成されており、電荷注入層16は、酸化されることで電気伝導度の値が増加した有機材料から成る。

(もっと読む)

半導体装置

【課題】半導体集積回路における消費電力を低減する。また、半導体集積回路における動作の遅延を低減する。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、酸化物半導体を用いた逆スタガ型薄膜トランジスタで構成する。

同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置およびその作製方法

【課題】同一基板上に酸化物半導体を用いたオフセットトランジスタとオフセットでないトランジスタを形成する。

【解決手段】酸化物半導体層202とゲート絶縁物203とゲート配線となる第1層配線204a、第1層配線204bを形成する。その後、オフセットトランジスタをレジスト206で覆い、酸化物半導体層に不純物を導入し、N型酸化物半導体領域207を形成する。その後、第2層配線209a、第2層配線209b、第2層配線209cを形成する。以上の工程により、オフセットトランジスタとそうでないトランジスタ(アラインドトランジスタ等)を形成することができる。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

21 - 40 / 618

[ Back to top ]