Fターム[5F110HK17]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 材料の特性が規定 (425)

Fターム[5F110HK17]に分類される特許

101 - 120 / 425

半導体装置

【課題】表示装置に用いられるトランジスタは、より高耐圧なものが求められており、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図る。

【解決手段】チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられたトランジスタを有する半導体装置である。バッファ層は、チャネル形成領域を形成する半導体層とソース電極層及びドレイン電極層との間にあって、特にドレイン端近傍の電界を緩和して、トランジスタの耐圧を向上させるように設けられる。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】SRAMは高速で省電力なメモリであるが、携帯機器等で使用するにはさらなる省電力化が求められる。

【解決手段】オフ抵抗が極めて高いトランジスタを書き込みトランジスタとし、書き込みトランジスタのドレインを書き込みビット線に、ソースをCMOSインバータの入力に接続し、読み出しトランジスタのドレインを読み出しビット線に、ソースをCMOSインバータの出力に接続したメモリセルを用いる。書き込みトランジスタのソースにはキャパシタを意図的に設けてもよいが、CMOSインバータのゲート容量あるいはCMOSインバータの正極や負極との間の寄生容量等を用いることもできる。データの保持はこれらのキャパシタに蓄積された電荷によっておこなえるため、CMOSインバータの電源間の電位差を0とできる。このため、CMOSインバータの正負極間を流れるリーク電流がなくなり、消費電力を低減できる。

(もっと読む)

電荷注入特性が高い有機薄膜トランジスタ

【課題】トランジスタ特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタ、及びその製造方法を提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、該第1導電層は、塗布法を用いて形成されたものであり、該第1導電層の端部は該第2導電層の端部と比較して電極ブロックの内側に位置している有機薄膜トランジスタ。

(もっと読む)

表示装置用金属配線膜

【課題】Si半導体層および/または透明導電膜との間のバリアメタル層を省略しても、低抵抗のオーミック特性を有する電気的接触を確保でき、更に十分な耐熱性を有する表示装置用金属配線膜を提供する。

【解決手段】Moを20原子%以上含有しており、且つ、Si、Nd、Ni、Mn、Mg、Fe、及びZnよりなる群から選択される少なくとも一種を5原子%以上含有しているAl合金膜53と、純CuまたはCu合金膜28,29とからなる積層膜であって、前記Al合金膜が、半導体層33と直接接続していると共に、前記CuまたはCu合金膜が透明導電膜55と直接接続している表示装置用金属配線膜。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

微結晶シリコン膜の作製方法、半導体装置の作製方法

【課題】高い膜密度を保ちつつ結晶性を高くした微結晶シリコン膜の作製方法を提供する。

【解決手段】本発明の微結晶シリコン膜の作製方法は、絶縁膜55上に、第1の条件により混相粒57aを有する第1の微結晶シリコン膜57をプラズマCVD法で形成し、その上に、第2の条件により第2の微結晶シリコン膜59をプラズマCVD法で形成する。第1の条件は、処理室内に供給する原料ガスとしてシリコンを含む堆積性気体と水素が含まれたガスを用い、処理室内の圧力を67Pa以上1333Pa以下とする条件であり、第1の条件における原料ガスの供給は、堆積性気体の流量に対する水素の流量を50倍以上1000倍以下にして堆積性気体を希釈したガスの供給と、当該ガスの堆積性気体の流量より低く、且つ絶縁膜上へのシリコンの堆積より絶縁膜上に堆積したシリコンのエッチングが優位となる堆積性気体の流量にしたガスの供給を交互に行うものである。

(もっと読む)

薄膜トランジスタ基板およびそれの製造方法

【課題】薄膜トランジスタ基板およびこれの製造方法を開示する。

【解決手段】本発明の薄膜トランジスタ基板は、基板上に形成されたゲート電極、前記ゲート電極上に前記ゲート電極と重なるように形成され、多結晶シリコンを含むアクティブ層、前記アクティブ層上に前記ゲート電極を中心に両側に分離して形成された第1オーミックコンタクト層、前記第1オーミックコンタクト層上に形成された第2オーミックコンタクト層および前記第2オーミックコンタクト層上に形成されたソース電極およびドレーン電極を含む。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

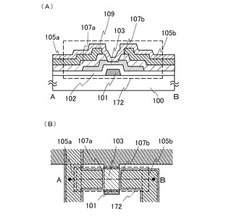

【課題】酸化物半導体を用いたパワーMISFETを提供する。

【解決手段】半導体層101を挟んでゲート電極102aとソース電極103a、ドレイン電極103bを形成し、半導体層のうちゲート電極102aとドレイン電極103bとの間にこれらが重ならない領域を設ける。この領域の長さを0.5μm乃至5μmとする。このようなパワーMISFETのドレイン電極とソース電極の間に100V以上の電源と負荷を直列に接続し、ゲート電極102aに制御用の信号を入力して使用する。

(もっと読む)

半導体装置、発光装置、およびその作製方法

【課題】酸化物半導体を用いて信頼性の優れた半導体装置を提供することを課題の一とする。又は、酸化物半導体を用いて信頼性の優れた発光装置を提供することを課題の一とする。

【解決手段】酸化物半導体を用いたトランジスタのソース電極層又はドレイン電極層に接続された第1の電極と、第1の電極に重畳する第2の電極の間に発光物質を含む有機層を備えた半導体装置において、第2の電極から、水素原子を含む不純物(例えば水分)を還元して水素イオン、又は水素分子を発する活性な導電材料を排除すればよい。特に、水と反応して水素イオン、又は水素分子を発生し難い不活性な導電材料を用いて、酸化物半導体を有する半導体装置を構成すればよい。具体的には、酸化還元電位が標準水素電極に比べて大きい金属、酸化還元電位が標準水素電極に比べて大きい金属同士の合金、乃至酸化還元電位が標準水素電極に比べて大きい導電性の金属酸化物を用いて半導体装置を構成すればよい。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタ

【課題】更なるスイッチング動作の高速化を図ることが可能な構造の横型IGBTを提供する。

【解決手段】コレクタ電極12がp+型領域4aに対してオーミック接触させられ、かつ、p型領域4bに対してショットキー接触させられるようにする。具体的には、コレクタ電極12とp型領域4bとの接触部位が確実にショットキー接触となるように、p型領域4bの表面上にバリア金属12aを配置する。これにより、コレクタ側からのホールの注入を抑制して低注入効率となるようにでき、ライフタイム制御を行わなくてもスイッチング動作を更に高速化することが可能な構造の横型IGBTとすることができる。

(もっと読む)

半導体装置及びその駆動方法

【課題】半導体装置における電界の集中を緩和する。

【解決手段】ゲート電極とドレイン電極を重畳させずに設け、且つ上面において、ゲート電極とドレイン電極の間には電界制御電極が設けられている。そして、ゲート電極と半導体層の間、及び電界制御電極と半導体層の間には、それぞれ絶縁層が設けられており、電界制御電極と半導体層の間に設けられた絶縁層は、ゲート電極と半導体層の間に設けられた絶縁層よりも厚い。さらには、この半導体装置を駆動させるに際して、電界制御電極の電位は、ソース電位以上であってゲート電位より低ければよく、例えば、電界制御電極とソース電位を接続させることでこのような構成を実現することができる。

(もっと読む)

電界効果トランジスタおよび半導体装置の作製方法

【課題】導体半導体接合を用いた電界効果トランジスタのゼロ電流を低減せしめる構造を提供する。

【解決手段】半導体層101とゲート105の間に、絶縁物104により周囲を覆われた導体もしくは半導体よりなり、半導体層101を横切るように形成されたフローティング電極102を形成し、これを帯電させることにより、ソース電極103aやドレイン電極103bからのキャリアの流入を防止する。このため半導体層101中のキャリア濃度を十分に低く維持でき、よって、ゼロ電流を低減できる。

(もっと読む)

有機薄膜トランジスタ用化合物及びそれを用いた有機薄膜トランジスタ

【課題】酸化安定性と塗布プロセスが適用可能な溶解性を有する有機薄膜トランジスタ用化合物を提供する。

【解決手段】下記式(1)で表わされる有機薄膜トランジスタ用化合物。 (もっと読む)

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を積層形成する。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】レジストの広がりを容易に制御して、寄生容量の増加を抑制する。

【解決手段】ゲート電極11aa上に、ゲート絶縁膜12、第1半導体膜13、第2半導体膜14及び金属膜を成膜し、金属膜上にレジストを形成する工程と、レジストから露出する金属膜、及びレジストの薄膜部の下層に配置する金属膜の上層部をエッチングしてソースドレイン形成層15aを形成する工程と、レジストRbbから露出するソースドレイン形成層15a及び第2半導体膜14の温度差に基づいてリフロー処理を行いレジストRbcに変形する工程と、レジストRbcを用いて第1半導体層13a及び第2半導体層形成層14aを形成する工程と、レジストRbcを除去した後に、ソース電極及びドレイン電極を形成し、両電極から露出する第2半導体層形成層14aをエッチングして第2半導体層14bを形成する工程とを備える。

(もっと読む)

半導体メモリ装置の駆動方法

【課題】オフ状態のソース、ドレイン間のリーク電流の低いトランジスタを書き込みトランジスタに用いて、データを長期間にわたり保存する半導体メモリ装置の駆動方法を提供する。

【解決手段】書き込みトランジスタのドレインと素子トランジスタのゲート、および、容量素子の一方の電極を接続したメモリセルを複数用いて形成されたマトリクスにおいて、書き込みトランジスタのゲートを書き込みワード線に接続し、キャパシタの他方の電極を読み出しワード線に接続する。そして、容量素子に蓄えられた電荷量を、読み出しワード線の電位を変化させることにより確認し、基準以上に電荷量が減少している場合にはメモリセルのリフレッシュをおこなう。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、上下をゲート電極で挟んだ酸化物半導体を用いた薄膜トランジス

タで構成する。同一基板上に画素部及び駆動回路を設けることによって製造コストを低減

する。

(もっと読む)

電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造

【課題】酸化物反応層の寄生抵抗の低減を図り、動作特性の向上を図った電子デバイス配線用Cu合金スパッタリングターゲット材、及び素子構造を提供する。

【解決手段】TFT素子1は、a−Si膜5上に形成されたPドープn+a−Si膜6と、Pドープn+a−Si膜6上に形成された1nm以下のSi酸化膜7を有している。電極配線膜となるCu合金膜8が、Si酸化膜7上にスパッタリングにより形成されている。Cu合金膜8は、0.3〜2.0原子%のSn、In、Gaの金属のうち1種以上を含有する。

(もっと読む)

有機薄膜トランジスタ及びその製造方法

【課題】大気雰囲気下であっても酸化されにくく、機能的にも劣化しにくい電荷注入層を備えた有機薄膜トランジスタを提供する。

【解決手段】ゲート電極20Aと、第1のソース/ドレイン電極60Aと、第2のソース/ドレイン電極60Bと、前記第1および第2のソース/ドレイン電極と前記ゲート電極との間に設けられる有機半導体層40と、前記第1および第2のソース/ドレイン電極と前記有機半導体層の間において、前記第1および第2のソース/ドレイン電極に接して配置される電荷注入層50とを備える有機薄膜トランジスタ10において、前記電荷注入層は、電荷注入特性を有するイオン性ポリマーを含有する、有機薄膜トランジスタ。

(もっと読む)

半導体膜の作製方法、半導体装置の作製方法、及び光電変換装置の作製方法

【課題】抵抗率の低い不純物元素を有する非晶質半導体を形成する。また、電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】プラズマCVD法により不純物元素を有する非晶質半導体を形成する方法において、パッシェンの法則で最小放電開始電圧を満たす圧力及び電極間隔において、パルス変調した放電開始電圧を電極に印加することより、抵抗率の低い不純物元素を有する非晶質半導体を形成する。

(もっと読む)

101 - 120 / 425

[ Back to top ]