Fターム[5F110HK17]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 材料の特性が規定 (425)

Fターム[5F110HK17]に分類される特許

81 - 100 / 425

薄膜トランジスタの製造装置およびその製造方法、ならびにプログラム

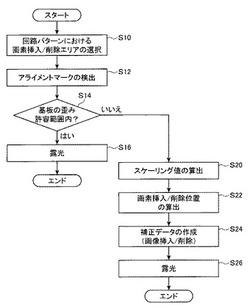

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法、ならびにプログラムを提供する。

【解決手段】本発明は、基板上にゲート電極、ゲート絶縁層、半導体層、ソース電極およびドレイン電極が少なくとも設けられた薄膜トランジスタの製造方法である。ソース電極およびドレイン電極を形成する工程において、基板の歪み、または基板の伸縮率に基づいて、露光データを、スケーリング処理を用いて薄膜トランジスタのチャネル長を固定した状態で補正して第1の補正データを作成する。この第1の補正データに基づいて、ソース電極およびドレイン電極の形成領域にレーザ光を照射し、その形成領域を親液性にする。この形成領域に、ソース電極およびドレイン電極となる液滴を、打滴データに基づいて打滴する。

(もっと読む)

電子デバイス及びその製造方法

【課題】転写プロセスを用いずに、所期のグラフェンを制御性良く容易且つ確実に安定形成し、信頼性の高い高性能の微細な電子デバイスを実現する。

【解決手段】基板1上に絶縁層2を形成し、絶縁層2に空隙2Aを形成し、空隙2Aに触媒材料4を充填し、絶縁層2における触媒材料4の露出面4aにグラフェン5を形成し、絶縁層2上でグラフェン5の両端部に接続するように一対の電極5,6を形成し、グラフェン5を一部除去してグラフェンリボン8を形成し、グラフェンリボン8の除去された部位である間隙2A1,2A2を通じて触媒材料4を除去する。

(もっと読む)

半導体装置及び電子機器

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導

体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作

製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって

形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチ

ング工程において、第1のエッチング工程は、エッチングガスによるドライエッチングを

用い、第2のエッチング工程はエッチング液によるウエットエッチングを用いる。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子

【課題】有機半導体に対する接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】金属層24Aと、金属層24Aの表面の少なくとも一部に付着したカーボンナノチューブ24Bと、を有する有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

半導体装置

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装

置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び

有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電

層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあ

わせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置(薄膜トランジスタ)を製造する。

【解決手段】本発明は、(a)基板SUBの上方に、第1金属酸化物を含有する半導体からなる導電層を形成する工程と、(b)導電層上に第2金属酸化物を含有する半導体からなる犠牲層SLを形成する工程と、(c)導電層と犠牲層SLとの積層膜を加工する工程と、(d)上記(c)工程の後、犠牲層SL上に、金属膜を形成する工程と、(e)上記(d)工程の後、上記金属膜の第1領域をドライエッチングにより除去する工程と、(f)上記(e)工程の後、上記第1領域の上記犠牲層SLをウェットエッチングにより除去する工程と、を有し、上記(c)工程と、上記(f)工程との間に、(g)導電層に熱処理を施し、導電層を結晶化し、導電層CLcとする工程を有する。かかる工程によれば、ドライエッチングにより生じた犠牲層SLのダメージ領域DRを除去できる。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

半導体装置

【課題】集積回路の動作速度の向上に有利な技術を提供する。

【解決手段】n型トランジスタおよびp型トランジスタがシリコンの(551)面に形成された半導体装置において、前記n型トランジスタの拡散領域に接触するシリサイド層の厚さが前記p型トランジスタの拡散領域に接触するシリサイド層の厚さよりも薄い。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成することで、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少なくとも結晶化した領域を有する。

(もっと読む)

有機トランジスタの製造方法

【課題】電界効果移動度が高い有機トランジスタを製造する方法を提供すること。

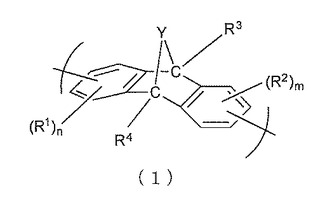

【解決手段】式

[式中、R1及びR2は、それぞれ独立に、置換基を表す。R3及びR4は、それぞれ独立に、水素原子又は置換基を表す。n及びmは、それぞれ独立に、0〜3の整数を表す。Yは、2価の基を表す。R1が複数個ある場合、及びR2が複数個ある場合、それらは同一でも相異なってもよい。]で表される構造単位を含む化合物を含有する有機膜を形成する工程と、Yで表される2価の基の少なくとも一部を脱離させて、有機半導体層を製造する工程とを、有する、ゲート電極、ソース電極、ドレイン電極及び有機半導体層を有する有機トランジスタの製造方法。

(もっと読む)

信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路。特に、短時間の電源停止により消費電力を抑えることができる信号処理回路。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する信号処理回路。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

有機薄膜、有機薄膜の製造方法、電界効果トランジスタ、有機発光素子、太陽電池、表示装置用アレイ及び表示装置

【課題】有機分子の配向性が制御されて十分な機能を有する有機薄膜及びその製造方法、並びに該有機薄膜を用いた有機電子デバイス及び表示装置の提供。

【解決手段】基材60上に第一の有機分子61を化学結合させて立設し、点在させ、第二の有機分子62を導入し、第一の有機分子61に対して第二の有機分子62を配列させて、有機薄膜6を形成する。第一の有機分子61及び第二の有機分子62が有機半導体分子である、かかる有機薄膜を、有機半導体層として設け、電界効果トランジスタとする。

(もっと読む)

チャネルエッチ型薄膜トランジスタとその製造方法

【課題】半導体層の膜厚均一性を向上させたチャネルエッチ型TFTとその製造方法を提供する。

【解決手段】酸化物半導体からなるチャネル層4を形成した後、該チャネル層4の上にIn、Zn、Gaを含む酸化物からなり、上記酸化物半導体よりもエッチングレートが速く、抵抗率が3.38×107Ωcm以下である犠牲層5を形成し、その上にソース電極6及びドレイン電極7を形成して、該ソース電極6とドレイン電極7の間に露出した犠牲層5をウェットエッチング除去することにより、半導体層膜厚の均一性を向上させ、TFT特性とその均一性と、をより向上させることができる。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】本発明は、安定した特性を示す金属酸化物半導体を用いた薄膜トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明の薄膜トランジスタは、ゲート電極1と、ゲート電極1上に設けられたゲート絶縁膜2と、ゲート絶縁膜2上に設けられたドレイン電極3B,4Bと、ゲート絶縁膜2上にドレイン電極3B,4Bと隣接して設けられ、金属酸化物半導体で構成されたチャネル層5とを備え、ドレイン電極3B,4Bは、ゲート電極1への電圧印加によりチャネル層5に形成される反転層101と接触すべくゲート絶縁膜2上に設けられ、チャネル層5を構成する金属酸化物半導体よりも酸化物生成自由エネルギーが若干小さい金属酸化物半導体で構成された第1ドレイン電極3と、第1ドレイン電極3上に設けられ、金属で構成された第2ドレイン電極4とを備える。

(もっと読む)

薄膜トランジスタ

【課題】寄生容量を小さくでき、応答速度低下を抑制することが可能なTFTを提供する。

【解決手段】基材110上に配設した有機半導体層150と、有機半導体層150と接触し、対向してチャネル領域を形成するソース電極120及びドレイン電極130と、有機半導体層150と絶縁層160を介して設けられるゲート電極140と、ソース電極120と導電接続するソース電極配線部125と、ドレイン電極130と導電接続するドレイン電極配線部135と、ゲート電極140と導電接続するゲート電極配線部145と、からなるTFT100であって、積層方向からみて、有機半導体層150が、ゲート電極140を含み、ゲート電極140が、ソース電極120とドレイン電極130とチャネル領域とからなる領域を含み、有機半導体層150の周縁でソース電極配線部125とドレイン電極配線部135との間にはゲート電極配線部145が配される。

(もっと読む)

アクティブマトリックス基板、及び液晶装置

【課題】TFTの光リーク電流が低減され、かつ、従来よりも少ないフォトリソフォグラフィ工程で製造することが可能なアクティブマトリックス基板を提供する。

【解決手段】アクティブマトリックス基板201は、絶縁性基板1上に、基板1側から、ゲート電極2と、ゲート電極2を覆うゲート絶縁膜6と、互いに離間形成されたドレイン電極9及びソース電極11と、チャネル層を含む少なくとも1層の半導体膜21とが順次形成された薄膜トランジスタ101と、画素電極10とが複数対アレイ状に形成されたものである。ドレイン電極9及びソース電極11は、基板1側から透光性導電膜EM2と非透光性導電膜EM3とが順次積層された積層構造を有し、かつ、ドレイン電極9の透光性導電膜EM2及び/又は非透光性導電膜EM3が延設され、この延設部分により画素電極10が形成されたものである。

(もっと読む)

配線構造

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、エッチストッパー層を設けなくてもウェットエッチング時の加工性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、薄膜トランジスタの半導体層と、金属配線膜とを有しており、前記半導体層と前記金属配線膜との間にバリア層を有する配線構造であって、半導体層は酸化物半導体からなり、バリア層は、高融点金属系薄膜とSi薄膜の積層構造を有し、Si薄膜は半導体層と直接接続している。

(もっと読む)

半導体装置及び表示装置

【課題】高融点メタルバリア層を有していなくても、高温熱処理後の電気特性を良好にする技術を提供することを目的とする。

【解決手段】半導体装置は、透明絶縁性基板1上に形成されたゲート電極2と、ゲート電極2上にゲート絶縁膜6を介して順次に形成されたSi半導体能動膜7と、n型の導電型を有するオーミック低抵抗Si膜8とを含む半導体層51と、半導体層51と直接接合された、少なくともアルミニウム(Al)を含むソース・ドレイン電極9,10とを備える。半導体層51は、平面視においてゲート電極2の外周よりも内側に形成され、Si半導体能動膜7の側面とソース・ドレイン電極9,10との界面近傍である第1領域には、少なくとも窒素(N)が含まれる。

(もっと読む)

81 - 100 / 425

[ Back to top ]