Fターム[5F110HL08]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−コンタクトホール介在 (16,138) | 材料 (10,537) | 半導体 (328)

Fターム[5F110HL08]に分類される特許

321 - 328 / 328

レーザ処理装置、レーザ照射方法、及び半導体装置の作製方法

【課題】 レーザ照射時の振動の発生を抑制し、一様なエネルギープロファイルを持つレーザビームを一方向に移動させることにより、信頼性のよい半導体装置を短時間で量産する。

【解決手段】 円柱状の回転体の表面に、回転体の曲率に沿って基板を回転体表面に吸着させ、回転体を回転させ、基板上に成膜された半導体膜を一度にレーザ照射する。また、回転体の回転軸方向に移動機構を設け、回転体が1回転したときに照射位置をずらすようにする。または回転体を回転させながら回転軸方向に移動させることも可能である。

(もっと読む)

半導体装置及びその作製方法

【課題】本発明は、低コストで大量生産が可能である半導体装置及びその作製方法を提供する。また、非常に膜厚の薄い集積回路を用いた半導体装置、及びその作製方法を提供する。更には、低消費電力である半導体装置及びその作製方法を提供する。

【解決手段】本発明は、絶縁表面上に半導体不揮発性記憶素子トランジスタを有し、メモリトランジスタのフローティングゲート電極が、複数の導電性粒子又は半導体粒子で形成されていることを特徴とする半導体装置である。

(もっと読む)

電気光学装置及び電子機器、並びに電気光学装置の製造方法

【課題】 電気光学装置において、他の不具合を発生させずに光リーク電流の発生を抑制し、高品位な表示を可能とする。

【解決手段】 基板上に、チャネル領域を有する半導体層を含んで構成された薄膜トランジスタと、薄膜トランジスタにより駆動される表示用電極と、半導体層の上層側及び下層側の少なくとも一方に積層された層間絶縁膜と、該層間絶縁膜の半導体層側とは反対側に積層された、チャネル領域を遮光するための遮光膜とを備えている。層間絶縁膜における半導体層とは反対側の表面には、チャネル領域のうち少なくともチャネル領域の縁部を遮光可能な領域において、半導体層に向かって局所的に窪んだ凹部が形成されている。遮光膜は、少なくとも凹部内に形成されている。

(もっと読む)

薄膜トランジスタの作製方法

【課題】 しかし、薄膜トランジスタを有する表示装置では、同一対象物、例えば同一絶縁膜のエッチング条件を最適化することが難しかった。これは、同一絶縁膜において、エッチングする絶縁膜の膜厚や面積が異なるためである。特に面積の小さなコンタクトホールは、エッチングする量がその他の開口部と異なる。

【解決手段】 上記課題を鑑み本発明は、第1のマスクを用いて、第1の領域の対象物をエッチングして広面積な開口部を形成し、第2のマスクを用いて、第2の領域の前記対象物をエッチングして微細な開口部、つまりコンタクトホールを形成することを特徴とする。

(もっと読む)

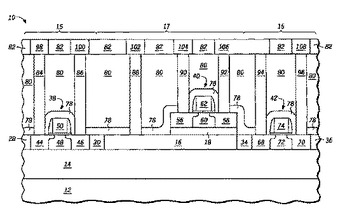

複数の半導体層を備えた半導体デバイス

半導体デバイス構造(10)では、N及びPチャネルトランジスタキャリア移動度を別々に最適化するため、二つの半導体層(16、20)が使用される。これを決定する導電特性は、半導体の材料の種類、結晶面、配向性及び歪みの組み合わせである。シリコンゲルマニウムの半導体材料、圧縮性歪み、(100)の結晶面及び<100>の配向性を特徴とする導電特性の場合、Pチャネルトランジスタ(38)においてホール移動度が向上する。また、結晶面は(111)であってもよく、この場合、配向性は重要ではない。N型伝導に適した基板は、P型伝導に適した(又は最適)基板とは異なる。Nチャネルトランジスタ(40)は、好ましくは、引っ張り歪み、シリコン半導体材料及び(100)面を有する。別の半導体層(16、20)では、N及びPチャネルトランジスタ(38、40)はいずれもキャリア移動度に対し最適化される。  (もっと読む)

(もっと読む)

III族窒化膜双方向スイッチ

【課題】電力用デバイスにおいて双方向に電圧をブロックできるようにする。

【解決手段】大電流を搬送するチャンネルを得るAlGaN/GaNインターフェースを備えたIII族窒化物双方向スイッチであり、この双方向スイッチは、この双方向スイッチのために、電流を搬送するチャンネルを形成するための二次元電子ガスの発生を阻止したり、または可能にする少なくとも1つのゲートにより作動する。

(もっと読む)

フロントゲート型SOI−MOSFETの製造方法

【課題】ソース/ドレイン拡張とフロントゲート(front gate)に自己整合させたバックゲートを含む、FD型SOI−CMOSデバイスの製造方法に関する。

【解決手段】

SOI−CMOS技術は、ポリシリコン、即ちポリSiバックゲートは、フロントゲート・デバイスの閾値電圧を制御するために使用され、nMOS及びpMOSバックゲートは、互いに独立に、及びフロントゲートと独立に、スイッチされる。

特に、バックゲートが、デバイスのフロントゲート及びソース/ドレイン拡張に自己整合されたバックゲートFD型CMOSデバイスの製造方法を提供する。バックゲートFD型CMOSデバイスは、SIMOX又は結合SOI−ウエハ、ウエハボンディングと薄膜化、ポリSiエッチング、LP−CVD、機械化学研磨(CMP)を用いて製造される。

(もっと読む)

薄膜トランジスタアレイ及びその製造方法、液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法

【課題】 本発明は薄膜トランジスタアレイ及びその製造方法と液晶表示装置及びその製造方法とエレクトロルミネッセンス表示装置及びその製造方法に関するものであり、均一性と性能に優れた薄膜トランジスタ及びその製造方法を生産性が高く低コストで提供することを目的とする。

【解決手段】 ゲート電極側面に側壁を形成することによって、自己整合的にLDDまたはオフセット領域を形成し、また、層間絶縁膜を複数の層で形成し、これら複数の層間絶縁膜上にソース・ドレイン電極とソースバス配線と画素電極を一括して形成する。

(もっと読む)

321 - 328 / 328

[ Back to top ]