Fターム[5F110HM02]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 断面形状 (1,337)

Fターム[5F110HM02]の下位に属するFターム

テーパ状 (428)

Fターム[5F110HM02]に分類される特許

201 - 220 / 909

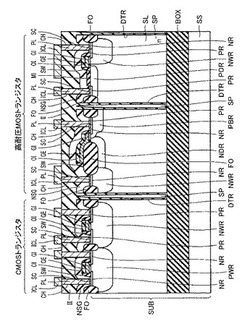

半導体装置およびその製造方法

【課題】簡易なプロセスで、高い埋め込み性を確保する必要のない半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法では、まず支持基板SSと、埋め込み絶縁膜BOXと半導体層SLとがこの順で積層された構成を有する半導体基板SUBが準備される。半導体層SLの主表面に、導電部分を有する素子が完成される。上記素子を平面視において取り囲む溝DTRが、半導体層SLの主表面から埋め込み絶縁膜BOXに達するように形成される。上記素子上を覆うように、かつ溝DTR内に中空を形成するように素子上および溝DTR内に第1の絶縁膜(層間絶縁膜II)が形成される。上記第1の絶縁膜に素子の導電部分に達する孔であるコンタクトホールCHが形成される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的とする。

【解決手段】チャネル形成領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極及び第1のドレイン電極と、を有する第1のトランジスタと、酸化物半導体層と、第2のソース電極及び第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、第2のソース電極または第2のドレイン電極の一方と、第2のゲート絶縁層と、第2のゲート絶縁層上に第2のソース電極または第2のドレイン電極の一方と重畳するように設けられた電極と、を有する容量素子と、を有し、第1のゲート電極と、第2のソース電極又は第2のドレイン電極の一方とは電気的に接続されている。

(もっと読む)

半導体装置

【課題】SOI基板を利用した半導体装置の高耐圧化を実現すること。

【解決手段】IGBT10の電圧保持領域60は、n型の裏面部拡散領域62とn型中間部拡散領域64とp型中間部拡散領域66と表面部拡散領域68を有している。裏面部拡散領域62の不純物濃度は、横方向に沿って、ボディ領域88側からコレクタ領域72側に向けて増加する。

(もっと読む)

エピタキシャルソース/ドレインが自己整合したマルチゲート半導体デバイス

低寄生抵抗であるチャネル歪みされたマルチゲートトランジスタとその製造方法に係る。ゲートを連結したチャネル側壁の高さがHsiである半導体フィンのチャネル領域の上にゲートスタックを形成されてよく、ゲートスタックに隣接する半導体フィンのソース/ドレイン領域内に、エッチングレートを制御するドーパントを注入してよい。ドーピングされたフィン領域をエッチングして、半導体フィンの、略Hsiに等しい厚みを除去して、ゲートスタックの一部の下にある半導体基板の部分を露呈させるソース/ドレイン延長キャビティを形成してよい。露呈した半導体基板の上に材料を成長させて、再成長したソース/ドレイン・フィン領域を形成して、ソース/ドレイン延長キャビティを充填して、ゲートスタックからの長さを、チャネルの長さに実質的に平行な方向に離れる方向に延ばしてよい。 (もっと読む)

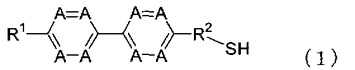

金属電極および該金属電極を有する有機半導体素子

【課題】本発明は、有機高分子等の半導体薄膜形成材料が単結晶でなく、多結晶であっても、印刷方法により金属電極上に安定で良好な有機半導体薄膜を簡便に形成することができ、性能の優れた有機半導体素子を提供することを課題とする。

【解決手段】本発明の金属電極は、下記式(1)で表される化合物を含有する溶液を用いて形成された表面処理層を有することを特徴とする。 (もっと読む)

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

誘電体分離型半導体装置

【課題】高耐圧かつ、電流駆動能力が高く、かつ電流集中による素子破壊の起こりにくい誘電体分離型半導体装置を提供する。

【解決手段】半導体支持基板の上に、絶縁された第一導電型の半導体領域とを有する誘電分離基板に形成した誘電体分離型半導体装置において、第一導電型の半導体領域と絶縁分離領域の間と、前記第1導電型の半導体領域の基板表面側と、に形成されたドレイン領域と、第一導電型のソースと第二導電型の半導体領域のチャネルからなる複数個の単位ソース領域と、第一導電型の半導体領域の基板表面側に形成されたドレイン領域と前記複数個の単位ソース領域の間を制御する複数個のゲート電極とを、備え、隣接する前記単位ソース領域間に絶縁分離領域が、基板底面側から基板表面側に向けて突き出した形状とされ、この絶縁分離領域上の素子表面領域が前記第一導電型の半導体領域より抵抗値が高い。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極にシリサイドを形成しつつ、拡散領域に接続するコンタクトとゲート電極の間隔を確保する。

【解決手段】被覆絶縁膜120は、ゲート電極140のチャネル幅方向における少なくとも一部上に形成されている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、ゲート電極140上、及び被覆絶縁膜120上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。シリサイド層142は、ゲート電極140上に形成されている。サイドウォール160は、被覆絶縁膜120が形成されている領域においてはゲート電極140より高く形成されている。そしてコンタクト210は、ゲート電極140のうち被覆絶縁膜120が形成されている領域に面している。

(もっと読む)

半導体装置

【課題】有機半導体層を用いた半導体装置において、寄生トランジスタを抑制することができ、電荷移動度に優れた半導体装置を提供する。

【解決手段】ゲート電極1と、ゲート絶縁膜2と、有機半導体層3と、有機半導体層3のうち、ゲート絶縁膜2との界面付近の部分のみに接続された、第1の導電材料からなるソース/ドレイン電極4と、有機半導体層3のそれ以外の部分に接続され、第1の導電材料とは異なる第2の導電材料から成り、有機半導体層3との間では電荷の移動が生じない電極層5とを含む半導体装置を構成する。

(もっと読む)

表示装置

【課題】狭額縁化が可能であり、表示特性に優れた表示装置を提供する。

【解決手段】駆動回路及び画素部を有し、駆動回路は、デュアルゲート型の薄膜トランジスタを用いて構成され、画素部はシングルゲート型の薄膜トランジスタを用いて構成される表示装置である。該表示装置おけるデュアルゲート型の薄膜トランジスタは、半導体層が微結晶半導体領域及び一対の非晶質半導体領域で形成され、ゲート絶縁層及び絶縁層が半導体層の微結晶半導体領域に接する。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体装置

【課題】良質な半導体装置を提供することを目的としている。

【解決手段】素子分離領域間の凸部108を含むシリコン基板106と、凸部108上の絶縁部112と、絶縁部112上のシリコンフィン114と、上面が凸部108の上面よりも低く位置する素子分離領域内の素子分離層116と、シリコンフィン114に設けられたソース/ドレイン領域と、ソース/ドレイン領域104のシリコンフィン114の側面から外側に突き出た横方向エピ成長シリコン部118と、ゲート電極領域102内のゲート絶縁層122を介してシリコンフィン114上に設けられるゲート電極124と、ゲート電極124の側面に隣接する第1のスペーサ128と、ソース/ドレイン領域104内の凸部108の側面を覆う第2のスペーサ130とを備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】SiGe等の半導体膜が形成された領域と、酸化シリコン膜から成るゲート絶縁膜が形成された領域とが同一基板上に形成される際に、ゲート絶縁膜を精度良く形成する。

【解決手段】基板10を熱酸化することにより、第1素子領域101及び第2素子領域201に、第1ゲート絶縁膜110及び第2ゲート絶縁膜210を形成し、かつ第3素子領域301及び第4素子領域401それぞれに位置する基板10に熱酸化膜を形成する。次いで、第4素子領域401に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する基板10上に半導体膜414を成膜する。次いで、第3素子領域301に位置する熱酸化膜を除去する。次いで、第4素子領域401に位置する半導体膜414上、及び第3素子領域301に位置する基板10上に第3ゲート絶縁膜310及び第4ゲート絶縁膜410を形成する。

(もっと読む)

トランジスタ

【課題】生産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供する。または、新たな半導体材料を用いた新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体中で電子供与体(ドナー)となりうる不純物を除去することで、真性又は実質的に真性な半導体であって、シリコン半導体よりもバンドギャップが大きい酸化物半導体でチャネル形成領域が形成される縦型トランジスタであり、酸化物半導体の厚さが1μm以上、好ましくは3μmより大、より好ましくは10μm以上であり、酸化物半導体に接する電極の一方の端部が、酸化物半導体の端部より内側にある。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

半導体装置およびその作製方法

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】チャネル抵抗の増大を回避させた薄膜トランジスタの提供。

【解決手段】ボトムゲート型の薄膜トランジスタであって、ゲート絶縁膜上にゲート電極の形成領域に開口を有する層間絶縁膜が形勢され、半導体膜は前記開口を被って層間絶縁膜上に形成され、

前記層間絶縁膜は前記ゲート絶縁膜よりも窒化物を多く含み、前記半導体膜は、前記ゲート絶縁膜および前記層間絶縁膜面に形成された少なくともGeを含む半導体結晶核上に形成された微結晶半導体膜あるいは多結晶半導体膜によって構成されている。

(もっと読む)

薄膜トランジスタ

【課題】イオン注入を行わずに低コストで製造できる構造形態を備えた薄膜トランジスタを提供する。

【解決手段】基板10上(又は第1下地膜11乃至第2下地膜12上)に設けられたポリシリコン半導体膜13と、ポリシリコン半導体膜13上に離間して設けられたソース電極15s及びドレイン電極15dと、ポリシリコン半導体膜13上にゲート絶縁膜14を介して設けられたゲート電極15gとを少なくとも有する。ポリシリコン半導体膜13は、面内方向にソース電極接続領域13s、チャネル領域13c及びドレイン電極接続領域13dを有し、チャネル領域13cにはドーパントが含まれておらず、ソース電極接続領域13s及びドレイン電極接続領域13dは基板10側からソース電極側及びドレイン電極側に向かってドーパント一定濃度層21とドーパント減少傾斜層22’とを有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成してからチャネル形成用半導体部を形成する方法において、結晶品質の良い単結晶Siを用いて良質なゲート絶縁膜を形成した縦型半導体装置を提供する。

【解決手段】単結晶半導体基板に少なくとも第1絶縁層を有する積層体を形成する工程S1と、前記積層体に、前記単結晶半導体基板が露出する孔を形成する工程S2と、前記孔の底面に露出している前記単結晶半導体基板を種結晶領域とすることにより、前記第1絶縁層の上にゲート電極となる単結晶半導体部を形成する工程S3と、前記孔内に埋められた前記単結晶半導体部を除去することで、前記孔の底面に前記単結晶半導体基板を再び露出させる工程S4と、前記単結晶半導体部の前記孔の側面に露出している部分にゲート絶縁膜を形成する工程S5と、前記孔にチャネル形成用半導体部を形成する工程S6と、を有する半導体装置の製造方法。

(もっと読む)

多結晶シリコン層の製造方法、薄膜トランジスタ、それを含む有機電界発光表示装置及びその製造方法

【課題】有機電界発光表示装置及びその製造方法を提供する。

【解決手段】基板100上に位置するバッファ層110と、バッファ層110上に位置する半導体層と、基板100全面にわたって位置するゲート絶縁膜と、半導体層に対応するゲート電極と、ゲート電極と絶縁され、半導体層と接続されるソース/ドレイン電極とを含み、半導体層の上部表面には溝を含んでおり、上記溝には金属シリサイトが位置することを特徴とする薄膜トランジスタ及びその製造方法に関し、上記薄膜トランジスタを含む有機電界発光表示装置及びその製造方法。

(もっと読む)

201 - 220 / 909

[ Back to top ]