Fターム[5F110HM02]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 断面形状 (1,337)

Fターム[5F110HM02]の下位に属するFターム

テーパ状 (428)

Fターム[5F110HM02]に分類される特許

121 - 140 / 909

半導体装置およびその作製方法

【課題】新規な構造の半導体装置あるいはその作製方法を提供することを課題とする。例えば、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図ることを課題とする。

【解決手段】トランジスタの信頼性向上を図るため、電界集中を緩和するバッファ層をドレイン電極層(またはソース電極層)と、酸化物半導体層との間に設け、バッファ層の端部をドレイン電極層(またはソース電極層)の側面から突出させた断面形状とする。バッファ層は、単層又は複数の層からなる積層で構成し、例えば窒素を含むIn−Ga−Zn−O膜、窒素を含むIn−Sn−O膜、SiOxを含むIn−Sn−O膜などを用いる。

(もっと読む)

電荷注入特性が高い有機薄膜トランジスタ

【課題】トランジスタ特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタ、及びその製造方法を提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、該第1導電層は、塗布法を用いて形成されたものであり、該第1導電層の端部は該第2導電層の端部と比較して電極ブロックの内側に位置している有機薄膜トランジスタ。

(もっと読む)

半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】電気的特性が良好な半導体装置の作製方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、HBrガスと、CF4ガスと、酸素ガスの混合ガスを含むガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを薄膜トランジスタのバックチャネル部を形成するエッチングに適用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

トランジスタの作製方法

【課題】特性のバラツキが少なく、電気特性が良好なトランジスタを作製する。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体を含む半導体層を形成し、半導体層上に不純物半導体層を形成し、不純物半導体層上にマスクを形成した後、マスクを用いて半導体層及び不純物半導体層をエッチングして、半導体積層体を形成し、マスクを除去した後に半導体積層体を希ガスを含む雰囲気で発生させたプラズマに曝して半導体積層体の側面に障壁領域を形成し、半導体積層体の不純物半導体層に接する配線を形成する。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置を提案することを課題とする。

【解決手段】基板上に形成されたゲート電極と、ゲート電極上に形成された酸素過剰のSiOX膜と、SiOX膜上に形成された酸化物半導体膜と、を有する半導体装置。

(もっと読む)

半導体装置、パワーダイオード及び整流器

【課題】高耐圧、低逆方向飽和電流、高いオン電流などの電気特性を有する半導体装置を提供することである。なかでも、非線形素子より構成されるパワーダイオード及び整流器を提供することである。

【解決手段】第1の電極と、第1の電極を覆うゲート絶縁層と、ゲート絶縁層と接して且つ第1の電極と重畳する酸化物半導体層と、酸化物半導体層の端部を覆う一対の第2の電極と、一対の第2の電極及び酸化物半導体層を覆う絶縁層と、絶縁層に接して且つ一対の第2の電極の間に設けられる第3の電極と、を有し、一対の第2の電極は酸化物半導体層の端面に接する半導体装置である。

(もっと読む)

表示装置、及び、その製造方法

【課題】薄膜トランジスタにおいて生じるリーク電流を抑えつつ、表示装置の生産性を向上させることを目的とする。

【解決手段】基板301と、基板301に形成されている複数の薄膜トランジスタTFTと、を有する表示装置であって、薄膜トランジスタTFTは、ゲート電極303と、ゲート電極303の上側に配置される微結晶半導体層305と、微結晶半導体層305上に配置される非晶質半導体層306と、を有し、非晶質半導体層306の水素濃度が、12atom%以下である、ことを特徴とする表示装置。

(もっと読む)

横型半導体装置

【課題】高い耐圧性能と長期信頼性を両立可能な半導体装置を提供する。

【解決手段】半導体基板の一主表面上においてドリフト領域を挟むように第1電極部と第2電極部とが各々分離形成され、ドリフト領域上部には酸化膜層が形成され、ドリフト領域、第1電極部、第2電極部、および酸化膜層が層間絶縁膜層により覆われた横型半導体装置であって、第1導電型半導体と第2導電型半導体とを交互にドリフト領域におけるキャリアのドリフト方向へ直列接続して成る連続接合半導体層が酸化膜層と層間絶縁膜層との境界部に設けられ、連続接合半導体層の一方端部は、第2電極部と並列に電源電位線に接続されていることを特徴とする、横型半導体装置である。

(もっと読む)

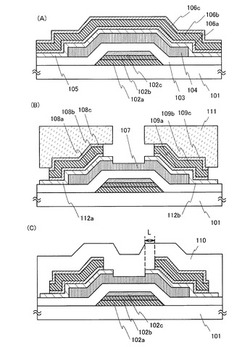

半導体装置及びその作製方法

【課題】マスク枚数を増加させることなく、積層構造の導電層の下層が露出した構造を有する半導体装置の作製方法を提供する。

【解決手段】ソース電極及びドレイン電極層を形成する導電膜を2層の積層構造で形成し、該導電膜上にエッチングマスクを形成し、該エッチングマスクを用いて該導電膜をエッチングし、該エッチングマスクを残した状態で該導電膜の上層をサイドエッチングして該導電膜の下層の一部を露出させてソース電極及びドレイン電極層とする。このように形成したソース電極及びドレイン電極層と画素電極層は、露出された下層の部分において接続される。ソース電極及びドレイン電極層を形成する導電膜は、例えば、下層をTi層とし、上層をAl層とすればよい。エッチングマスクに開口部が複数設けられていてもよい。

(もっと読む)

半導体装置

【課題】接続配線に起因する耐圧低下を防止できる半導体装置の耐圧特性をさらに向上させることができる半導体装置の提供。

【解決手段】半導体層の第1素子領域に配置されており、第1主電極と第2主電極を有する第1種類の第1半導体素子と、半導体層の第2素子領域に配置されており、第3主電極と第4主電極を有する第2種類の第2半導体素子とを備え、第1素子領域と第2素子領域は、電流が流れる方向に対して直交する方向に隣接し、かつ、第1素子領域と第2素子領域を含む素子領域全体で一巡する形に形成され、半導体層を平面視したときに、第1素子領域の曲率は、第2素子領域の曲率よりも小さい。

(もっと読む)

高電圧薄膜トランジスタを使用するMEMS装置のための集積化ドライバ電子工学

【課題】作動MEMS装置及び該作動MEMS装置を制御するためのドライバ回路を提供する。

【解決手段】ドライバ回路は、基板上に形成される複数の高電圧薄膜トランジスタ(HVTFT)を含み、各HVTFTは、制御ゲート電極、ソース電極、及び、該ソース電極が制御ゲート電極から第1の距離だけ離れるように配置されたドレイン電極を含む。このドレイン電極は、ドレイン電極のいずれか一部及び制御ゲート電極の間の最短距離が第1の距離より十分に大きいように、ドレイン電極及びソース電極間の第1の破壊電圧が制御ゲート電極及びソース電極間の第2の破壊電圧より大きいように、制御ゲート電極から離間される。複数の作動MEMS装置は、上記基板上に形成され、複数のHVTFTのうちの関連したHVTFTのドレイン電極にそれぞれ接続される。

(もっと読む)

アレイ基板およびその製造方法、並びに液晶ディスプレー

【課題】ソース・ドレイン電極と別体に形成された拡張導電部によって、TFTスイッチング素子の有効チャネル長を短くする。

【解決手段】アレイ基板であって、ベース基板を有し、ベース基板に縦横に交差するデータラインとゲートラインが形成されてマトリックス状に配列する複数の画素ユニットが画成され、各画素ユニットにスイッチング素子が設置される。各スイッチング素子は、ゲート電極、活性層、ソース電極およびドレイン電極と、拡張導電部とを有し、前記ソース電極と前記ドレイン電極の前記活性層に接触する端部は対向してチャネル領域を定義し、前記拡張導電部は、前記ソース電極または前記ドレイン電極に隣接して電気的に接触し、前記拡張導電部の端部は、前記拡張導電部に接触するソース電極またはドレイン電極を超え、前記チャネル領域内に延び、少なくとも前記チャネル領域内で前記活性層に接触する。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を積層形成する。

(もっと読む)

表示装置

【課題】

表示装置の高解像度化や小型化、さらには画素の開口率の向上を行った場合でも、半導体層に入射する光を効果的に遮断し、ホトコン電流による表示品質の低下を防止することが可能な表示装置を提供すること。

【解決手段】

前記基板上に、第1絶縁膜と、ゲート電極と、ゲート電極の上層に形成された第2絶縁膜と、前記第2絶縁膜の上層に形成された半導体層とが積層され、前記第1絶縁膜は開口部を有し、前記ゲート電極は、前記開口部に倣って形成された窪みを有し、前記半導体層の全部、又は前記半導体層の端部は、平面的に見て前記窪みと重畳していることを特徴とする。

(もっと読む)

結晶化用光マスク及びこれを利用した薄膜トランジスタ表示板の製造方法

【課題】薄膜トランジスタの特性を均一に確保できる結晶化用光マスク及びそれを利用した薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】本発明による結晶化用光マスクは、スリットが一定に配列されている一つ以上のスリット領域を含み、前記スリットはマスクの移動方向に対し一定角度で傾斜して設けられ、スリット領域は、第1の長さを有する第1部分と第1の長さよりも長い第2の長さを有する第2部分とを含む。

(もっと読む)

半導体装置

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおけるソースの高キャリア濃度化をプロセス面での負荷を抑えつつ実現する。

【解決手段】ゲート絶縁膜30は、3−5族化合物半導体のチャネル層20の第1面のゲート領域に形成される。ソースコンタクト層34およびドレインコンタクト層38は、チャネル層20の第1面にゲート領域を挟むように位置するドレイン領域およびソース領域それぞれに形成される。裏面絶縁膜50は、チャネル層20の第1面と反対側の第2面側に形成される。ソース下面電極52は、裏面絶縁膜50のチャネル層20と反対の面側に、ソースコンタクト層34と対向する領域に形成される。

(もっと読む)

半導体装置

【課題】裏面に対する各種プロセスを必要としない簡素な構造の半導体装置を提供する。

【解決手段】活性層2に対して埋込絶縁膜4との境界部分にn+型埋込領域6が形成されているSOI基板5を用いて、素子領域8と配線引出部9との間にトレンチ分離部11を配置し、トレンチ分離部11をn-型ドリフト層7と同じもしくはそれより深く、かつ、埋込絶縁膜4から離間するように形成する。このような構成とすれば、SOI基板5に対して予め形成しておけるn+型埋込領域6を介して行うことができる。このため、高耐圧MOSFET1の素子領域8と配線引出部9との電気的な接続を裏面電極などを備える必要がなく、裏面に対する各種プロセスを必要としない簡素な構造の半導体装置により、層間絶縁膜18に大きな電位差が掛かることを抑制できる。また、電位分布が不均一になることを防止でき、高耐圧MOSFET1の耐圧低下を抑制することも可能となる。

(もっと読む)

121 - 140 / 909

[ Back to top ]