Fターム[5F110HM04]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 平面形状 (975)

Fターム[5F110HM04]に分類される特許

201 - 220 / 975

電界効果トランジスタおよび半導体装置

【課題】導体半導体接合を用いて、優れた特性を示す、あるいは、作製の簡単な、あるいは、より集積度の高い電界効果トランジスタを提供する。

【解決手段】半導体層の電子親和力よりも仕事関数の小さな導体との接合においては、導体より半導体層にキャリアが注入された領域が生じる。そのような領域を電界効果トランジスタ(FET)のオフセット領域、あるいは、インバータ等の半導体回路の抵抗として用いる。また、ひとつの半導体層中にこれらを設けることにより集積化した半導体装置を作製できる。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】薄膜トランジスタ及びその製造方法を提供すること。

【解決手段】薄膜トランジスタは基板上に形成されたゲート電極、ゲート電極と重なり、第12族元素と第16族元素(但し、酸素元素は除く)または第13族元素と第15族元素を含む非結晶質の多元系化合物(multi−elements compound)を含んで、電子移動度が約0.8cm2/Vs以上の半導体パターン、半導体パターンの第1端部と重なるソース電極、及び半導体パターンの第2端部と重なってソース電極と離隔されたドレイン電極を含む。非結晶質の多元系化合物を半導体パターンに適用することによって薄膜トランジスタの駆動特性を向上させることができる。

(もっと読む)

半導体装置

【課題】消費電力の増加を招くことなくオフの状態を実現することのできる半導体装置を提供する。

【解決手段】ゲートに電圧が印加されていない状態でオン状態であるパワー素子と、パワー素子のゲートに第1の電圧を印加するためのスイッチング用の電界効果トランジスタと、パワー素子のゲートに第1の電圧より低い電圧を印加するためのスイッチング用の電界効果トランジスタと、を有し、上記スイッチング用の電界効果トランジスタはオフ電流が小さい半導体装置である。

(もっと読む)

信号処理回路、及び信号処理回路の駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。そして、上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

液晶表示装置用アレイ基板及びその製造方法

【課題】本発明は、3マスク工程による液晶表示装置用アレイ基板で島状に半導体層を構成することにより、マスク数の減少と信頼性を向上する。また、マスク数の減少のために3マスク工程で液晶表示装置用アレイ基板を製作する過程で、リフトオフ工程による不良を最小化することができる。

【解決手段】本発明は液晶表示装置及びその製造方法に係り、3マスク工程の核心工程であるリフトオフ工程時スパターリング法を利用して保護膜パターンを形成することによってリフトオフ不良を最小化する。また、アクティブ及びオーミックコンタクト層を含む半導体層をデータ配線、ソース及びドレイン電極と別個のマスクを利用して島状にゲート電極内に形成することによって漏れ電流を防止する。

(もっと読む)

表示装置とその作製方法

【課題】安定した電気的特性(例えば、オフ電流がきわめて低減されている)を有するトランジスタで構成される表示装置を提供することを目的とする。

【解決手段】トランジスタを形成するための半導体材料としてシリコン半導体よりも禁制帯幅(バンドギャップ)の広い半導体材料を用い、好ましくは、かかる半導体材料のキャリア供与体となる不純物の濃度を低減することでオフ電流の低減を図る。そのために、トランジスタの半導体層(チャネル領域を形成する層)としてエネルギーギャップが2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上の酸化物半導体を用い、該酸化物半導体に含まれるキャリア供与体となる不純物の濃度を低減させている。それにより、トランジスタのオフ電流を、室温にてチャネル幅1μm当たり10zA/μm未満、85℃にて100zA/μm未満と極めて低いレベルにまで低減させることを可能とする。

(もっと読む)

電圧調整回路

【課題】トランジスタにおけるオフ電流を低減し、電圧調整回路における出力電圧の変換効率を向上させる。

【解決手段】ゲート、ソース、及びドレインを有し、ゲートがソース又はドレインに電気的に接続され、ソース及びドレインの一方に第1の信号が入力され、チャネル形成層としてキャリア濃度が5×1014/cm3以下である酸化物半導体層を有するトランジスタと、第1の電極及び第2の電極を有し、第1の電極がトランジスタのソース及びドレインの他方に電気的に接続され、第2の電極にクロック信号である第2の信号が入力される容量素子と、を有し、第1の信号の電圧を昇圧又は降圧し、昇圧又は降圧した電圧である第3の信号を出力信号としてトランジスタのソース及びドレインの他方を介して出力する構成である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】IGBTを構成するバイポーラトランジスタのターンオフ時間を短くし、かつIGBTを構成するバイポーラトランジスタを動作しやすくする。

【解決手段】シンカー層115は第1導電型ウェル102及び第2導電型ドリフト層104それぞれに接しており、かつ第1導電型コレクタ層108から離れている。シンカー層115の表層には、第2導電型拡散層(第2の第2導電型高濃度拡散層)116が形成されている。第2導電型拡散層116はシンカー層115より不純物濃度が高い。第2導電型拡散層116と第1導電型コレクタ層108は、素子分離絶縁膜16を介して互いに分離している。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】チャネル形成領域に結晶化率の高い領域を配し、電界効果移動度が高く、オン電流が大きい薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタの半導体層中に逆錐形状の結晶粒を含ませ、下地層上に設けられた第1の配線層と、第1の配線層に少なくとも一部が接する不純物半導体層と、少なくとも一部が不純物半導体層を介して第1の配線層と電気的に接続される半導体層と、半導体層上に設けられた第1の絶縁層と、少なくとも半導体層と第1の絶縁層を覆って設けられた第2の絶縁層と、第2の絶縁層上であって、不純物半導体層の少なくとも一部、及び不純物半導体層によって形成されるソース領域とドレイン領域の間に重畳して設けられた第2の配線層と、を有する薄膜トランジスタとする。

(もっと読む)

薄膜トランジスタ、表示装置及び薄膜トランジスタの作製方法

【課題】チャネル形成領域に結晶化率の高い領域を配し、ソースとドレインの間に高抵抗な領域を配し、電界効果移動度が高くオン電流が大きい薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタの下地層に「結晶核の生成を抑制する不純物」を含ませ、または下地層の表面に「結晶核の生成を抑制する不純物」を存在させ、下地層上に設けられた第1の配線層と、第1の配線層に少なくとも一部が接する不純物半導体層と、少なくとも一部が不純物半導体層を介して第1の配線層と電気的に接続される半導体層と、半導体層上に設けられた第1の絶縁層と、少なくとも半導体層と第1の絶縁層を覆って設けられた第2の絶縁層と、第2の絶縁層上であって、不純物半導体層の少なくとも一部、及び不純物半導体層によって形成されるソース領域とドレイン領域の間に重畳して設けられた第2の配線層と、を有する薄膜トランジスタとする。

(もっと読む)

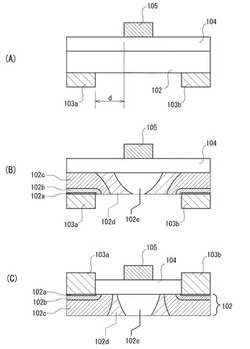

薄膜トランジスタとその作製方法

【課題】薄膜トランジスタのオン電流を大きくする。

【解決手段】薄膜トランジスタのバックチャネル部に凸部を設ける。該凸部は、ソースまたはドレインからチャネル形成領域まで引いたバックチャネル部の接線を避けて設けられる。該凸部により電荷のトラップ箇所とオン電流の経路を遠ざけることができ、オン電流を大きくすることができる。バックチャネル部の側面の形状は曲面であってもよいし、断面において直線で表される形状であってもよい。更には、一括してエッチングを行うことでこのような形状を形成する方法を提供する。

(もっと読む)

記憶装置、半導体装置、及び電子機器

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた半導体装置の提供を目的の一つとする。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積及び放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、酸化物半導体をチャネル形成領域に含むトランジスタを用いる。位相反転素子への電源電圧の印加を停止する場合、データを容量素子に記憶させることで、位相反転素子への電源電圧の供給を停止しても、容量素子においてデータを保持させる。

(もっと読む)

半導体装置およびその製造方法

本発明の方法(20)は、端部の第1の組を有する分離された要素を含むパターンで導電材料層を基板上に提供する段階(21)を含む、半導体装置の製造に関する。本方法は、段階(22)において、基板上にそれらの間に一つ以上のキャビティを形成するための一連の壁構造体を提供する段階をさらに含む。壁構造体は端部の第1の組と協働する端部の第2の組を有する。端部の第2の組は所定の距離で端部の第1の組から後退する。さらに、本方法は段階(24)において、キャビティ内に液体材料を堆積する段階を含む。上述の特徴を有するディスプレイおよび電子装置も開示される。  (もっと読む)

(もっと読む)

電界効果トランジスタ、電子装置、電界効果トランジスタの製造方法及び使用方法

【課題】 チップ面積を大きくし過ぎることなく、過電圧、過電力が加わっても破壊されない電界効果トランジスタを提供する。

【解決手段】 本発明の電界効果トランジスタは、

半導体層上に、ゲート電極110と、ドレイン電極109と、ソース電極108と、保護ダイオード(保護ダイオード電極)111とが配置され、

ドレイン電極109が、保護ダイオード111の周囲の一部もしくは全部を囲む状態で形成されているか、または、

ドレイン電極109は、複数であり、複数のドレイン電極109の少なくとも一対のドレイン電極間に、保護ダイオード111が配置されるように形成されていることを特徴とする。

(もっと読む)

液晶表示装置、及び当該液晶表示装置を具備する電子機器

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】表示部に複数の画素を有し、複数のフレーム期間で表示を行う液晶表示装置であって、フレーム期間は、書き込み期間及び保持期間を有し、書き込み期間において、複数の画素のそれぞれに、画像信号を入力した後、保持期間において、複数の画素が有するトランジスタをオフ状態にして、少なくとも30秒間、画像信号を保持させる。画素は、酸化物半導体層でなる半導体層を具備し、酸化物半導体層は、キャリア濃度が1×1014/cm3未満である。

(もっと読む)

成膜方法および半導体装置

【課題】スパッタ法により、酸化物半導体膜上に薄膜を成膜する際に、酸化物半導体膜のプラズマダメージを膜面内均一性良く抑制して成膜する。

【解決手段】基板B上に成膜された、Inと、Ga,Zn,Mg,Al,Sn,Sb,CdおよびGeからなる群より選ばれる少なくとも1種の元素とを含む酸化物半導体膜1上に、基板BとターゲットTとを対向させて、プラズマを用いるスパッタ法によりターゲットTの構成元素を含む薄膜2を形成する成膜方法において、薄膜2の成膜時のプラズマ中のプラズマ電位Vs(V)と、基板Bの基板電位Vsub(V)との電位差を0V超20V以下とする。

(もっと読む)

液晶表示装置、及び当該液晶表示装置を具備する電子機器

【課題】低消費電力化できる液晶表示装置を提供することを課題の一とする。

【解決手段】駆動回路部及び画素部を有する表示パネルと、駆動回路部を駆動する制御信号及び画素部に供給する画像信号を生成するための信号生成回路と、画像信号をフレーム期間毎に記憶する記憶回路と、記憶回路でフレーム期間毎に記憶された画像信号のうち、連続するフレーム期間の画像信号の差分を検出する比較回路と、比較回路で差分を検出した際に連続するフレーム期間の画像信号を選択して出力する選択回路と、比較回路で差分を検出した際に制御信号及び選択回路より出力される画像信号の駆動回路部への供給を行い、比較回路で差分を検出しない際に制御信号を駆動回路部への供給を停止する表示制御回路と、を有する。

(もっと読む)

表示装置、及び表示装置を有する電子機器

【課題】消費電力が抑制された表示装置を提供することを課題の一とする。また、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。また、暗所でも長時間の利用が可能な、消費電力が抑制された自発光型の表示装置を提供することを課題の一とする。

【解決手段】高純度化された酸化物半導体を用いた薄膜トランジスタで回路を構成し、画素が一定の状態(映像信号が書き込まれた状態)を保持することを可能とする。その結果、静止画を表示する場合にも安定した動作が容易になる。また、駆動回路の動作間隔を長くできるため、表示装置の消費電力を低減できる。また、自発光型の表示装置の画素部に蓄光材料を適用し、発光素子の光を蓄えれば、暗所でも長時間の利用が可能になる。

(もっと読む)

半導体装置及びその作製方法

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体膜中の水分または水素などの不純物を低減するために、酸化物半導体膜を形成した後、酸化物半導体膜が露出した状態で第1の加熱処理を行う。次いで、酸化物半導体膜中の水分、または水素などの不純物をさらに低減するために、イオン注入法またはイオンドーピング法などを用いて、酸化物半導体膜に酸素を添加した後、再び、酸化物半導体膜が露出した状態で第2の加熱処理を行う。

(もっと読む)

201 - 220 / 975

[ Back to top ]