Fターム[5F110HM04]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 平面形状 (975)

Fターム[5F110HM04]に分類される特許

141 - 160 / 975

薄膜トランジスタおよび画像表示装置

【課題】ホールの多数発生を抑制し、かつリーク電流の増大を抑制することができる薄膜トランジスタを提供する。

【解決手段】本発明に係る薄膜トランジスタでは、半導体層12は、平面視において、ゲート電極2の端辺部2A,2Bからソース電極7およびドレイン電極8が引き出された部分において、ゲート電極2から外側に延在する延在部P1,P2,P3を有している。また、平面視において、ソース電極7とゲート電極2の端辺部2A,2Bとが交差する部分L1,L2は、チャネル形成領域13に接するソース電極7の部分LSと、チャネル長方向Yにおいて重ならない。さらに、平面視において、ドレイン電極8とゲート電極2の端辺部2Bとが交差する部分L3は、チャネル形成領域13に接するドレイン電極8の部分LDと、チャネル長方向Yにおいて重ならない。

(もっと読む)

電子機器

【課題】配線の凹凸差を緩和することが可能な構造の半導体装置を提供することを課題と

する。

【解決手段】第1の導電層と、第2の導電層と、第1の導電層及び第2の導電層の間に形

成されると共に、接続孔を有する絶縁層と、第1の導電層及び第2の導電層に接続すると

共に、少なくとも端部の一部が接続孔の内側に形成される第3の導電層と、を有する半導

体装置である。第2の導電層及び第3の導電層が接続する接続孔付近において、第3の導

電層が第1の絶縁層を介して第2の導電層に重畳せず、第3の導電層の端部が第1の絶縁

層上に形成されない。このため、第3の導電層の凹凸を低減することが可能である。

(もっと読む)

発光表示装置の作製方法

【課題】トランジスタの作製工程を簡略化し、フォトマスクの枚数を従来よりも少なくするだけでなく、新たな工程を増やすことなく発光表示装置を作製することを目的とする。

【解決手段】トランジスタを構成する半導体層に真性または実質的に真性な高抵抗の酸化物半導体を使用することによって、個々のトランジスタに対して半導体層を島状に加工する工程を省くことができる。半導体層または半導体層の上層に形成した絶縁層を開口する工程において該半導体層の不要な部分を同時にエッチングし、フォトリソグラフィ工程を削減する。

(もっと読む)

半導体装置、発光装置

【課題】信頼性の優れた酸化物半導体を用いた半導体装置を提供する。又は、信頼性の優れた酸化物半導体を用いた発光装置を提供する。

【解決手段】酸化物半導体を用いた半導体素子と共に封止される第2の電極は、その活性が損なわれ難い。活性な第2の電極と半導体装置に残存および/又は装置外から浸入する水分が反応して生じる水素イオンおよび/又は水素分子が、酸化物半導体のキャリア濃度を高め、半導体装置の信頼性を損なう原因となる。一方の面を有機層と接する第2の電極の他方の面の側に、水素イオンおよび/又は水素分子の吸着層を設ければよい。また、第2の電極に水素イオンおよび/又は水素分子が透過する開口部を設ければよい。

(もっと読む)

アレイ基板およびその製造方法、並びに液晶ディスプレー

【課題】ソース・ドレイン電極と別体に形成された拡張導電部によって、TFTスイッチング素子の有効チャネル長を短くする。

【解決手段】アレイ基板であって、ベース基板を有し、ベース基板に縦横に交差するデータラインとゲートラインが形成されてマトリックス状に配列する複数の画素ユニットが画成され、各画素ユニットにスイッチング素子が設置される。各スイッチング素子は、ゲート電極、活性層、ソース電極およびドレイン電極と、拡張導電部とを有し、前記ソース電極と前記ドレイン電極の前記活性層に接触する端部は対向してチャネル領域を定義し、前記拡張導電部は、前記ソース電極または前記ドレイン電極に隣接して電気的に接触し、前記拡張導電部の端部は、前記拡張導電部に接触するソース電極またはドレイン電極を超え、前記チャネル領域内に延び、少なくとも前記チャネル領域内で前記活性層に接触する。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタ

【課題】更なるスイッチング動作の高速化を図ることが可能な構造の横型IGBTを提供する。

【解決手段】コレクタ電極12がp+型領域4aに対してオーミック接触させられ、かつ、p型領域4bに対してショットキー接触させられるようにする。具体的には、コレクタ電極12とp型領域4bとの接触部位が確実にショットキー接触となるように、p型領域4bの表面上にバリア金属12aを配置する。これにより、コレクタ側からのホールの注入を抑制して低注入効率となるようにでき、ライフタイム制御を行わなくてもスイッチング動作を更に高速化することが可能な構造の横型IGBTとすることができる。

(もっと読む)

トランジスタ、液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するための工程を省略し、ゲート電極を形成する工程(同一層で形成される配線を含む)、ソース電極及びドレイン電極を形成する工程(同一層で形成される配線を含む)、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。配線の形状及び電位を工夫することで、寄生チャネルの形成を防ぐ。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 製造工程を単純化すると同時に、良好な画質を確保できる薄膜トランジスタ表示板を提供することである。また、本発明の他の目的は、画素の開口率を向上することができる薄膜トランジスタ表示板を提供することである。

【解決手段】 本発明の実施形態による薄膜トランジスタ表示板は、基板上に形成されているゲート線と、ゲート線上に形成されているゲート絶縁膜と、ゲート絶縁膜上に形成されている第1半導体と、少なくとも一部分の第1半導体上に形成されているデータ線及びドレイン電極と、ゲート絶縁膜上に形成されている蓄積導電体と、データ線、ドレイン電極及び蓄積導電体上に形成されている第1保護膜と、第1保護膜上に形成され、蓄積導電体上に位置した開口部を有する第2保護膜と、第2保護膜上に形成され、ドレイン電極に接続され、開口部で蓄積導電体と重なる画素電極とを備えることを特徴とする薄膜トランジスタ表示板。

(もっと読む)

液晶表示装置

【課題】IPS方式の液晶表示装置の開口率を向上させることが可能な技術を提供することである。

【解決手段】

ドレイン線と、ゲート線と、共通電極と、線状の画素電極と、薄膜トランジスタとを有する液晶表示装置であって、前記ドレイン線は、同一の画素行内で隣接する2つの画素毎に1本形成され、前記ゲート線は、同一の画素行内で、同一のドレイン線に接続される前記画素の内で、一方の画素に接続される第1のゲート線と、他方の画素に接続される第2のゲート線からなり、前記画素電極は、前記共通電極との重畳領域において、前記第1の方向からプラス方向に傾斜した第1の線状電極と、前記第1の方向からマイナス方向に傾斜した第2の線状電極とからなり、前記画素毎に、前記第1の線状電極の領域と前記第2の線状電極の領域との間の領域に、前記第1及び第2のゲート線並びに前記薄膜トランジスタとが形成されてなる液晶表示装置である。

(もっと読む)

エッチング方法及び半導体装置の作製方法

【課題】結晶性半導体膜に対する非晶質半導体膜のエッチング選択比が高いエッチング方法を提供する。

【解決手段】結晶性半導体膜上に非晶質半導体膜が設けられた積層半導体膜の一部に対して、Br系ガスと、F系ガスと、酸素ガスの混合ガスを用いてエッチングを行い、前記積層半導体膜に設けられた前記結晶性半導体膜の一部を露出させる。このようにエッチングを行うことで、露出された部分の膜減りを抑えることができる。更には、当該エッチング方法を薄膜トランジスタのバックチャネル部を形成するエッチングに採用することで、当該薄膜トランジスタの電気的特性を良好なものとすることができる。該薄膜トランジスタ上には絶縁層が設けられていることが好ましい。

(もっと読む)

液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】半導体層205のエッチングと、画素電極210とドレイン電極206bを接続するためのコンタクトホール208の形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

非導電性ナノワイヤー及びその製造方法

【課題】有機モット絶縁体である非導電性ナノワイヤー、製造方法及びそれを用いたトランジスタを提供する。

【解決手段】有機モット絶縁体となる原料を用い、電極の形状や印加電圧を所定の条件とした電解法により、有機モット絶縁体である非導電性ナノワイヤーを製造する。この方法によれば微細な非導電性ナノワイヤーを効果的に得られる。また、この非導電性ナノワイヤーを用いれば、効果的にトランジスタを製造できる。この態様のトランジスタ21は、ゲート電極26、絶縁層25、及びソース電極22、ドレイン電極23及び非導電性ナノワイヤー24の順に搭載されている。

(もっと読む)

発光表示装置の作製方法

【課題】トランジスタの作製工程を簡略化し、フォトマスクの枚数を従来よりも少なくするだけでなく、新たな工程を増やすことなく発光表示装置を作製することを目的とする。

【解決手段】トランジスタを構成する半導体層に真性または実質的に真性な高抵抗の酸化物半導体を使用することによって、個々のトランジスタに対して半導体層を島状に加工する工程を省くことができる。半導体層の上層に形成した絶縁層を開口する工程において該半導体層の不要な部分を同時にエッチングし、フォトリソグラフィ工程を削減する。

(もっと読む)

薄膜トランジスタアレイ及び画像表示装置並びに薄膜トランジスタアレイの製造方法

【課題】生産性が良く、低コストに、開口面積の大きい薄膜トランジスタアレイ、及びそれを用いた画像表示装置を作製することができる薄膜トランジスタアレイを提供する。

【解決手段】半導体層と、半導体層に離間して設けられたソース電極及びドレイン電極と、ゲート絶縁層を介して半導体層に離間して配置されたゲート電極とを有する表示スイッチング用の薄膜トランジスタを備えた画素が絶縁基板上に複数形成された薄膜トランジスタアレイにおいて、複数の画素100は互いに隣接して格子状に配置され、この複数の画素100のうち互いに隣接する4つの画素100を一単位とし当該一単位の中心部分あに各画素100の薄膜トランジスタ1001が集中して配置される構成にした。

(もっと読む)

半導体装置

【課題】裏面に対する各種プロセスを必要としない簡素な構造の半導体装置を提供する。

【解決手段】活性層2に対して埋込絶縁膜4との境界部分にn+型埋込領域6が形成されているSOI基板5を用いて、素子領域8と配線引出部9との間にトレンチ分離部11を配置し、トレンチ分離部11をn-型ドリフト層7と同じもしくはそれより深く、かつ、埋込絶縁膜4から離間するように形成する。このような構成とすれば、SOI基板5に対して予め形成しておけるn+型埋込領域6を介して行うことができる。このため、高耐圧MOSFET1の素子領域8と配線引出部9との電気的な接続を裏面電極などを備える必要がなく、裏面に対する各種プロセスを必要としない簡素な構造の半導体装置により、層間絶縁膜18に大きな電位差が掛かることを抑制できる。また、電位分布が不均一になることを防止でき、高耐圧MOSFET1の耐圧低下を抑制することも可能となる。

(もっと読む)

有機半導体化合物

【課題】高い電荷移動度を有する新規な化合物を提供する。

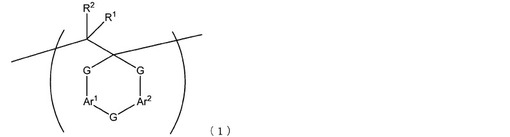

【解決手段】下記式(1)で表される構造単位を連続して2個以上有する化合物。

【化1】

(式(1)中、Ar1およびAr2はそれぞれ置換基を有してもよい2価の芳香族基であって、Ar1およびAr2のうちの少なくとも一方は置換基を有してもよい2価の複素環基である。Ar1とAr2とは同一でも異なっていてもよい。Gは直接結合または連結基であり、複数個存在するGは互いに同一でも異なっていてもよい。R1およびR2は水素原子または、置換基を有してもよい炭素数が1〜20の1価の炭化水素基である。R1とR2とは同一でも異なっていてもよい。)

(もっと読む)

半導体装置

【課題】さらなる耐圧特性の向上が図られる半導体装置を提供する。

【解決手段】半導体基板1の主表面上に、相対的に厚みの薄い部分3aと厚い部分3bとを含む誘電体部3を介在させてN-半導体層2が形成されている。N-半導体層2の所定の領域では、N型不純物領域5とP型不純物領域4が形成されている。N型不純物領域5とN-半導体層2とによって挟まれたP型不純物領域4の部分の表面上にゲート電極9が形成されている。P型不純物領域4から距離を隔てられたN-半導体層2の所定の領域では、P型不純物領域6が形成されている。N-半導体層2の表面から誘電体部3に達するように、空乏層阻止部として、N-半導体層2の不純物濃度よりも高い不純物濃度を有するN型不純物領域13が形成されている。

(もっと読む)

ボトムゲート型薄膜トランジスタ

【課題】伝達特性のサブスレッショルド領域における形状変化を低減したボトムゲート型薄膜トランジスタを提供する。

【解決手段】基板の上に、ゲート電極層と、ゲート絶縁層と、チャネル領域、ソース領域及びドレイン領域が同一の層で形成され、かつソース領域とドレイン領域がチャネル領域を介して設けられた酸化物半導体層と、がこの順で積層されて形成され、ソース領域及びドレイン領域の各々における、幅方向の端部の、チャネル領域に近い側の隅部から少なくとも一部の領域が、該端部と同じ側のチャネル領域の端部よりも内側に位置していることを特徴とするボトムゲート型薄膜トランジスタ。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

表示装置

【課題】画素部の薄膜トランジスタにおけるゲート・ソース間容量のばらつきを抑制することが可能な技術を提供する。

【解決手段】画素の領域毎に形成される画素電極PXと、画素電極を駆動する薄膜トランジスタとを備える表示装置において、薄膜トランジスタは、対角位置に形成される第1の角部B及び第2の角部Cと、前記第1の角部Bが形成される第1の辺と前記第2の角部Cが形成される第2の辺とを共有する第3の角部とを有し、ゲート絶縁膜を介して前記ゲート線GLに接続されるゲート電極と重畳して形成される半導体層ASと、前記ドレイン線DLからその一部が延在して形成され、前記第3の角部と重畳されるドレイン電極DTと、一端が前記第1の角部Bに重畳して形成され、他端が前記画素電極と接続される第1のソース電極ST1と、一端が前記第2の角部Cと重畳して形成され、他端が前記画素電極PXと接続される第2のソース電極ST2と、を有する。

(もっと読む)

141 - 160 / 975

[ Back to top ]