Fターム[5F110HM04]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 平面形状 (975)

Fターム[5F110HM04]に分類される特許

81 - 100 / 975

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく

作製することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層、ソース領域及びドレイン領域を酸化物半

導体層とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体層

の純度を高め、不純物である水分などを低減する加熱処理(脱水化または脱水素化のため

の加熱処理)を行う。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

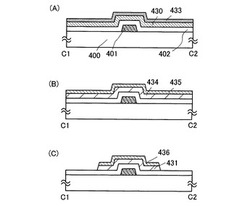

半導体装置

【課題】信頼性の高い、酸化物半導体を有する半導体装置。

【解決手段】酸化物半導体層は、ソース電極と重なる第1の領域と、ドレイン電極と重なる第2の領域と、ソース電極及びドレイン電極と重ならない第3の領域と、を有し、記第3の領域における酸化物半導体層の膜厚は、第1の領域及び第2の領域における酸化物半導体層の膜厚よりも小さく、第3の領域における酸化物半導体層の一端部は、第1のテーパを有し、記第3の領域における酸化物半導体層の他端部は、第2のテーパを有し、ソース電極の端部は、第3のテーパを有し、ドレイン電極の端部は、第4のテーパを有し、第1のテーパと、第3のテーパとは連続した形状を有し、第2のテーパと、第4のテーパとは連続した形状を有する半導体装置である。

(もっと読む)

シリコン・オン・インシュレータ内に形成された金属酸化膜半導体デバイス

【課題】デバイスの破壊電圧を大きく低下させずにLDMOSデバイスのオン抵抗を減少可能にすること。

【解決手段】半導体デバイスが、第1導電型の基板、基板の少なくとも一部分上に形成された絶縁層、および絶縁層の少なくとも一部分上に形成された第2導電型のエピタキシャル層を備える。第1、第2導電型のソース/ドレイン領域が、エピタキシャル層内でその上面に近接して形成され、第1、第2ソース/ドレイン領域は互いに横に間隔を置いて設置される。ゲートは、エピタキシャル層の上でその上面に近接して、少なくとも部分的に第1および第2ソース/ドレイン領域の間に形成される。このデバイスはさらに、エピタキシャル層と、絶縁層を貫通して形成され、基板、第1ソース/ドレイン領域、およびエピタキシャル層と直接に電気的に接続するように構成された第1のソース/ドレイン接点と、エピタキシャル層を貫通して形成され、第2ソース/ドレイン領域に直接に電気的に接続できるように構成された第2ソース/ドレイン接点とを備える。

(もっと読む)

有機素子の製造方法、有機分子結晶層の接合方法、細線状導電体の製造方法、有機素子および細線状導電体

【課題】電極に対して有機分子結晶層を配向制御して接合することができる有機分子結晶層の接合方法およびこの接合方法を利用した有機素子の製造方法を提供する。

【解決手段】絶縁性基体11上に電極12およびこの電極12と接合する芳香族化合物からなる有機分子結晶層13を形成する場合に、電極12の側面12aの絶縁性基体11の主面に対する傾斜角度を制御することにより、有機分子結晶層13の電極12に対する配向を制御する。電極12の側面を傾斜角度が互いに異なる複数の面により形成するようにしてもよい。

(もっと読む)

発光装置の作製方法

【課題】微細な配線パターンを備えた発光装置の作製方法の提供。

【解決手段】Inと、Gaと、Znとを有する酸化物半導体層を形成し、酸化物半導体層上に第1の導体パターンを形成し、第1の導体パターンより微細な第2の導体パターンを形成し、前記第2の導体パターンと電気的に接続する発光素子を形成する発光装置の作製方法であって、第2の導体パターンは、酸化物半導体層を横断する。

(もっと読む)

薄膜トランジスタアレイ、表示装置、およびそれらの製造方法

【課題】本発明は、開口率を大きくする必要がなく、印刷に適し、複数画素を用いずに面積階調できる薄膜トランジスタアレイ、表示装置、および薄膜トランジスタアレイの製造方法を提供する。

【解決手段】画素の有効領域の幅をA、画素の有効領域のネガパターンの幅をBとしたとき、幅Bが幅Aよりも大きな薄膜トランジスタとする。あるいは、対向電極と画素電極の距離をCとしたとき、距離Cが幅Bの4分の1以上B以下である表示装置とする。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

半導体装置

【課題】トランジスタのサイズを縮小しつつ、良好なスイッチング特性を有する半導体装置を提供する。

【解決手段】一対の第1の突起と、一対の第1の突起の間に設けられる第2の突起とを有するゲート電極と、ゲート電極を覆うゲート絶縁膜と、ゲート絶縁膜と接して、且つ一対の第1の突起および第2の突起に重畳する半導体膜と、半導体膜と接して、且つ一対の第1の突起と重畳する一対の電極と、を有し、半導体膜の側端は、半導体膜のチャネル幅方向において、一対の第1の突起の頂面より外側であり、一対の電極の側端は、半導体膜のチャネル幅方向において、一対の第1の突起の頂面より外側である半導体装置である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気的特性の良好なトランジスタ及びその作製方法を提供することを課題の一とする。

【解決手段】基板上に酸化物半導体膜及び絶縁膜を有し、酸化物半導体膜の端部は絶縁膜と接しており、酸化物半導体膜は、チャネル形成領域と、チャネル形成領域を挟んで形成されたドーパントを含む領域とを含み、酸化物半導体膜上に接して形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、サイドウォール絶縁膜を有するゲート電極と、サイドウォール絶縁膜、酸化物半導体膜、および絶縁膜に接して形成されたソース電極およびドレイン電極とを有する半導体装置である。

(もっと読む)

半導体装置及び電子機器

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導

体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作

製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって

形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチ

ング工程において、第1のエッチング工程は、エッチングガスによるドライエッチングを

用い、第2のエッチング工程はエッチング液によるウエットエッチングを用いる。

(もっと読む)

半導体回路および論理回路

【課題】論理回路をできるだけ小さな回路面積で形成可能な半導体回路を提供する。

【解決手段】半導体回路は、第1および第2のトランジスタで共有されるゲート領域と、ゲート領域に接するように配置されるゲート絶縁膜と、ゲート絶縁膜に接するように配置される半導体層と、を備える。半導体層は、ゲート領域に対向するように配置され、第1のトランジスタのチャネルとして用いられる反転層形成領域と、反転層形成領域に沿って、あるいは反転層形成領域と交差するように形成され、第2のトランジスタのチャネルとして用いられる導通路形成領域と、を有する。導通路形成領域は、ゲート領域が所定の電圧範囲のときには、反転層形成領域から伸びる空乏層により遮断される。

(もっと読む)

電界効果型トランジスタ、電界効果型トランジスタの製造方法、固体撮像装置、及び電子機器

【課題】 ゲート電極の微細化が可能な電界効果型トランジスタを提供する。

【解決手段】 本開示に係る電界効果型トランジスタは、基板10と、基板10上に形成され、フィン領域13と該フィン領域13の両端にそれぞれ形成されるソース領域14とドレイン領域15とを有する半導体層と、フィン領域13の少なくとも2面の一部と接する凸部171を有するゲート電極17と、を備える。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】薄膜トランジスタは、第1方向に形成された少なくとも1本のゲートラインを含むゲート11と、ゲート上に形成されたゲート絶縁層12と、ゲート絶縁層12上に形成された少なくとも1つのソース13及びドレイン14と、を含み、ソース13及びドレイン14のうち少なくともいずれか一つは、延長部分13b、14bを含み、延長部分13b、14bは、少なくとも1本のゲートラインと平行するように、第1方向に形成される。ゲート11は、ライン状に均一厚を有し、その側面と上面との間に曲面を含み、1本または2本以上のゲートラインを含む形態となる。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、容易に素子分離もできる半導体装置を提供する。

【解決手段】第1絶縁膜2の上の第1導電型の第1半導体層3の表面を含む上部に設けられた第2導電型の第1半導体領域7と、第1半導体領域7の上部に設けられた第1導電型の第2半導体領域8と、側面が第1半導体層3と第1半導体領域7と第2半導体領域8に接する第1トレンチ4と、第1トレンチ4の側面に沿って設けられたゲート絶縁膜5と、第1トレンチ4内に埋め込まれたゲート電極6と、第1半導体領域7と第1トレンチ4から離れて第1半導体層3の上部に設けられた第1導電型の第3半導体領域9と、側面が第3半導体領域9に接し第3半導体領域9に対して第1半導体領域7の反対側に配置された第2トレンチ15と、第2トレンチ15の側面に沿って設けられた素子分離絶縁膜10と、第2トレンチ15内に埋め込まれたポリシリコン埋め込み領域11とを有する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

縦型電界効果トランジスタとその製造方法及び電子機器

【課題】縦型電界効果トランジスタとその製造方法及び電子機器において、チャネルの下地の材料の選択の幅を広げると共に、縦型電界効果トランジスタのオン抵抗が上昇するのを抑制すること。

【解決手段】基材1と、基材1の上に形成されたソース電極2と、基材1の上に形成され、ソース電極2に重なる開口12を備えた第1の絶縁膜3と、開口12の横の第1の絶縁膜3の上に形成されたゲート電極6と、開口12の側面に形成されたゲート絶縁膜16と、第1の絶縁膜3の上に形成され、開口12に繋がる凹部8aを備えた第2の絶縁膜8と、開口12と凹部8aのそれぞれの内側と第2の絶縁膜8の上に形成され、酸化物半導体を材料とするチャネル17と、凹部8aの横の前記チャネル17の上に形成されたドレイン電極19とを有する縦型電界効果トランジスタによる。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

電子装置およびその製造方法

【課題】グラフェンシートを使い、大電流をオンオフできる電子装置を提供する。

【解決手段】電子装置は基板と、前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極からドレイン電極へのキャリアの流れを横切って形成された、複数の開口部よりなる開口部列と、を備え、前記各々の開口部では前記グラフェンシートから4個以上の炭素原子が除去されており、前記各々の開口部は、他の炭素原子に結合していない結合手を有する炭素原子を二個以上含む少なくとも5個の炭素原子からなるジグザグ形状の端部により画成されている。

(もっと読む)

81 - 100 / 975

[ Back to top ]