Fターム[5F110HM04]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | 形状 (2,461) | 平面形状 (975)

Fターム[5F110HM04]に分類される特許

101 - 120 / 975

電子装置およびその製造方法

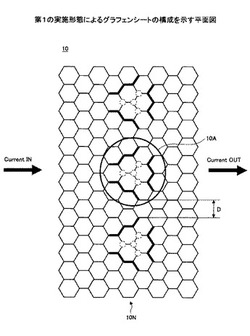

【課題】グラフェンシートを使い、大電流をオンオフできる電子装置を提供する。

【解決手段】電子装置は基板と、前記基板上にゲート絶縁膜を介して形成されたグラフェンシートと、前記グラフェンシートの一端に形成されたソース電極と、前記グラフェンシートの他端に形成されたドレイン電極と、前記グラフェンシートに前記ソース領域とドレイン領域との間でゲート電圧を印加するゲート電極と、前記グラフェンシートに前記ソース電極とドレイン電極の間において、前記ソース電極からドレイン電極へのキャリアの流れを横切って形成された、複数の開口部よりなる開口部列と、を備え、前記各々の開口部では前記グラフェンシートから4個以上の炭素原子が除去されており、前記各々の開口部は、他の炭素原子に結合していない結合手を有する炭素原子を二個以上含む少なくとも5個の炭素原子からなるジグザグ形状の端部により画成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製に用いるフォトリソグラフィ工程を従来よりも少なくし、且つ、信頼性の高い半導体装置を提供する。

【解決手段】第1の基板上に酸化物半導体層を有するトランジスタを含む回路と、当該第1の基板とシール材で固定された第2の基板とを有し、当該シール材、当該第1の基板、及び当該第2の基板で囲まれる閉空間は、減圧状態、或いは乾燥空気を充填する半導体装置に関する。当該シール材は、少なくとも前記トランジスタを囲み、閉じられたパターン形状を有する。また当該回路は、酸化物半導体層を有するトランジスタを含む駆動回路である。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、電流検出の直線性を向上させられ、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】センスセルの両側にメインセルを配置し、センスセルのエミッタがメインセルのエミッタに挟まれた構造にする。これにより、センスセルのエミッタに流れる電流密度とセンスセルのエミッタに流れる電流密度とを近づけることができ、ミラー比がメインセルとセンスセルそれぞれのエミッタの長手方向における長さの比に近くなる。また、センスセルのエミッタに流れる電流密度とセンスセルのエミッタに流れる電流密度とを近づけられるため、スイッチング時や大電流が流れる時に流れる単位面積当たりの電流量がメインセル側と比較してセンスセル側において大きくなることを抑制できる。このため、電流の偏りを抑制することができ、破壊耐量を向上させることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製及び表示装置の作製に用いるフォトマスクの枚数を従来よりも少なくすることを課題の一とする。

【解決手段】ゲート電極を形成する工程と、島状半導体層を形成するための工程を、1回のフォトリソグラフィ工程で行い、平坦化絶縁層を形成した後、コンタクトホールを形成する工程を1回のフォトリソグラフィ工程で行い、ソース電極及びドレイン電極を形成する工程と画素電極を形成する工程を1回のフォトリソグラフィ工程で行い、合計3回のフォトリソグラフィ工程で表示装置を作製する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】オフ電流の極めて小さい半導体装置を提供する。また、該半導体装置を適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上にゲート電極を有し、ゲート電極上にゲート絶縁層を有し、ゲート絶縁層上に酸化物半導体層を有し、酸化物半導体層上にソース電極及びドレイン電極を有し、酸化物半導体層の外縁のうちソース電極の外縁からドレイン電極の外縁に達する部分の長さを、チャネル長の3倍以上、好ましくは5倍以上とする。また、熱処理により、ゲート絶縁層から酸化物半導体層へ酸素を供給する。また、酸化物半導体層を選択的にエッチングした後、絶縁層を成膜する。

(もっと読む)

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いるトランジスタにおいて、電気特性の良好なトランジスタ及びその作製方法を提供する。

【解決手段】基板上に第1の酸化絶縁膜を形成し、該第1の酸化絶縁膜上に第1の酸化物半導体膜を形成した後、加熱処理を行い、第1の酸化物半導体膜に含まれる水素を脱離させつつ、第1の酸化絶縁膜に含まれる酸素の一部を第1の酸化物半導体膜に拡散させ、水素濃度及び酸素欠陥を低減させた第2の酸化物半導体膜を形成する。次に、第2の酸化物半導体膜を選択的にエッチングして、第3の酸化物半導体膜を形成した後、第2の酸化絶縁膜を形成して、当該第2の酸化絶縁膜を選択的にエッチングして、第3の酸化物半導体膜の端部を覆う保護膜を形成する。この後、第3の酸化物半導体膜及び保護膜上に一対の電極、ゲート絶縁膜、及びゲート電極を形成する。

(もっと読む)

半導体装置

【課題】正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置を提供する。

【解決手段】メインセルとセンスセルとをトレンチ分離構造1dによって絶縁分離する。これにより、メインセルのコレクタに対して100V以上の高電圧が印加されても、それに起因するノイズが電流検出用の出力端子に誘起されないようにできる。また、センスセルのエミッタ電位がセンス抵抗Rsに流れる電流によって上昇しても、メインセルのエミッタと電気的に完全に分離されているため、寄生トランジスタが動作することもない。勿論、抵抗層14から発生させられたノイズが電流検出用の出力端子に誘起されることも抑制できる。したがって、正確にメインセルに流れる電流を検出することができると共に、高い電圧が用いられる場合でもその影響を受け難い半導体装置とすることが可能となる。

(もっと読む)

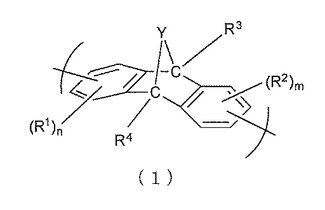

化合物及びそれを含有する薄膜

【課題】有機トランジスタの有機半導体層に含有させるのに有用なπ共役構造を有する化合物及びそれを用いた薄膜、及び該π共役構造を含む化合物を得るための前駆体である化合物を提供することである。

【解決手段】式

[式中、R1及びR2は、それぞれ独立に、置換基を表す。R3及びR4は、それぞれ独立に、水素原子又は置換基を表す。n及びmは、それぞれ独立に、0〜3の整数を表す。Yは、2価の基を表す。R1が複数個ある場合、それらは同一でも相異なってもよい。R2が複数個ある場合、それらは同一でも相異なってもよい。]

で表される構造単位と;π共役構造を有する構造単位とを;有する化合物。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明は、より寄生容量の少ない素子の実現が可能な素子分離構造を有する半導体装置およびその製造方法を提供することにある。

【解決手段】 SOI基板上に形成される半導体装置は、素子分離領域に形成される素子分離溝(空洞)17と、半導体層11と支持基板13の間に介在する埋め込み絶縁層の一部に素子分離溝(空洞)17に接する空洞領域20を有する。

【効果】寄生容量を低減でき、また、素子の耐圧を高めることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル形成時のひずみ緩和の抑制を可能にすると共に、更にひずみを印加することを可能にする。

【解決手段】基板1と、基板上に形成されひずみを有する第1半導体層3と、第1半導体層3上に離間して設けられ、第1半導体層3と格子定数が異なる第2および第3半導体層8と、第2半導体層と第3半導体層8との間の第1半導体層3上に設けられたゲート絶縁膜4と、ゲート絶縁膜4上に設けられたゲート電極5と、を備え、第2半導体層および第3半導体層8直下の第1半導体層3の外表面領域をシリサイド3a、8aとする。

(もっと読む)

SOI型トランジスタ

【課題】DRAMメモリアレイに用いられるセミコンダクタ・オン・インシュレータ型トランジスタを提供する。

【解決手段】SOI型のトランジスタは、半導体物質層60(SOI層)と、この半導体物質層60の内部を通って走るゲート線65a,65b,66cと、このゲート線65a,65b,66cに沿ってソース拡散領域70a、70b、70cよりも遠くまで延びるドレイン拡散領域64と、このドレイン拡散領域64よりも上方にあるソース拡散領域70a、70b、70cと、ドレイン拡散領域64まで延びるドレインコンタクト79と、ソース拡散領域まで延びるソースコンタクトと、を備え、これらドレインコンタクト79及びソースコンタクトは、ゲート線65a,65b,66cと平行に走る平面内にある。

(もっと読む)

薄膜トランジスタ

【課題】寄生容量を小さくでき、応答速度低下を抑制することが可能なTFTを提供する。

【解決手段】基材110上に配設した有機半導体層150と、有機半導体層150と接触し、対向してチャネル領域を形成するソース電極120及びドレイン電極130と、有機半導体層150と絶縁層160を介して設けられるゲート電極140と、ソース電極120と導電接続するソース電極配線部125と、ドレイン電極130と導電接続するドレイン電極配線部135と、ゲート電極140と導電接続するゲート電極配線部145と、からなるTFT100であって、積層方向からみて、有機半導体層150が、ゲート電極140を含み、ゲート電極140が、ソース電極120とドレイン電極130とチャネル領域とからなる領域を含み、有機半導体層150の周縁でソース電極配線部125とドレイン電極配線部135との間にはゲート電極配線部145が配される。

(もっと読む)

表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い表示装置を提供する。消費電力が少なく、信頼性の高い表示装置を提供する。

【解決手段】トランジスタの、ゲート電極となる導電層、ゲート絶縁層となる絶縁層、半導体層、およびチャネル保護層となる絶縁層を連続して形成する。ゲート電極(同一層で形成される他の電極または配線を含む)と島状半導体層の形成を、一回のフォトリソグラフィ工程で行う。該フォトリソグラフィ工程と、コンタクトホールを形成するフォトリソグラフィ工程と、ソース電極及びドレイン電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程と、画素電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程の、4つのフォトリソグラフィ工程で表示装置を作製する。

(もっと読む)

酸化物半導体膜および半導体装置

【課題】より電気伝導度の安定した酸化物半導体膜を提供することを課題の一とする。また、当該酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供することを課題の一とする。

【解決手段】結晶性を有する領域を含み、当該結晶性を有する領域は、a−b面が膜表面に概略平行であり、c軸が膜表面に概略垂直である結晶よりなる酸化物半導体膜は、電気伝導度が安定しており、可視光や紫外光などの照射に対してもより電気的に安定な構造を有する。このような酸化物半導体膜をトランジスタに用いることによって、安定した電気的特性を有する、信頼性の高い半導体装置を提供することができる。

(もっと読む)

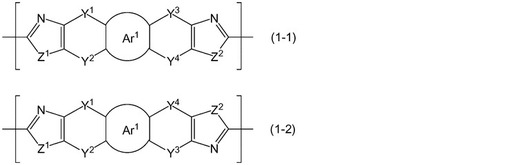

含窒素縮合環化合物、含窒素縮合環重合体、有機薄膜及び有機薄膜素子

【課題】優れた電子輸送性を有する有機n型半導体として利用可能な新規化合物及び新規重合体の提供。

【解決手段】式(1−1)及び式(1−2)で表される構造単位からなる群より選択される、含窒素縮合環化合物。

[式中、Ar1は、芳香環を示し、Y1及びY2のうちいずれか一方は、−C(=X1)−で表される基を示し、他方は、単結合を示し、Y3及びY4のうちいずれか一方は、−C(=X2)−で表される基を示し、他方は、単結合を示し、X1及びX2は、酸素原子等を示し、Z1及びZ2は、酸素原子等を示す。]

(もっと読む)

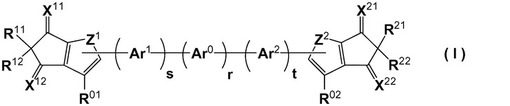

共役系化合物、並びにこれを用いた有機薄膜及び有機薄膜素子

【課題】電子輸送性に優れたn型半導体として利用可能であり、しかも溶剤への溶解性にも優れる共役系化合物の提供。

【解決手段】式(I)で表される共役系化合物。[式中、R01及びR02はアルカン骨格を含む1価の基。R11、R12、R21及びR22は水素原子、ハロゲン原子又は1価の基。X11、X12、X21及びX22は=O,=S又は=CA2(Aは水素原子、ハロゲン原子又は1価の基を示すが、その少なくとも1つは電子吸引性の基。)を示す。Z1及びZ2は−O−,−S−,−Se−,−Te−,−SO−等のいずれかの基を示す。Ar0、Ar1及びAr2は芳香族炭化水素基又は複素環基を示す。rは1〜6の整数、s及びtは0〜6の整数を示す。] (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

101 - 120 / 975

[ Back to top ]