Fターム[5F110HM19]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | ソース、ドレイン配線に工夫 (347)

Fターム[5F110HM19]に分類される特許

101 - 120 / 347

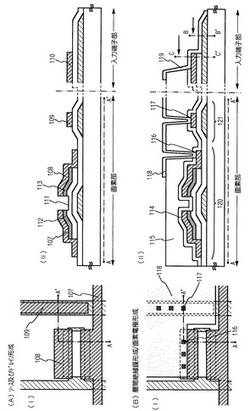

半導体装置の作製方法、半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置な

らびに半導体装置において、TFTを作製する工程数を削減して製造コストの低

減および歩留まりの向上を実現することを目的としている。

【解決手段】 基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶

縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と

、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部

に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲ

ート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層

とから形成されていることを特徴としている。このような構成とすることで、フ

ォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる

。

(もっと読む)

MIS電界効果トランジスタ及び半導体基板の製造方法

【課題】高温特性を改善した高集積、高速且つ高性能なMISFETを得ること。

【解決手段】半導体基板に絶縁膜を埋め込んだトレンチ素子分離領域を選択的に設け、この絶縁分離された半導体基板上に、半導体基板と同じ第1の半導体を、筒状構造を有して縦方向にエピタキシャル成長させ、この第1の半導体層に自己整合して、格子定数がやや大きい第2の半導体を内側面の横方向にエピタキシャル成長させることにより、第1の半導体層に歪みを加える。この第2の半導体層の上部内側面を除く内側面に接して絶縁膜を設け、この絶縁膜の側面間を空孔となし、この空孔に栓をするように、第2の半導体層の上部内側面間に導電膜を設ける。歪み半導体層の外側面にはゲート絶縁膜を介してゲート電極を設ける。歪み半導体層及び第2の半導体層の上部にはドレイン領域を設け、歪み半導体層及び第2の半導体層の下部且つ半導体基板の表面にはソース領域を設けておき、配線体をそれぞれの領域に接続した縦型のMISFETを構成すること。

(もっと読む)

表示装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一とする。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置において、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二種類の酸化物半導体層とを組み合わせて構成され、ゲート電極層と重なるチャネル形成領域となる半導体層上にチャネル保護層が設けられた逆スタガ型薄膜トランジスタが設けられた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続するパッド部が設けられている。

(もっと読む)

パネル構造体、パネル構造体を含む表示装置及びその製造方法

【課題】パネル構造体、パネル構造体を含む表示装置及びその製造方法を提供する。

【解決手段】パネル構造体、パネル構造体を含む表示装置及びその製造方法に係り、該パネル構造体の構成要素間連結のためのビアホールは、1回の工程で形成されうる。例えば、該パネル構造体で、トランジスタとそれと離隔された導電層との連結のためのビアホールは、1回の工程で形成されうる。

(もっと読む)

半導体装置およびその製造方法

【課題】 塗布技術や印刷技術を用いて形成した薄膜トランジスタを微細に形成し、さらに、ホトコンを低減することにより、高性能な薄膜トランジスタ、及びそれを用いた半導体装置を安価に提供すること。

【解決手段】 絶縁基板上に、ソース・ドレイン電極、ゲート絶縁膜、有機半導体層、ゲート電極の各部材が積層された薄膜トランジスタ、およびそのトランジスタを含む表示装置、ICタグ装置、センサー装置において、有機半導体層は塗布法もしくは印刷法で形成されており、ソース・ドレイン電極上の有機半導体層の概略パターン平面形状の少なくとも一部(少なくともチャネル長方向の端部)がソース・ドレイン電極上のパターン形状と自己整合的な形状である構成とした。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】ゲート絶縁層上に、ドレイン電極層またはソース電極層を形成した後、低抵抗な酸化物半導体層をソース領域またはドレイン領域として形成し、その上に半導体層として酸化物半導体膜を形成することを要旨とする。好ましくは、半導体層として酸素過剰酸化物半導体層を用い、ソース領域及びドレイン領域として酸素欠乏酸化物半導体層を用いる。

(もっと読む)

液晶表示装置用薄膜トランジスタ基板及びその製造方法

【課題】TFT用薄膜トランジスタ基板の製造工程を単純化する。

【解決手段】ゲート線及びゲート電極を含むゲート配線と、共通電極を含む共通配線とを絶縁基板の上に形成し、前記ゲート配線及び共通配線を覆うゲート絶縁膜を形成し、前記ゲート絶縁膜の上に半導体パターン、前記半導体パターンの上に接触層パターン、前記接触層の上にソース電極及びドレーン電極をそれぞれ形成し、前記ソース電極と連結されたデータ線を含むデータ配線とを形成し、前記ドレーン電極の一部以外の前記データ配線を覆う保護膜パターンを形成し、前記データ配線と異なる層に画素電極を形成する段階とを含み、前記ソース及びドレーン電極の分離は、前記ソース電極及びドレーン電極の間に位置する第1部分と前記第1部分より厚い第2部分と前記第1部分より薄い第3部分とを含む感光膜パターンを用いた写真エッチングによって行う液晶表示装置用薄膜トランジスタ基板の製造方法。

(もっと読む)

半導体装置、電気光学装置、およびこれを備えた電子機器

【課題】高速動作可能な半導体装置を低コストで提供する。

【解決手段】本発明の半導体装置は、TFT100Pと、上部電極303と下部電極302とを有する蓄積容量103と、TFT−下部電極間に形成された第1の層間絶縁膜(第1層間絶縁膜221)と、上部電極上に形成された第2の層間絶縁膜(第3層間絶縁膜223)と、第2の層間絶縁膜上に形成されたソース電極403及びドレイン電極(第1ドレイン電極402)とを含み、ソース電極は、第1、第2層間絶縁膜を貫通する第1のコンタクトホール551を介してTFTのソース領域に、ドレイン電極は、第1、第2層間絶縁膜を貫通する第2のコンタクトホール552を介してTFTのドレイン領域に接続され、下部電極は、第2層間絶縁膜を貫通する第3のコンタクトホール553を介してドレイン電極に接続されている。

(もっと読む)

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】半導体装置Sは、各第2領域R2の少なくとも一部の平坦な領域に互いに同じ厚みで形成された第1平坦化膜13と、各第1平坦化膜13の間にゲート電極8a,8bを覆うように設けられて第1平坦化膜13よりも研磨選択比が小さい材料により構成され、第1平坦化膜13の表面と面一になるように研磨されることにより第1平坦化膜13の表面に連続する平坦な表面を有する第2平坦化膜14とを備えている。基体層1の一部は、第1平坦化膜13又は第2平坦化膜14を介して剥離用物質がイオン注入されることにより形成された剥離層に沿って分離されている。

(もっと読む)

薄膜トランジスタ及び電気光学装置並びに電子機器

【課題】薄膜トランジスタにおいて、光リーク電流の発生を抑制しつつ、サイズの縮小化を図る。

【課題を解決するための手段】薄膜トランジスタは、基板(10)上に形成されており、チャネル領域(30a2)及びソースドレイン領域(30a1、30a3)を有する半導体層と、チャネル領域にゲート絶縁膜を介して対向配置されたゲート電極(30b)とを備える。基板は、薄膜トランジスタに電気的に接続された配線等のうち少なくとも一つが形成される主表面(12´´)、並びに該主表面に対して斜めに傾いた傾斜面(12´)を有し、半導体層のうち少なくとも前記チャネル領域は、傾斜面に形成されている。

(もっと読む)

電気光学装置及びその製造方法並びに電子機器

【課題】液晶パネル等の電気光学装置において、TFTにおける光リーク電流の発生を効率よく抑制しつつ、動作の安定化を図る。

【解決手段】電気光学装置は、基板(10)上に、チャネル領域、ソースドレイン領域及びLDD領域を有する半導体層(30a)と、チャネル領域に対向するゲート電極(30b)と、半導体層より上層側に積層され、少なくともチャネル領域及びLDD領域より広く形成された上側遮光膜(1)と、半導体層より下層側に積層され、少なくともチャネル領域及びLDD領域より広く形成された下側遮光膜(11)と、半導体層及び下側遮光膜間に積層され、少なくともLDD領域に重なる領域における膜厚よりソースドレイン領域に重なる領域における膜厚の方が小さくなるように形成された下側層間絶縁膜(12)とを備える。

(もっと読む)

縦型電界効果トランジスタを備える半導体装置及びその製造方法

【課題】縦型電界効果トランジスタを利用した半導体装置において、集積度を更に向上させること。

【解決手段】半導体装置1は、絶縁性基板10と、絶縁性基板10上に形成された第1導電型の第1半導体層21と、第1半導体層21上にソース及びドレインの一方が形成された第1導電型チャネルの第1縦型電界効果トランジスタNFETと、絶縁性基板10上に形成された第2導電型の第2半導体層22と、第2半導体層22上にソース及びドレインの一方が形成された第2導電型チャネルの第2縦型電界効果トランジスタPFETと、を備える。第1半導体層21と第2半導体層22は、直接接触している。

(もっと読む)

表示装置及びその製造方法

【課題】ボトムゲート構造を有する薄膜トランジスタを含む表示装置において、遮光層とゲート電極との間の寄生容量の発生を軽減しつつ、光リーク電流の発生の抑制を図ることが可能になる表示装置を提供すること。

【解決手段】表示装置は、半導体層への光の入射を抑制するための遮光層(40)と、第1絶縁膜(31)と、薄膜トランジスタのゲート電極(22)と、第2絶縁膜(32)と、半導体層(21)と、が順次積層された基板を含む。遮光層(40)は、ゲート電極(22)の少なくとも一部が遮光層(40)と第1絶縁膜(31)を介して重ならないようにして形成される。

(もっと読む)

アクティブマトリクス基板、ディスプレイパネル、表示装置およびアクティブマトリクス基板の製造方法

【課題】アクティブマトリクス基板の開口率と消費電力とを向上させる。

【解決手段】アクティブマトリクス基板101Aは、透明基板10と、透明基板10上に形成された配線(LG,LD,LP,L1,L2等)と、この配線(LG,LD,LP,L1,L2等)の少なくとも一部を覆う透明半導体層44と、配線(LG,LD,LP,L1,L2等)および透明半導体層44の少なくとも一部を覆う透明な絶縁膜と、を備える。配線(LG,LD,LP,L1,L2等)は、主配線としての第1メタル配線41Mと、これから分岐する副配線としての透明な配線(41,42,43等)と、を含む。主配線としての第1メタル配線41Mは、少なくとも一部が副配線としての配線(41,42,43等)よりも高い導電性を備えた材料を用いて形成される。

(もっと読む)

表示装置

【課題】非表示領域の周辺において、信号線の配置に占める面積を小さくできる表示装置の提供。

【解決手段】基板上に、一方向に並設される複数のゲート信号線と、前記一方向と交差する方向に並設される複数のドレイン信号線と、前記ゲート信号線とドレイン信号線とのうちの一方の信号線のそれぞれの間に前記一方の信号線に沿って配置される複数の共通信号線とを備え、共通信号線と交差して配置される接続配線に電気的に接続され、接続配線は、複数の共通信号線うち、仮想的にそのまま延長した場合でも非表示領域を横切ることなく配置されている第2の共通信号線に電気的に接続されている。

(もっと読む)

配線基板及び表示装置

【課題】配線抵抗を低減しながらも、その製造工程数を低減する。

【解決手段】複数の配線13の少なくとも一部は、金属ナノ粒子からなる第1導電層31と、少なくとも一部が第1導電層31に直接に積層された第2導電層32とにより構成され、第2導電層32は、第1導電層31に接触して設けられたバリア層33と、該バリア層33に直接に積層された金属層34とを有している。

(もっと読む)

薄膜トランジスタ及びその作製方法、並びに表示装置及びその作製方法

【課題】従来よりも少ないマスク数で作製する薄膜トランジスタ及び表示装置の作製方法を提供する。

【解決手段】第1の導電膜と、絶縁膜と、半導体膜と、不純物半導体膜と、第2の導電膜とを積層し、この上に3段階の厚さを有するレジストマスクを形成し、第1のエッチングを行って薄膜積層体を形成し、該薄膜積層体に対してサイドエッチングを伴う第2のエッチングを行ってゲート電極層を形成し、その後レジストマスクを後退させて半導体層、ソース電極及びドレイン電極層を形成することで、薄膜トランジスタを作製する。3段階の厚さを有するレジストマスクは、例えば、4階調のフォトマスクにより形成する。

(もっと読む)

液晶表示装置

【課題】高開口率化及び高精細化に対応した液晶表示装置を提供する。

【解決手段】複数の走査線12と、走査線を覆って形成した絶縁膜21と、各走査線12に交差する交差部13Dを有する複数の信号線13と、走査線と信号線とに隣接して配設した画素電極と、半導体層、ゲート絶縁膜、前記走査線に接続したゲート電極と、ドレイン電極14b及びソース電極14aの何れかで信号線に接続された一方の電極と、画素電極に接続されたドレイン電極及びソース電極の他方の電極と、ドレイン電極及びソース電極が信号線に沿う方向に直線状に配置された複数の薄膜トランジスタ14と、第1の重ね合わせ部17aが交差部13D上に重なり第2の重ね合わせ部17cが一方の電極上に重なり一方の電極と信号線とを接続する複数の中継電極17と、を具備し、中継電極の第1の重ね合せ部は走査線12の幅方向の両側端部12b、12cに対応する絶縁膜21の段差部13E,13Dを覆う長さを有する。

(もっと読む)

液晶表示パネル

【課題】表示品位に優れ、製品歩留まりの高い液晶表示パネルを提供する。

【解決手段】液晶表示パネルは、第1基板と、第2基板と、液晶層と、を備えている。第1基板は、走査線と、信号線と、スイッチング素子Wと、スイッチング素子に重なったコンタクトホール11hを有した第1絶縁層11と、共通電極ETと、コンタクトホールに形成され、スイッチング素子に電気的に接続された接続部13と、接続部に重なった他のコンタクトホール14hを有した第2絶縁層14と、他のコンタクトホールを介して接続部に電気的に接続された画素電極EPと、を備えている。

(もっと読む)

液晶表示装置用アレイ基板製造用のエッチングテープ

【課題】本発明は液晶表示装置用アレイ基板製造用のエッチングテープを提供する。

【解決手段】本発明のエッチングテープは、ベースシート及びベースシート上にゲルタイプのエッチング物質が塗布されて形成されたエッチング物質層を含む。このエッチングテープは、透明絶縁基板上にゲート電極、ストレージキャパシターの第1電極、ゲート配線を形成する段階、ゲート絶縁膜、アクティブ層、オーミック接触層、ソース電極及びドレーン電極を形成し、誘電体層及びストレージキャパシターの第2電極を形成し、データ配線を形成する段階、画素電極を形成し、ゲートパッド電極を形成し、データパッド電極を形成する段階、保護層を形成する段階及びゲートパッド電極上に形成された保護層とデータパッド電極上に形成された保護層をエッチングすることでコンタクトホールを形成する段階を含む液晶表示装置用アレイ基板の製造方法に利用される。

(もっと読む)

101 - 120 / 347

[ Back to top ]