Fターム[5F110HM19]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | ソース、ドレイン配線に工夫 (347)

Fターム[5F110HM19]に分類される特許

21 - 40 / 347

半導体記憶装置

【課題】動作速度の向上と面積の縮小を図る。

【解決手段】半導体記憶装置は、半導体基板100と、前記半導体基板上に形成され、データを記憶する複数のメモリセルが配置されたメモリセルアレイ部Aと、前記メモリセルアレイ部上に絶縁層を介して形成され、かつ、前記絶縁層および前記メモリセルアレイ部を貫通する孔106内に形成されて前記半導体基板に接続された単結晶半導体層109と、前記単結晶半導体層上に形成された回路部Bと、を具備し、前記メモリセルアレイ部上における前記単結晶半導体層の下部側は、上部側よりもGe濃度が高い。

(もっと読む)

半導体装置及びその製造方法

【課題】包囲型ゲート電極付きの歪みSOI構造のMISFETの提供

【解決手段】

半導体基板1上に第1の絶縁膜2が設けられ、第1の絶縁膜2上に第2の絶縁膜3が選択的に設けられ、第2の絶縁膜3上に設けられた第1の半導体層5間に、第2の絶縁膜3が設けられていない部分上に設けられた第2の半導体層6が挟まれた構造からなる半導体層が島状に絶縁分離されて設けられ、第2の半導体層6の周囲にはゲート絶縁膜12を介して包囲型ゲート電極13が設けられ、第1の半導体層5には概略高濃度ソースドレイン領域(8、11)及び低濃度ソースドレイン領域(9、10)が設けられ、第2の半導体層6には概略チャネル領域が設けられ、高濃度のソースドレイン領域(8、11)及び包囲型ゲート電極13には配線体(17、18、20、21)が接続されているMISFET。

(もっと読む)

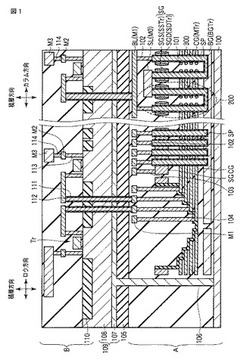

半導体装置

【課題】大面積基板など、熱収縮による影響の大きい基板に形成された半導体素子であっても、その影響を受けずに動作するような半導体素子の提供すること。また、そのような半導体素子を搭載し、薄膜半導体回路及び薄膜半導体装置を提供すること。さらに、多少のマスクずれが生じたとしても、その影響を受けずに動作するような半導体素子を提供する。

【解決手段】ドレイン領域114、117側の半導体層の低濃度不純物領域と重なるように形成した複数のゲート電極102を有し、それぞれのゲート電極102が形成するチャネル領域122、123に流れる電流の向きが一方向と一方向と反対の方向となるようにそれぞれのゲート電極102に対応するソース領域115、116とドレイン領域114、117を形成し、一方向に電流が流れるチャネル領域122と一方向と反対の方向に電流が流れるチャネル領域123の数が等しい薄膜トランジスタ。

(もっと読む)

表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い表示装置を提供する。消費電力が少なく、信頼性の高い表示装置を提供する。

【解決手段】トランジスタの、ゲート電極となる導電層、ゲート絶縁層となる絶縁層、半導体層、およびチャネル保護層となる絶縁層を連続して形成する。ゲート電極(同一層で形成される他の電極または配線を含む)と島状半導体層の形成を、一回のフォトリソグラフィ工程で行う。該フォトリソグラフィ工程と、コンタクトホールを形成するフォトリソグラフィ工程と、ソース電極及びドレイン電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程と、画素電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程の、4つのフォトリソグラフィ工程で表示装置を作製する。

(もっと読む)

半導体装置

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジ

スタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁

層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化

物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トラ

ンジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極

層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソ

ース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレ

イン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

酸化物半導体を用いる装置、表示装置、及び、電子機器

【課題】酸化物半導体をチャネル材料とする薄膜トランジスタを用いるに当り、配線交差部において酸化物半導体の経時的な特性の変化に伴って耐圧低下が生じないようにする。

【解決手段】酸化物半導体TFTを用いる回路部の配線交差部において、下部配線431と上部配線432との間に、ゲート絶縁膜434、酸化物半導体層435、及び、チャネル保護膜436を積層し、酸化物半導体層435の立ち上げ部435Aの外周面と上部配線432の内周面との間にチャネル保護膜436を介在させる。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】半導体装置において、セルフターンオンが発生しないようにし、安定した動作を実現する。

【解決手段】半導体装置を、基板1と、基板の上方に設けられ、電子走行層6及び電子供給層7を含む半導体積層構造2と、半導体積層構造の上方に設けられたゲート電極3、ソース電極4及びドレイン電極5と、ゲート電極、ソース電極及びドレイン電極の上方に設けられ、ゲート電極、ソース電極及びドレイン電極のそれぞれに接続されたゲートパッド10、ソースパッド11及びドレインパッド12と、ゲートパッド、ソースパッド及びドレインパッドの下方に設けられた導電層1とを備えるものとし、ゲートパッドとソースパッドとの間の距離を、ゲートパッドとドレインパッドとの間の距離よりも小さくする。

(もっと読む)

表示装置用金属配線膜

【課題】Si半導体層および/または透明導電膜との間のバリアメタル層を省略しても、低抵抗のオーミック特性を有する電気的接触を確保でき、更に十分な耐熱性を有する表示装置用金属配線膜を提供する。

【解決手段】Moを20原子%以上含有しており、且つ、Si、Nd、Ni、Mn、Mg、Fe、及びZnよりなる群から選択される少なくとも一種を5原子%以上含有しているAl合金膜53と、純CuまたはCu合金膜28,29とからなる積層膜であって、前記Al合金膜が、半導体層33と直接接続していると共に、前記CuまたはCu合金膜が透明導電膜55と直接接続している表示装置用金属配線膜。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】保護膜(Al2O3)の膜質変化に起因するTFT特性のばらつきを軽減することが可能な薄膜トランジスタの製造方法を提供する。

【解決手段】TFT1の製造プロセスにおいて、ソース・ドレイン電極15上に、第1保護膜16(Al2O3層)とAl層とをこの順に、スパッタリングにより連続的に成膜する。各層のスパッタリングでは、いずれもターゲットとしてアルミニウムを用いるが、Al2O3層の成膜過程では、反応ガスとして使用する酸素ガスによってターゲット表面が変質し易い。その後、連続してAl層を成膜する(酸素ガスを使用しないスパッタリングを行う)ことで、ターゲット表面が改質される(成膜処理の度に、ターゲット表面が改質される)。従って、成膜処理回数が増しても、保護膜における膜厚や屈折率が変化しにくい。

(もっと読む)

薄膜トランジスタアレイ基板、及び液晶表示装置

【課題】透明導電膜上層に形成される絶縁膜の膜浮きの発生を防止或いは抑制し、歩留り或いは信頼性を向上することの可能な薄膜トランジスタアレイ基板、及び液晶表示装置を得る。

【解決手段】この発明のTFTアレイ基板100においては、TFT51と、ソース電極53及びドレイン電極54、並びにソース電極53及びドレイン電極54と同一材料により同層に形成される金属パターン5の何れかに直接重なり形成される透明導電膜パターン6と、透明導電膜パターン6上を含むゲート絶縁膜8上を覆う上層絶縁膜9を備え、少なくとも額縁領域42に形成される透明導電膜パターン6は、ソース電極53、ドレイン電極54或いは金属パターン5のパターン端面を覆うことなく形成される。

(もっと読む)

埋め込み配線を備える基板、その製造方法、これを利用する半導体装置およびその製造方法

【課題】 低抵抗の埋め込み配線を備える基板の製造方法を提供する。

【解決手段】 始めに半導体用基板100の第1面S1上に導電層120を形成する。次に、導電層120をパターニングして第1方向に延長する線形の導電層パターン122を形成する。導電層120をパターニングするとき露出する半導体用基板100をエッチングして導電層パターン120の下部に第1方向に延長する線形の半導体パターン104を形成する。次に導電層パターン120および半導体パターン104上に絶縁層150を形成する。半導体用基板100の第1面S1側の絶縁層150が支持基板160と当接するように支持基板160上に配置する。次に半導体用基板100のイオン注入層102側の絶縁層150が露出するように半導体用基板100を除去する。これにより、導電層パターン120は、半導体パターン104の埋め込み配線として利用することができる。

(もっと読む)

発光表示装置の作製方法

【課題】トランジスタの作製工程を簡略化し、フォトマスクの枚数を従来よりも少なくするだけでなく、新たな工程を増やすことなく発光表示装置を作製することを目的とする。

【解決手段】トランジスタを構成する半導体層に真性または実質的に真性な高抵抗の酸化物半導体を使用することによって、個々のトランジスタに対して半導体層を島状に加工する工程を省くことができる。半導体層の上層に形成した絶縁層を開口する工程において該半導体層の不要な部分を同時にエッチングし、フォトリソグラフィ工程を削減する。

(もっと読む)

配線構造体、半導体素子、配線基板、表示用パネル及び表示装置

【課題】 酸化物電極との良好な接続を行うことや、絶縁膜等との界面で生じる相互拡散を抑制することができ、かつ製造工程の低コスト化を図ることができる配線構造体、それを用いた半導体素子、配線基板、表示用パネル及び表示装置を提供する。

【解決手段】 アルミニウム層、銅層及び銅合金層からなる群より選択される少なくとも1つの層と、アルミニウム合金層とを含む2層以上の積層体であり、該アルミニウム合金層が表層に配置されている配線構造体である。これにより、液晶表示装置等において、酸化物電極と配線との接続部で酸化膜が形成されず、良好な接続を行うことができる。

(もっと読む)

表示装置

【課題】画素部の薄膜トランジスタにおけるゲート・ソース間容量のばらつきを抑制することが可能な技術を提供する。

【解決手段】画素の領域毎に形成される画素電極PXと、画素電極を駆動する薄膜トランジスタとを備える表示装置において、薄膜トランジスタは、対角位置に形成される第1の角部B及び第2の角部Cと、前記第1の角部Bが形成される第1の辺と前記第2の角部Cが形成される第2の辺とを共有する第3の角部とを有し、ゲート絶縁膜を介して前記ゲート線GLに接続されるゲート電極と重畳して形成される半導体層ASと、前記ドレイン線DLからその一部が延在して形成され、前記第3の角部と重畳されるドレイン電極DTと、一端が前記第1の角部Bに重畳して形成され、他端が前記画素電極と接続される第1のソース電極ST1と、一端が前記第2の角部Cと重畳して形成され、他端が前記画素電極PXと接続される第2のソース電極ST2と、を有する。

(もっと読む)

薄膜トランジスタアレイ基板、その製造方法、及び液晶表示装置

【課題】 FFSモードの液晶表示装置において、半透過マスクを用いることなくフォトリソグラフィー工程数を削減することができ、さらに断線を防止することができる薄膜トランジスタアレイ基板、その製造方法、及び液晶表示装置を提供すること

【解決手段】本発明にかかる薄膜トランジスタアレイ基板は、ゲート配線43を覆うゲート絶縁膜11上に形成されたソース配線44と、ゲート絶縁膜11上に形成され、ドレイン電極5の下のほぼ全面と、ソース電極4の下のほぼ全面と、ソース配線44の下のほぼ全面と、ゲート電極の対面とに配設された半導体層2と、一部がドレイン電極5の上に直接重なり形成された画素電極6と、ソース電極4及びソース配線44の上に、画素電極6と同じ層によって直接重なり形成された透明導電パターン6aと、画素電極6及び透明導電パターン6aを覆う層間絶縁膜12上に形成され、画素電極6との間でフリンジ電界を発生させる対向電極8と、を備えるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】 バーズビークの増大を抑制し、小型で信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】 そこで本発明の半導体装置の製造方法は、半導体基板と前記半導体基板上に絶縁膜を介して形成された第1導電型の半導体層とを有するSOI基板と、第1導電型の半導体層からなる活性領域内に、第2導電型の半導体層からなるウェルを形成するとともに、ウェル内および第1導電型の活性領域内に、第1導電型の半導体層からなるソース・ドレイン領域を形成した横型MOSFETの製造方法であって、活性領域のうち、素子領域を除く領域を不活性化し、不活性化領域(絶縁性領域14)を形成する工程を含み、不活性化領域を形成する工程が、活性領域に対し、所定間隔を隔てて所定幅の小トレンチを形成する工程と、小トレンチを囲む領域の活性領域3を酸化し、小トレンチTsが酸化膜で覆われるとともに、隣接する小トレンチまで酸化膜が到達するように酸化する工程を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】基板1Cは、半導体基板2と絶縁層3と半導体層4とが積層されたSOI領域1Aと、半導体基板2で構成されたバルク領域1Bとを有しており、SOI領域1Aの半導体層4に形成されたMISFETは、チャネル領域に不純物が導入されておらず、バルク領域1Bの半導体基板2に形成されたMISFETは、チャネル領域に不純物が導入されている。SOI領域1AのMISFETを形成する際には、MISFETのチャネル領域に不純物が導入されないようにし、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とは行なわない。バルク領域1BのMISFETを形成する際には、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とを行う。

(もっと読む)

半導体装置

【課題】大画面化しても低消費電力、歩留まり及び信頼性の向上を実現するための半導体

装置の構造及びその作製方法を提供する。

【解決手段】画面で使われる画素薄膜トランジスタを逆スタガ型薄膜トランジスタで作製

する。その逆スタガ型薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上

に作製する。また、ソース配線と逆スタガ型薄膜トランジスタ、画素電極と逆スタガ型薄

膜トランジスタをつなぐ金属配線を同一工程で作製する。

(もっと読む)

回路基板及び表示装置

【課題】 配線の特性の劣化を生じさせることなく、額縁面積を削減することが可能な回路基板、及び、該回路基板を備える表示装置を提供することを目的とする。

【解決手段】 支持基板上にトランジスタ及び外部接続端子が載置されたトランジスタ基板と、該トランジスタ基板上に取り付けられた外付け部材とを含んで構成される回路基板であって、上記外付け部材は、導電部材を介して外部接続端子と電気的かつ物理的に接続されており、上記トランジスタは、外部接続端子と横並びに配置されている回路基板である。

(もっと読む)

液晶表示装置および液晶表示装置の製造方法

【課題】液晶表示装置の製造コストの低減を図る。

【解決手段】電界効果型の薄膜トランジスタを備える液晶表示装置であって、薄膜トランジスタの半導体層に、インジウムを材料に含む透明アモルファス酸化物半導体が用いられ、半導体層は、ソース電極およびドレイン電極並びにそれらの電極線として必要な領域を含む形状に形成され、半導体層に積層されるソース・ドレイン層に、インジウムを含む金属薄膜が用いられ、ソース・ドレイン層に積層される絶縁層に、窒化珪素による絶縁膜が用いられ、薄膜トランジスタのチャネル部が、絶縁層とソース・ドレイン層とに設けられた開口部によって形成されていることを特徴とする。

(もっと読む)

21 - 40 / 347

[ Back to top ]