Fターム[5F110HM19]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | ソース、ドレイン配線に工夫 (347)

Fターム[5F110HM19]に分類される特許

41 - 60 / 347

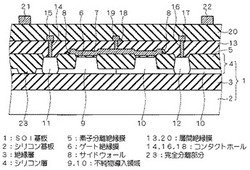

半導体装置及びその製造方法

【課題】電源配線の電位の変動に起因するボディ領域の電位の変動を抑制し得る半導体装置を得る。

【解決手段】シリコン層4の上面内には、パーシャルトレンチ型の素子分離絶縁膜5が選択的に形成されている。電源配線21は、素子分離絶縁膜5の上方に形成されている。電源配線21の下方において、素子分離絶縁膜5には、絶縁層3の上面に達する完全分離部分23が形成されている。換言すれば、半導体装置は、電源配線21の下方において、シリコン層4の上面から絶縁層3の上面に達して形成された完全分離型の素子分離絶縁膜を備えている。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

耐ITOピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供すること。

【解決手段】薄膜トランジスタにおいて透明導電膜とAl合金膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記Al合金膜は、Geを0.1〜5原子%含むと共に、前記Al合金膜の3倍以上のGeを含む第1層と、第1層よりもGe含有率の低いAl合金からなる第2層と、を含む積層構造を有すること。

(もっと読む)

半導体装置及びその製造方法

【課題】集積度が高くリソグラフィーコストが低いn型及びp型FETの積層構造を有した半導体装置を提供すること。

【解決手段】半導体装置100は、半導体基板1上にそれぞれ離隔しつつ列状に形成された第1グループの複数の柱状ゲート電極10と、前記半導体基板1上であって前記第1グループの隣接する柱状ゲート電極10間に形成された第1導電型の第1半導体層12と、前記第1半導体層の上であって前記第1グループの隣接する柱状ゲート電極間に形成された第1絶縁層20と、前記第1絶縁層20の上であって前記第1グループの隣接する柱状ゲート電極10間に形成された前記第1導電型と異なる第2導電型の第2半導体層13とを備え、前記第1半導体層12をチャネルとする前記第1導電型の第1MOSFETが形成され、前記第2半導体層13をチャネルとする前記第2導電型の第2MOSFETが形成されている。

(もっと読む)

積層構造体、多層配線基板、アクティブマトリックス基板、画像表示装置、及び積層構造体の製造方法

【課題】インクジェット法により形成した微細な導電層の積層構造体、多層配線基板、アクティブマトリックス基板、画像表示装置、及びその製造方法を提供する。

【解決手段】濡れ性変化材料を含む濡れ性変化層を形成し、その一部にエネルギーを付与して、低表面エネルギー部を隔て互いに近接した第1の領域43と第2の領域44を含む高表面エネルギー部を形成し、導電性材料を含有する機能液61を第1の領域43にインクジェット法を用いて選択的に滴下し、機能液61を乾燥させて高表面エネルギー部上に導電層を形成する。その際、第1の領域43の中心位置と機能液61の滴下中心位置の距離Xは、機能液の飛翔時の直径D、機能液の着弾位置ばらつきα、第1の領域の幅L、第1の領域と第2の領域との間隔Sとして、X<±(L+2S−D−2α)/2(但し、L+2S>D+2α)、及び、X<±(L+D−2α)/2(但し、L+2D>D+2α)で表される。

(もっと読む)

半導体装置及びその製造方法

【課題】リーク電流が低く、電界効果移動度が高いなどの優れた特性を有するTFTを備え、駆動回路を内蔵して部材点数を減らすことが可能な半導体装置において、駆動回路内部における腐食などの発生を防止する。

【解決手段】本発明の半導体装置においては、駆動回路を内蔵したTFTアレイ基板100に、ゲート電極2と、ゲート絶縁膜3と、結晶性半導体部分を含んでチャネル領域4cが形成される半導体層4と、チャネル領域4cを保護するチャネル保護膜5と、半導体層4に接続されたソース電極6及びドレイン電極7を備えたTFT、並びに、ゲート電極2と同層に形成された配線層2aとソース電極6と同層に形成された配線層6aを駆動回路内部においてコンタクトホール13を介し直接接触させて接続させる配線変換部12を備えるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

半導体装置

【課題】機能回路の電源配線及び接地配線に要する接地面積を少なくし、同時に消費電流による電源電圧降下及び接地電圧上昇を抑えることで、薄型・軽量・高機能・低価格の半導体装置を提供する。

【解決手段】機能回路に電源電圧を供給する電源配線1009及び接地電圧を供給する接地配線1010が格子状に配置されている半導体装置である。格子状にすることで、電源電圧降下及び接地電圧上昇は大幅に低減できる。また、配線幅を細くしても、格子状にしない場合と同程度の電源電圧降下及び接地電圧上昇に抑えられるので、電源配線及び接地配線の配置面積を大幅に低減できる。

(もっと読む)

フロント型プロジェクタ

【課題】高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつフロント型プロジェクタである。

【解決手段】チャネル形成領域、ソース領域、及びドレイン領域を有する半導体層と、島状のゲート電極とを備えた薄膜トランジスタを有し、ゲート電極が接続する第1配線と、ソース領域又はドレイン領域が接続する第2配線とは直交し、第2配線や容量配線と平行かつ重なるように配置されている。

(もっと読む)

表示装置、及び、表示装置の製造方法

【課題】第一の電極膜に接して形成されている導電膜を有する表示装置と、その製造方法の提供。

【解決手段】ゲート電極膜と、第一の電極膜及び第二の電極膜と、第一の電極膜に接続され、第一の導電層及び第一の導電層と重ねて形成される第二の導電層を含む導電層からなる導電膜と、を備える表示装置の製造方法であって、第一の電極膜と第二の電極膜とを形成する電極膜形成工程と、導電層を第一の電極膜及び第二の電極膜に接続するように形成する導電層形成工程と、導電層のうち所定の領域以外を除去することにより、導電膜を形成する導電膜形成工程と、を含み、導電層形成工程は、第一の導電層を第一の電極膜及び第二の電極膜それぞれの上面に形成する第一の導電層形成工程と、第一の導電層の上面に第二の導電層を形成する第二の導電層形成工程と、を含むことを特徴とする。

(もっと読む)

液晶表示装置及びその製造方法

【課題】工程を単純化することのできる半透過型薄膜トランジスタの製造方法を提供する。

【解決手段】第1及び第2基板を提供し、第1マスク工程で第1基板上にゲートラインを形成し、第2マスク工程で第1基板上のゲート絶縁膜とゲート絶縁膜上の半導体パターンと半導体パターン上の画素領域を定義するようにゲートラインと交差するデータラインとソース電極及びドレイン電極を形成し、第3マスク工程でデータライン上の有機絶縁膜とソース電極及びドレイン電極を形成し有機絶縁膜を貫通する透過ホールを形成し、第4マスク工程で有機絶縁膜を貫通してドレイン電極と接続された画素電極及び透過ホールを形成し、透過ホールの画素電極を露出させる反射電極を画素電極上に形成する液晶表示装置の製造方法を提供する。

(もっと読む)

半導体装置

【課題】絶縁層上の半導体層に形成された部分空乏型のトランジスターにおいて、高いON/OFF比と、安定動作を同時に実現できるようにした半導体装置を提供する。

【解決手段】絶縁層上の半導体層に形成された部分空乏型の第1トランジスターと、前記半導体層に形成された第2トランジスターと、前記半導体層に形成された第3トランジスターと、を備え、前記第1トランジスターは、第1導電型の第1ソース又は第1ドレインを有し、前記第2トランジスターは、第1導電型の第2ソース又は第2ドレインを有し、前記第3トランジスターは、第2導電型の第3ソース又は第3ドレインを有し、前記第1ソース又は第1ドレインの一方と、前記第2ソース又は第2ドレインの一方とが電気的に接続され、前記第2ソース又は第2ドレインの他方と、前記第1トランジスターのボディ領域と、前記第3ソース又は第3ドレインの一方とが互いに電気的に接続されている。

(もっと読む)

論理回路及び半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を出力信号として出力する構成とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】高性能なフレキシブル半導体装置を提供すること。

【解決手段】金属箔から成る支持層、支持層の上に形成された半導体構造部、および半導体構造部の上に形成された樹脂フィルムを有して成るフレキシブル半導体装置。かかるフレキシブル半導体装置では、樹脂フィルムには開口部が形成されており、その開口部に半導体構造部の表面と接触する導電部材が形成されており、半導体構造部が半導体層および半導体層の表面に形成された絶縁層を有して成る。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

半導体装置

【目的】高耐圧NMOSFETなどのレベルシフト素子から素子分離溝越しに隣接した高電位浮遊領域への高電位配線を、高耐圧NMOSFETの耐圧低下や層間絶縁膜の破壊および素子分離溝の分離耐圧劣化を招くことなく、形成できる半導体装置を提供する。

【解決手段】高電位配線9の直下にnドレインバッファ層10と接してp-拡散層11とこれに接するp+拡散層12を形成することで、高電位配線9が横切る絶縁膜44aの電界強度を低下できる。絶縁膜44aの電界強度を低下させることで、高耐圧NMOSFET20の耐圧低下や層間絶縁膜5の破壊および素子分離溝(トレンチ4a)の分離耐圧劣化を防止できる。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】複数ゲートトランジスタの改良された構造、およびその製造プロセスの提供。

【解決手段】相補型金属酸化膜半導体(CMOS)デバイス100は、第1のパラメータを有する少なくとも2つの第1のゲート電極を備えたPMOSトランジスタと、上記第1のパラメータとは異なる第2のパラメータを有する少なくとも2つの第2のゲート電極を備えたNMOSトランジスタと、を有している。上記第1のパラメータおよび上記第2のパラメータは、上記PMOSおよびNMOSトランジスタの上記ゲート電極材料120の厚さ、またはドーパントプロファイルを含んでいる。上記少なくとも2つの第1のゲート電極および上記少なくとも2つの第2のゲート電極の上記第1および第2のパラメータは、それぞれ、上記PMOSおよびNMOSトランジスタの仕事関数を規定する。

(もっと読む)

半導体装置およびその製造方法

【課題】FINFETにおいて、寄生抵抗の改善を図ることができる技術を提供する。

【解決手段】本発明におけるFINFETでは、サイドウォールSWを積層膜から形成している。具体的に、サイドウォールSWは、酸化シリコン膜OX1と、酸化シリコン膜OX1上に形成された窒化シリコン膜SN1と、窒化シリコン膜SN1上に形成された酸化シリコン膜OX2から構成されている。一方、フィンFIN1の側壁には、サイドウォールSWが形成されていない。このように本発明では、ゲート電極G1の側壁にサイドウォールSWを形成し、かつ、フィンFIN1の側壁にサイドウォールSWを形成しない。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

41 - 60 / 347

[ Back to top ]