Fターム[5F110HM19]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | ソース、ドレイン配線に工夫 (347)

Fターム[5F110HM19]に分類される特許

61 - 80 / 347

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

誘電体分離型半導体装置とその製造方法

【課題】耐圧が維持されるとともに絶縁耐量の高いワイヤ配線が電極に配線される誘電体分離型半導体装置を提供する。

【解決手段】誘電体分離型半導体装置は、支持基板、埋込誘電体層および半導体基板から構成される誘電体分離型基板を具備し、半導体基板は、選択的に形成される第1半導体領域と、第1半導体領域をその外周縁から所定の距離だけ離間して取り囲むように設けられる第2導電型の第2半導体領域と、第1半導体領域に接合される第1主電極と、第2半導体領域に接合される第2主電極と、を備え、支持基板は、第1半導体領域に重畳する領域を内包する位置に貫通孔と、貫通孔の開口に現れる埋込誘電体層の領域に接して配設されるシリコーンラダーポリマー層と、貫通孔の開口に現れる埋込誘電体層の領域、シリコーンラダーポリマー層に接して配設される裏面電極と、シリコーンラダーポリマー層に囲まれる空間を埋めて平坦化する第1ハンダと、を備える。

(もっと読む)

表示装置

【課題】高開口率化及び高精細化に対応した液晶表示装置を提供する。

【解決手段】複数の走査線12と、走査線を覆って形成した絶縁膜21と、各走査線12に交差する交差部13Dを有する複数の信号線13と、走査線と信号線とに隣接して配設した画素電極と、半導体層、ゲート絶縁膜、前記走査線に接続したゲート電極と、ドレイン電極14b及びソース電極14aの何れかで信号線に接続された一方の電極と、画素電極に接続されたドレイン電極及びソース電極の他方の電極と、ドレイン電極及びソース電極が信号線に沿う方向に直線状に配置された複数の薄膜トランジスタ14と、第1の重ね合わせ部17aが交差部13D上に重なり第2の重ね合わせ部17cが一方の電極上に重なり一方の電極と信号線とを接続する複数の中継電極17と、を具備し、中継電極の第1の重ね合せ部は走査線12の幅方向の両側端部12b、12cに対応する絶縁膜21の段差部13E,13Dを覆う長さを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を作製し、提供することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層を酸化物半導体膜とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体層に接して保護膜となる酸化物絶縁膜を形成した後に、不純物である水分などを低減する加熱処理(脱水化または脱水素化のための加熱処理)を行って、ソース電極層、ドレイン電極層、ゲート絶縁層中、及び酸化物半導体膜中に加え、上下に接して設けられる膜と酸化物半導体膜の界面に存在する水分などの不純物を低減する。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

液晶表示装置

【課題】光リーク電流の発生を抑制しつつ、半導体膜のアライメント要求精度を緩和した薄膜トランジスタを有する液晶表示装置を提供する。

【解決手段】透明基板の上側に積層されたゲート電極と、ゲート電極の上側に積層されるソース電極及びドレイン電極と、ゲート電極の上側に積層されて、ゲート電極が発生させる電界によりソース電極及びドレイン電極間の電流を制御する半導体膜とを含み、半導体膜は、ゲート電極と平面的に重複する第1の領域と、ゲート電極と平面的に重複しない第2の領域とを有する平面的形状で形成され、ソース電極とドレイン電極は、第2の領域において半導体膜と接続せず、第1の領域において半導体膜と接続する、ことを特徴とする薄膜トランジスタを有する液晶表示装置。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造工程の簡略化を達成しつつ、基板表面の凹凸を低減させることが可能な液晶表示装置を提供することである。

【解決手段】

複数のゲート線と、前記ゲート線に交差する複数のドレイン線と、前記ゲート線と前記ドレイン線との交差部付近にそれぞれ形成された薄膜トランジスタと、隣接する一対の前記ゲート線と隣接する一対の前記ドレイン線とで囲まれた画素領域毎に形成された着色膜とを備え、隣接する画素の着色膜の端部を重ねてなる領域が前記ドレイン線に重畳して形成される液晶表示装置であって、前記ゲート線と前記ドレイン線とを電気的に分離する層間絶縁膜が前記薄膜トランジスタの上層に形成され、前記ドレイン線の形成領域に沿って前記層間絶縁膜に凹部が形成され、該凹部に前記ドレイン線が形成されてなる液晶表示装置である。

(もっと読む)

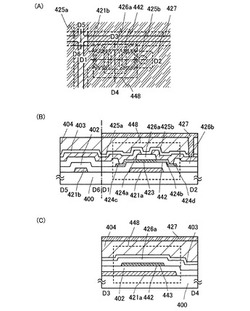

薄膜トランジスタ基板及び薄膜トランジスタ基板の製造方法

【課題】アライメント専用のパターンを設けることなく、かつ高精度なアライメントマークを用いた薄膜トランジスタ基板を提供する。

【解決手段】ゲート信号線245及び共通信号線303の一部には、これらの延伸方向に垂直で、互いに対向するように開口した欠切があり、平行に延びるゲート信号線245及び共通信号線303の間の隙間と、この切欠とを組合わせることにより、外観として十字型が形成される。ドレイン信号線251の一部には、ドレイン信号線251の延伸方向と垂直な2つの凸部があり、ドレイン信号線251とこれらの凸部とを組合わせることにより、外観として十字型が形成される。このように形成された十字型のうちのひとつは、後に形成される層のフォトリソグラフィ工程の露光において、アライメントマークとして使用される。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体装置の作製方法

【課題】分離層と配線を分離させ、半導体素子全体を基板から分離させることを課題とする。

【解決手段】第1の基板上に互いに密着性の弱い第1の層と第2の層を形成し、第2の層上に第1の半導体素子層及び第1の絶縁層を形成し、第1の絶縁層中に第1の層に達するスルーホールを形成し、スルーホール底部に露出した第1の層を酸化させ、第1の絶縁層上及びスルーホール内部に第1の半導体素子層と電気的に接続される配線を形成し、第1の層と第2の層を分離することにより第1の基板から第1の半導体素子層及び配線を分離して配線を露出させる半導体装置の作製方法と、さらに、同様の作製工程により、分離された第2の半導体素子層と配線との間に、異方性導電接着材を設け、第1の半導体素子層と第2の半導体素子層は、異方性導電接着材及び配線によって電気的に接続されている半導体装置の作製方法に関する。

(もっと読む)

半導体装置

【課題】 狭ピッチの画素回路に駆動TFTを効率よく配置する方法を提供する。

【解決手段】 基板1上にトランジスタを含む複数の回路3が配列してなる半導体装置であって、トランジスタを形成する半導体層11は、第1コンタクトパッドQ1と、第1コンタクトパッドに接続して回路の配列ピッチの短い方向と交差する方向に延びる第1の部分R1と、前記第1の部分から前記回路の配列ピッチの短い方向に延びる第2の部分R2と、第1コンタクトパッドとの間に前記第1の部分と前記第2の部分とを含む第2コンタクトパッドQ2とを有しており、第2の部分に絶縁層をはさんで電極層が重なっている。

(もっと読む)

半導体素子の接触部及びその製造方法並びに表示装置用薄膜トランジスタ表示板及びその製造方法

【課題】比抵抗が低いながらも接触特性が良い接触部を含み、優れた接触特性を有する接触部を含む薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】絶縁基板と、ゲート線と、ゲート絶縁層と、半導体層と、データ線と、前記データ線と分離されているドレーン電極と、前記半導体層を覆っていて前記ドレーン電極を露出する第1接触孔、前記ゲート線の一部を露出する第2接触孔、前記データ線の一部を露出する第3接触孔を有する保護膜と、前記第1接触孔を通じて前記ドレーン電極と連結される画素電極と、前記第2接触孔を通じて前記ゲート線と連結されているゲート接触補助部材と、前記第3接触孔を通じて前記データ線に連結されるデータ接触補助部材とを含み、前記データ接触補助部材は凹凸を有することを特徴とする薄膜トランジスタ表示板を提供する。

(もっと読む)

誘電体分離型半導体集積装置、及び半導体集積装置の製造方法

【課題】微細なMOS素子と共存する。

【解決手段】支持基板5と、埋込シリコン酸化膜6と、第1高濃度不純物層9及び低不純物濃度層とからなる活性層15、とで構成されるSOI基板を適用した誘電体分離型半導体集積装置10において、高耐圧半導体素子形成領域を囲んで形成される素子分離領域は、多重溝100と、多重溝の側壁に設けた第1酸化膜105と、第1酸化膜と隣接して多重溝側壁に沿って形成された第2高濃度不純物層110と、第2高濃度不純物層の略上部にLOCOS酸化膜50を介して配設された低抵抗層P2と、前記低抵抗層に積層された第2酸化膜70,75,80と、を備えて構成され、低抵抗層は、第2高濃度不純物層、あるいはドレイン電極と略同電位であり、第2酸化膜の表面でエミッタ電極が前記高耐圧半導体素子形成領域から隣接領域へ引き出されている。

(もっと読む)

液晶表示装置

【課題】光リークに起因した表示品位の劣化を抑制することが可能な液晶表示装置を提供することを目的とする。

【解決手段】 絶縁基板と、前記絶縁基板の上に配置された半導体層と、前記半導体層を覆う第1絶縁膜と、前記第1絶縁膜の上に配置されそれぞれ第1方向に延在した第1ゲート線及び第2ゲート線と、前記第1ゲート線及び前記第2ゲート線を覆う第2絶縁膜と、前記第2絶縁膜の上に配置され第2方向に延在し前記第1ゲート線とクロスする第1クロス部及び前記第2ゲート線とクロスするとともに前記第1クロス部より小さい第2クロス部を有するソース線と、を備えたアレイ基板と、前記アレイ基板に向かい合う対向基板と、前記アレイ基板と前記対向基板との間に保持された液晶層と、を備えたことを特徴とする液晶表示装置。

(もっと読む)

半導体装置及びその作製方法

【課題】接続する素子の駆動電圧によってトランジスタのドレイン電圧が決定される。トランジスタの小型化にともないドレイン領域に集中する電界強度が高まり、ホットキャリアが生成し易くなる。ドレイン領域に電界が集中し難いトランジスタを提供することを課題の一とする。また、トランジスタを有する表示装置を提供することを課題の一とする。

【解決手段】高い導電率を有する第1配線層および第2配線層の端部とゲート電極層の重なりをなくすことにより、第1電極層及び第2電極層近傍に電界が集中する現象を緩和してホットキャリアの発生を抑制し、加えて第1配線層および第2配線層より高抵抗の第1電極層および第2電極層をドレイン電極層として用いてトランジスタを構成する。

(もっと読む)

半導体構造体およびその製造方法(移動度が最適化された方位を有する半導体ナノワイヤ)

【課題】高いオン電流、低いオフ電流を与えるp型半導体ナノワイヤ・デバイス、n型半導体ナノワイヤ・デバイスを提供する。

【解決手段】各々が半導体リンク部30C,50Cと2つの隣接するパット部30A,30B,50A,50Bを含む半導体構造体で、半導体リンク部の側壁は、第1の半導体構造体の場合には正孔の移動度を最大化するように、第2の半導体構造体の場合には電子の移動度を最大化するように方位を定める。半導体構造体の酸化による薄化で、半導体リンク部の幅は、異なる結晶方位ごとに異なる速度で小さくされる。異なる量の薄化の結果、薄化後に得られる半導体ナノワイヤが目標とするサブリソグラフィ寸法となるように、予め決定される。異なる結晶面に対する異なる薄化速度を補償することによって、過剰な薄化又は不十分な薄化がなされることなく、最適なサブリソグラフィ幅を有する半導体ナノワイヤを形成する。

(もっと読む)

液晶パネル

【課題】複数個のアレイ基板を同時に形成するためのアレイ基板用マザー基板にスピンコ

ーターを用いてレジスト塗布する際、表示領域内に放射状の塗布ムラが生じないような配

線パターンとされたアレイ基板を備えた液晶パネルを提供すること。

【解決手段】本発明の液晶パネルは、液晶層を挟持して対向配置された一対の基板を有し

、前記一対の基板の一方の表示領域には複数のサブ画素がマトリクス状に形成されている

と共に、表示領域の周縁部には表示領域からゲート配線39G及びソース配線39Sが端

子領域まで延在されている液晶パネルにおいて、前記互いに隣接するゲート配線39G及

びソース配線39S等の引き回し配線の直近の屈曲点P1同士を順次結んでなるラインが

、端子領域が形成されている辺と実質的に平行な直線ラインL1とされている。

(もっと読む)

高耐圧半導体装置および高電圧集積回路装置

【目的】ワイヤ接続における高耐圧半導体装置において、複雑なプロセス製造工程も、複雑な裏面加工工程も一切伴わず、低コストで高耐圧化、高信頼性化を実現できる高耐圧半導体装置およびそれを用いた高電圧集積回路装置を提供することにある。

【構成】半導体基板100上に誘電体層101を介して半導体層102が形成され、半導体層102上にドレイン層113と、ドレイン層113を内包するように形成されたバッファ層112と、ドレイン層113と離間し、その周りを囲むように形成されたソース層114と、ソース層114を内包するように形成されたウエル層111と、半導体層102上にゲート絶縁膜を介して形成されたゲート電極110と、を備えた高耐圧半導体装置において、ドレイン層113及び、バッファ層112の平面形状が非連続または連続の環状とする。

(もっと読む)

61 - 80 / 347

[ Back to top ]