Fターム[5F110HM19]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−共通 (7,931) | ソース、ドレイン配線に工夫 (347)

Fターム[5F110HM19]に分類される特許

81 - 100 / 347

半導体装置

【課題】配線抵抗の低い半導体装置を提供すること、透過率の高い半導体装置を提供すること、または開口率の高い半導体装置を提供することを課題とする。

【解決手段】ゲート電極、半導体層、ソース電極又はドレイン電極を透光性を有する材料を用いて形成し、ゲート配線又はソース配線等の配線を透光性を有する材料より抵抗率が低い材料で設ける。また、ソース配線及び/又はゲート配線を、透光性を有する材料と当該透光性を有する材料より抵抗率が低い材料を積層させて設ける。これにより、配線抵抗が低く、透過率の高い半導体装置を提供することができる。

(もっと読む)

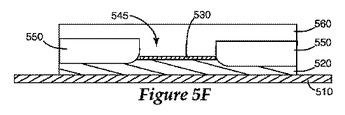

電気光学装置および電子機器

【課題】第1中間導電層や第2中間導電層に起因したデッドスペースを削減する。

【解決手段】第1スイッチング素子Q1と第2スイッチング素子Q2とは走査線22をゲートとして動作する。第1スイッチング素子Q1は、第1データ線24Aと第1中間導電層541との間に電気的に介在し、第2スイッチング素子Q2は、第2データ線24Bと第2中間導電層542との間に電気的に介在する。第1中間導電層541は第1電極31に導通し、第2中間導電層542は第2電極32に導通する。第1中間導電層541の少なくとも一部と第2中間導電層542の少なくとも一部とは、平面視で走査線22に重なる。

(もっと読む)

表示体

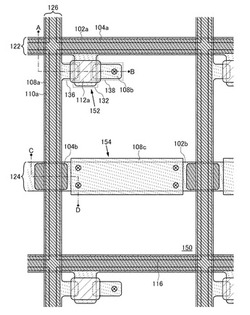

【課題】プリント基板に設けられたアクティブマトリクスを機械的および電磁気的に保護する上で有利な表示体を提供する。

【解決手段】表示体は、観察者側に位置する図示しない前面板と、該前面板に対向して配置される背面板とを備えている。背面板は、前記前面板に対向する面に形成された画素電極101と、該画素電極101を駆動するアクティブマトリクスとを有している。背面板は、プリント基板で構成されている。プリント基板は、画素電極層と、第1絶縁層113aと、ソース線層およびゲート線層と、2つの第2絶縁層113b、113cと、トランジスタ層と、第3絶縁層114と、グランド層112と、第4絶縁層115とがこの順番で前面板から離れる方向に積層されて構成されている。

(もっと読む)

半導体装置

【課題】コンタクトホールの加工時において配線のダメージを受けにくく、信頼性の低下を抑制できる構造の接続部を有する半導体装置を提供すること。

【解決手段】接続部1は、第1導電層2と第2導電層4とが、その交差個所に設けられたコンタクトホール5を介して接続されたものである。矩形状のコンタクトホール5は第2導電層4の幅方向の略中央に配置されている。そして、コンタクトホール5のパターンを囲むように矩形状の半導体層3が設けられている。半導体層3は、コンタクトホール5の底部において第1導電層2上に形成されている。この半導体層3は、第1導電層2とのエッチング選択比が高く、第1導電層2に対するエッチング効率が充分に高いものである。

(もっと読む)

印刷形成した接続部を有する回路基板及びその製造方法

【課題】

課題は、回路基板の有機TFT素子の接続部において接続用電極配線のショートや寸法精度不良を改善するため、層間絶縁膜(絶縁バンク)を素子の電極間のみに形成することで接続用電極の隣接パターンショートを確実に回避することである。

【解決手段】

解決手段は、回路基板において、基板と、基板上に形成された薄膜トランジスタ素子と、該薄膜トランジスタ素子の金属電極群に外部回路基板の接続端子を電気的に接続するための接続部において、当該接続部の各々の金属電極間のみを覆う絶縁膜が形成された接続部と、上記薄膜トランジスタ素子の金属電極と上記絶縁膜の両方に接する接続用電極群とを有することであり、そしてまた、上記薄膜トランジスタ素子の金属電極は接続部で周期的に配列され、上記絶縁膜はライン形状であり上記薄膜トランジスタ素子の金属電極間に周期的に配置され、上記絶縁膜の算術平均粗さRaは2μm以下であることである。

(もっと読む)

薄膜素子およびその製造方法

【課題】 製造に際し、当初、耐熱性の高い仮基板を用い、最終的に、耐熱性の低いフィルム基板を用い、仮基板を除去し、これにより得られた薄膜トランジスタパネルにおいて、画素電極(薄膜)が破損しにくいようにする。

【解決手段】 仮基板51上に形成された分離層52上に画素電極2を形成する。この場合、画素電極2下以外の領域における分離層52が膜減りしたとしても、その上に下地絶縁膜1を形成し、仮基板51および分離層52を除去すると、下地絶縁膜1の下面に平板状の画素電極2が凹んだ状態で埋め込まれることになるので、画素電極2が破損しにくいようにすることができる。

(もっと読む)

表示装置及びその製造方法

【課題】静電気による薄膜トランジスタの破壊を防止することが可能な技術を提供することである。

【解決手段】

複数本のドレイン線と、前記ドレイン線と交差する複数本のゲート線と、複数の薄膜トランジスタを有し、前記ドレイン線及び前記ゲート線に駆動信号を供給する駆動部と、該駆動部に外部から制御信号を入力する電極端子とを備え、前記ドレイン線と前記ゲート線とに囲まれた領域を画素の領域とする表示装置の製造方法であって、前記駆動部の複数の薄膜トランジスタを形成する際に、前記画素の集合体である表示領域の外側領域に、前記複数の薄膜トランジスタを相互に接続し前記駆動信号の生成動作をさせる第1の配線と同一層の配線であり、かつ前記第1の配線とは異なる第2の配線を形成し、少なくとも一対の薄膜トランジスタを接続する工程と、前記薄膜トランジスタの形成後に、前記表示領域の外側領域において、前記第2の配線の切断する工程とを有する表示装置の製造方法である。

(もっと読む)

半導体装置

【課題】金属配線と金属酸化物を有する層を形成する際、電蝕といわれる腐食の発生をおさえることにより、半導体装置の動作特性および信頼性を向上させ、歩留まりの向上を実現することを目的とする。

【解決手段】配線は、耐酸化性金属からなる第1の層と、その上に形成されたアルミニウムもしくはアルミニウムを主成分とする第2の層と、その上に形成された耐酸化性金属からなる第3の層からなる3層構造とし、前記配線と電気的に接続する金属酸化物を有する層を有する。また、第2の層の上面及び下面は第1及び第3の層と接し、側面は酸素とアルミニウムを含む酸化層と接する。

(もっと読む)

表示装置及びその作製方法

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素を作製する際に、生産性の向上を図る。

【解決手段】基板上に形成されたゲート電極として機能する第1の配線と、前記第1の配線上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に、低抵抗酸化物半導体層及び前記低抵抗酸化物半導体層上に導電層が積層して設けられた第2の配線、並びに前記低抵抗酸化物半導体層及び前記低抵抗酸化物半導体層の画素電極として機能する領域が露出するように前記導電層が積層して設けられた電極層と、前記ゲート絶縁膜上の前記第2の配線と前記電極層との間に形成された高抵抗酸化物半導体層と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面コンタクト電極と拡散層とのコンタクト抵抗が低減して、半導体装置の動作速度の向上を図ることを可能にする。

【解決手段】基板10の表面側に形成された拡散層25P、26P、25N、26Nと、前記拡散層25P、26P、25N、26Nの表面に形成されていて前記拡散層25P、26P、25N、26Nよりも抵抗が低い低抵抗部27P、28P、27N、28Nと、前記基板10の裏面側より前記基板10を貫通して前記拡散層25P、26P、25N、26Nを通して前記低抵抗部27P、28P、27N、28Nに接続された裏面コンタクト電極63P、64P、63N、64Nを有する。

(もっと読む)

半導体装置、およびその作製方法

【課題】アクティブマトリクス型表示装置等の半導体装置において、トランジスタの駆動能力を低下させることなく寄生容量の容量値を低減することを課題の一とする。または、寄生容量の容量値を低減した半導体装置を低コストに提供することを課題の一とする。

【解決手段】トランジスタのゲート電極と同一の材料層で形成される配線と、ソース電極またはドレイン電極と同一の材料層で形成される配線との間に、ゲート絶縁層以外の絶縁層を設ける。

(もっと読む)

半導体装置

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体層と、酸化物半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層との順で積層されたゲート電極を含むゲート配線と、酸化物半導体層と、前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、酸化物半導体層と電気的に接続され、第3の導電層と第4の導電層との順で積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

薄膜トランジスタ基板前駆体及び薄膜トランジスタ基板の製造方法

【課題】液晶表示装置の表示品位の低下を抑制して、薄膜トランジスタの欠陥を修正する。

【解決手段】各画素毎にゲート電極が規定され、互いに平行に延びるように設けられた複数のゲート線11aと、各画素のゲート電極に絶縁膜を介して重なるように島状に設けられた第1半導体層13aと、各画素毎に各ゲート線11aに絶縁膜を介して重なるように島状に設けられた第2半導体層13bと、各画素毎に第1半導体層13aを介してゲート電極の一方の端部に重なるようにソース電極14aaが規定され、各ゲート線11aと交差する方向に互いに平行に延びるように設けられた複数のソース線14aと、各画素毎に第1半導体層13aを介してゲート電極の他方の端部に重なると共にソース電極14aaと対峙するようにドレイン電極14baが規定され、各画素電極にそれぞれ接続するように設けられた複数のドレイン線14bとを備えている。

(もっと読む)

陽極酸化された薄膜構造用の電気的接続

第1の薄膜メタライゼーション層と第2の薄膜メタライゼーション層とを電気的に接続する回路ビアの形成のための手法が述べられる。ビアの形成では、第1のメタライゼーション層の陽極酸化に先立って、ビア接続領域に配置される陽極酸化バリア及び/又は補助パッドを使用する。バリアを形成するために使用される材料は、陽極酸化の際に陽極酸化液を実質的に透過せず、導電層とバリアとの間に酸化物が形成されることを阻止するものである。補助パッドは非陽極酸化性であり、陽極酸化の際に、パッドを通じて電流が流れることを実質的に防止するためにバリアによって覆われる。陽極酸化の後に、バリアは除去される。補助パッドが充分な導電性を有する場合には、バリアの除去後に第1のメタライゼーション層上に残存されてもよい。第2のメタライゼーション層が陽極酸化層上に配置され、ビア接続領域において第1の導電層と電気的に接触する。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体装置を提供する。

【解決手段】本発明による半導体装置(100)は、絶縁層(125)の一部および半導体層(126)を覆う第1層間絶縁膜であって、絶縁層(125)のうちの下側電極(142)上の領域を覆わない第1層間絶縁膜(102)と、絶縁層(125)および第1層間絶縁膜(102)を覆う第2層間絶縁膜(104)と、第1層間絶縁膜(102)および第2層間絶縁膜(104)に設けられたコンタクトホールを介して半導体層(125)のソース領域およびドレイン領域と電気的に接続されたソース電極(128)およびドレイン電極(130)と、ソース電極(128)およびドレイン電極(130)と同じ材料から形成され、絶縁層(125)および第2層間絶縁膜(104)に設けられたコンタクトホールを介して下側電極(142)と電気的に接続された上側電極(144)とを備える。

(もっと読む)

半導体装置

【課題】従来の透過型液晶パネル向け半導体装置を小型化し、マイクロディスプレイを実現しようとするとき、半導体装置と透明電極とを接続するビアホールの径が縮小するため、接触抵抗が高くなるという問題があった。また、接触抵抗低減のために、半導体装置と透明電極との間に中間金属層を設けると、画素の開口率が低下し、画面が暗くなるという課題があった。

【解決手段】本発明の半導体装置は、半導体装置と透明電極との間に設ける中間金属層に切欠部を有する。この切欠部により、中間金属層の側面の面積を拡大し、透明電極との接触面積を従来よりも大きくすることができる。また、中間金属層の側面部面積を利用するため、画素表面に対する投影面積を小さく設定でき、画素の開口率を大きくすることができる。このため、十分な明るさをもつ、超小型のマイクロディスプレイを提供できる。

(もっと読む)

アクティブマトリクス基板及び液晶表示装置

【課題】アクティブマトリクス基板における配線と電極端子との接続部において、電極端子に欠陥が生じた場合でも、配線に含まれる金属が腐食することがない構成を提供する。

【解決手段】本発明のアクティブマトリクス基板は、接続部16を備えたアクティブマトリクス基板であって、上記接続部16は、第1の金属層1bと、上記第1の金属層1bの上に、上記第1の金属層1bの幅より狭く積層された第2の金属層1aと、上記第2の金属層1aの上に、上記第2の金属層1aを完全に覆い、かつ上記第1の金属層1bの幅より狭く積層された保護部2と、上記保護部2の上に、上記保護部2を完全に覆い、かつ上記第1の金属層1bに接触するように積層された電極端子3とを備えているので、電極端子3に欠陥部4が生じた場合でも、配線に含まれる金属が腐食することがない。

(もっと読む)

アレイ基板及びアレイ基板の製造方法

【課題】製造歩留まりの高いアレイ基板及びアレイ基板の製造方法を提供する。

【解決手段】アレイ基板1は、チャネル層19と、ゲート絶縁膜21と、ゲート配線と、ゲート電極23と、層間絶縁膜25と、非晶質シリコン層27aと、データ配線と、を備えている。データ配線は、非晶質シリコン層27aに積層され、金属で形成され、ゲート絶縁膜21及び層間絶縁膜25に形成されたコンタクトホールh1を介してチャネル層19に接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極のミスアライメントに起因してトランジスタのオン電流が変動することを抑制する。

【解決手段】この半導体装置は、第1トランジスタ200、第2トランジスタ300、第1配線410、第2配線420、及び第1ゲート電極120を備えている。第1ゲート電極120は、第1トランジスタ200及び第2トランジスタ300のゲート電極であって、第1チャネル領域225上及び第2チャネル領域325上を直線状に延伸している。そして、第1トランジスタ200の第1ソース210は、第1ゲート電極120を介して第2トランジスタ300の第2ソース310の反対側に位置しており、第1トランジスタ200の第1ドレイン220は、第1ゲート電極120を介して第2トランジスタ300の第2ドレイン320の反対側に位置している。

(もっと読む)

81 - 100 / 347

[ Back to top ]