Fターム[5F110NN01]の内容

Fターム[5F110NN01]の下位に属するFターム

層間絶縁膜 (8,935)

島状のチャネル保護膜 (1,301)

材料 (15,721)

製法 (8,383)

Fターム[5F110NN01]に分類される特許

81 - 100 / 137

有機半導体素子モジュール

【課題】本発明は、基材の表面の凹凸の低減により有機半導体素子の特性ばらつきの低減を可能にする有機半導体素子モジュールを提供する事を目的とするものである。

【解決手段】表面に凹凸がある基材10の上に凹凸緩衝保護層20を設け、その凹凸緩衝保護層20の上に有機半導体素子38構成部分を設置する。有機半導体素子38構成部分を、凹凸緩衝保護層20および基材10とで挟みこむように、第2保護層22を設置するものである。

(もっと読む)

有機半導体材料及び有機電界効果トランジスタ

【課題】塗布プロセスが可能で、高次の規則性及び結晶性を有し、且つ、安定性も良好な有機半導体材料を提供する。

【解決手段】5員環及び/又は6員環の芳香環が6以上、20以下結合してなり、且つ、下記式(1)で表わされる部分構造を有し、移動度が1.0×10-3cm2/Vs以上であり、固体状態でのイオン化ポテンシャルが、4.8eV以上、5.6eV以下である化合物を用いる。

式中、R1及びR2は各々独立に、水素原子又は一価の有機基を表わす。但し、R1及び

R2の少なくとも一方は、置換されていても良い芳香族基である。

(もっと読む)

有機薄膜トランジスタ

【課題】移動度の高い有機薄膜トランジスタを提供することである。

【解決手段】ゲート絶縁層の上に、表面処理層及びその上に有機半導体化合物を含有する有機半導体層を有する有機薄膜トランジスタにおいて、前記有機半導体層を形成する前の前記表面処理層の表面を、走査型プローブ顕微鏡の探針を近接または接触した状態で走査した時、前記探針と前記表面処理層との間に生じるFFM信号差が100mV以下であることを特徴とする有機薄膜トランジスタ。

(もっと読む)

アクティブマトリクス型液晶表示装置およびスイッチング素子

【課題】液晶表示装置のTFT基板側の薄膜トランジスタにバックライト光が照射されると、TFTのソース・ドレイン電極とゲート電極との間で、アモルファスシリコン半導体領域を透過しながら多重反射し、フロントチャネルに光が入射され、TFTに光オフリーク電流が発生する。

【解決手段】薄膜トランジスタで『ゲート線101のゲート電極部分−ソース電極105及びゲート線101のゲート電極部分−ドレイン電極106のオーバーラップ長d』を、ゲート線101のゲート電極部分の端部から入射する光がチャネル部に到達するまでに十分減衰できるような距離に、例えば、4μm以上に設定すると、チャネル部に入射される光が、バックライト出射強度の0.2%以下に抑制できるため、光オフリーク電流を十分に低減することができ、フリッカーや表示の不均一性を改善することができた。

(もっと読む)

液晶表示装置とその製造方法

【課題】 TFT液晶表示装置の生産コストを低減するために4枚マスク・プロセスに続く3枚マスク・プロセスの開発を推進する。

【解決手段】低抵抗金属層と、パシベーション絶縁層と非晶質シリコン層とゲート絶縁層の食刻ガスで除去可能な耐熱金属層との積層よりなるソース・ドレイン配線を形成し、パシベーション絶縁層を付与した後、その断面形状が逆テーパ形状の感光性樹脂パターンを用いて、パシベーション絶縁層と非晶質シリコン層とゲート絶縁層とからなる積層に開口部を形成し、絵素電極用導電性薄膜層のリフトオフにより絵素電極の形成を行うことで、開口部形成工程と開口部形成工程に続く絵素電極形成工程を1枚のフォトマスクで処理する。半導体層の島化工程は、上記開口部内の第1の非晶質シリコン層のサイドエッチングまたは前記感光性樹脂パターンの形成にハーフトーン露光技術を併用して行うことで3枚マスク・プロセスを実現する。

(もっと読む)

平板表示装置及び平板表示装置の製造方法

【課題】有機薄膜トランジスターの特性が損なわれることを減少することができる平板表示装置の製造方法を提供する。

【解決手段】平板表示装置の製造方法は、絶縁基板を備える段階と、絶縁基板上にチャネル領域を定義するために離間して設けられるソース電極及びドレイン電極を形成する段階と、ソース電極とドレイン電極上に第1保護層を形成する段階と、第1保護層上にチャネル領域に対応する開口部が設けられた金属層を形成する段階と、金属層をマスクとして利用して開口部を通じ第1保護層にチャネル領域を露出させる載置孔を形成する段階と、載置孔の内部と金属層の上に有機半導体層と第2保護層を順に形成する段階と、金属層、載置孔以外の有機半導体層及び第2保護層を除去する段階とを含む。

(もっと読む)

有機半導体薄膜の製造方法及び有機半導体薄膜、並びにそれを用いた有機電子デバイス及び有機電界効果トランジスタ

【課題】 結晶粒の大きい有機半導体薄膜を製造することの可能な有機半導体薄膜の製造方法を提供する。

【解決手段】 脱離により二重結合を形成する構造を有する有機半導体前駆体の薄膜を、温度勾配を有する系内を移動させることにより、結晶成長させながら有機半導体の薄膜に変換する工程をそなえるとともに、移動速度x(mm/s)と移動方向の温度勾配d(℃/mm)とが式(I)で表わされる条件を満たすようにする。

0.001 < xd < 1000 (I)

(もっと読む)

薄膜トランジスタ搭載パネル及びその製造方法

【課題】 レーザーアニールによる熱によっても、プラスチック基板上に形成された薄膜トランジスタが、そのプラスチック基板から剥離し難い構造からなる薄膜トランジスタ搭載パネル及びその製造方法を提供する。

【解決手段】 プラスチック基板上に形成されたアモルファスシリコンをレーザーアニールしてポリシリコン薄膜を形成し、そのポリシリコン薄膜の所定領域に不純物イオンを添加した後にレーザーアニールによって熱活性化してなる薄膜トランジスタ搭載パネルであって、プラスチック基板とポリシリコン薄膜との間に、レーザーアニール時にプラスチック基板側に伝わる熱を緩衝する熱緩衝膜を形成する。その熱緩衝膜の厚さをT(μm)、熱緩衝膜の材料の比熱をC(J/(g・K))、熱緩衝膜の材料の比重をρ(g/cm3)、熱緩衝膜の材料の熱伝導率をκ(W/(m・K))としたとき、T≧1.02×κ/(C×ρ)の関係を満たす。

(もっと読む)

薄膜トランジスタの作製方法、その薄膜トランジスタを用いた表示装置及びその表示装置が組み込まれた電子機器

【課題】薄膜トランジスタを作製する際、従来のCVD法により形成される膜よりも高品質の膜を形成すること、熱酸化法で形成される膜と同等又はそれ以上の品質の膜を基板に影響を及ぼさない温度で形成することを目的とする。

【解決手段】ガラス基板、所定のパターンに形成された非晶質シリコンを含む半導体膜、ゲート電極及び該ゲート電極から延びた配線、ゲート絶縁膜となる絶縁膜、保護膜の少なくとも一つに対し、ガラス基板の温度を該ガラス基板の歪点より100℃以上低い温度とし、低電子温度且つ高電子密度でプラズマ酸化又はプラズマ窒化をおこなう。

(もっと読む)

液晶表示装置

【課題】 本発明は、非晶質の導電性膜を所定のエッチャントを用いて、所定の形状にパターニングし、当該パターニングされた導電性膜を覆うように保護絶縁膜を形成したとしても、当該保護絶縁膜の異常成長を防止することができる、液晶表示装置を提供することを目的とする。

【解決手段】 本発明の一例に係る液晶表示装置は、上面に薄膜トランジスタが形成されているガラス基板1と、上面に対向電極が形成されているカラーフィルタ基板16との間に、液晶が封止されている。そして、画素電極10は、薄膜トランジスタのドレイン電極と接続されている。また、画素電極10は、透明性を有する保護絶縁膜13により、覆われている。当該画素電極10は、InとZnとを含む酸化化合物を有している。

(もっと読む)

半導体装置およびその製造方法ならびに画像表示装置

【課題】 移動度を向上させ、かつ、電流劣化が抑制された半導体装置およびその製造方法ならびに画像表示装置を提供する。

【解決手段】 薄膜トランジスタは、透明基板10と、透明基板10上に形成され、チャネル領域210とソース/ドレイン領域211S,211D,221S,221Dとを含む多結晶シリコン膜20と、多結晶シリコン膜20上に形成され、シリコン酸化膜を含むゲート絶縁膜30と、ゲート絶縁膜30上に形成されたゲート電極40と、ゲート電極40を覆うように形成され、ゲート絶縁膜30におけるシリコン酸化膜よりも高い体積密度でSi−O−H結合を有するシリコン酸化膜を含む層間絶縁膜50と、層間絶縁膜50上に形成された保護膜90とを備える。

(もっと読む)

電極基板,薄膜トランジスタ,表示装置、及びその製造方法

本発明は、下部電極をフォトマスクに利用して、絶縁膜上に下部電極と概ね同一パターン形状の撥液領域と概ね反転パターン形状の親液領域を形成して、親液領域内に導電性インクを塗布焼成して、下部電極に対して概ね反転パターン形状の上部電極を自己整合して形成するため、印刷法を用いても位置ずれが発生しない。このため、アクティブマトリクス型薄膜トランジスタ基板などの半導体装置が印刷法を用いて形成できる。  (もっと読む)

(もっと読む)

有機薄膜トランジスタ表示板及びその製造方法

【課題】有機薄膜トランジスタの製造工程を減らすと共に、高解像度有機半導体層を実現することができる有機薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】本発明は、基板と、ある一方向に延びた複数のゲート線と、前記ゲート線と絶縁されて交差する複数のデータ線と、前記データ線に接続されているソース電極と、前記ソース電極と対向するドレイン電極と、前記ドレイン電極に接続されている画素電極と、前記ソース電極と前記ドレイン電極に接続されており、感光性を有する有機物質からなる有機半導体層とを備えることを特徴とする有機薄膜トランジスタ表示板及びその製造方法を提供する。

(もっと読む)

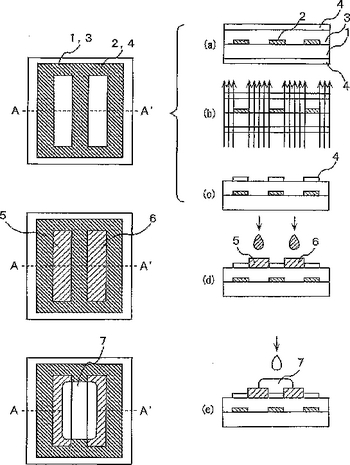

半導体装置、光学装置及びセンサ装置

【課題】 ソール電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】 ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

薄膜の膜厚測定方法、多結晶半導体薄膜の形成方法、半導体デバイスの製造方法、およびその製造装置、並びに画像表示装置の製造方法

【課題】 薄膜の膜厚を1分間に1万点以上の測定を基板全面にわたって行う検査を可能とする。

【解決手段】 透明基板2上に形成された薄膜3に対してレーザ光を照射し、基板の測定領域全体に渡って基板内の多数の同一ポイントでの透過強度を透過光強度モニタ4、反射光強度を反射光強度モニタ5で測定する。反射率をRとし透過率をTとしてA=1−(R+T)の値からA値と膜厚の関係から膜厚を測定し評価する。

(もっと読む)

有機薄膜トランジスタ及びその製造方法

【課題】本発明は、低い仕事関数をもって、高い電界放出効果と電荷移動度及び電気伝導度をもつCNTと有機半導体物質を混合すること、又はCNT上に有機半導体物質をコーティングすることによって、有機半導体層を形成させ、高い電気伝導度と電荷移動度及び高速のスイッチング速度を実現することができる有機TFT及びその製造方法を提供する。

【解決手段】本発明は有機TFT及びその製造方法に係り、有機TFTでCNTと有機半導体物質を混合すること、又はCNT上に有機半導体物質をコーティングすることによって、有機半導体層を形成させ、高い電気伝導度と電荷移動度を有するCNTの物性により、既存の低い電荷移動度とスイッチング特性を有する有機半導体層の物性を向上させることができる有機TFT及びその製造方法に関する。

(もっと読む)

単結晶シリコン薄膜トランジスタの有機発光ディスプレイ及びその製造方法

【課題】単結晶シリコン薄膜トランジスタの有機発光ディスプレイ及びその製造方法を提供する。

【解決手段】

単結晶シリコンチャンネルを有するスイッチングトランジスタとドライビングトランジスタとによる単結晶シリコン2T−1C構造の半導体回路部がプラスチック基板に形成される構造を有する有機発光ディスプレイである。本発明による単結晶シリコンの製造工程は、結晶成長板に単結晶シリコン及びバッファ層を形成した後、絶縁層上から水素イオンを注入して単結晶シリコン層から所定の深さに位置する分割層を形成する。単結晶シリコン層は、基板に付着され、分割層は、外部に加えられる熱エネルギーによって分割される。これにより、基板上に所定の厚さの単結晶シリコンフィルムを形成できる。

(もっと読む)

縦型有機FET及びその製造方法

有機半導体から成る活性層の分子配向を抑制し、キャリア移動度を向上した縦型有機FETを提供する。本発明は、基板上に少なくともソース電極層、ドレイン電極層、ゲート電極及び活性層が設けられており、ソース電極層、活性層及びドレイン電極層が順に積層した構造を有する縦型有機FETであって、(1)前記ソース電極層及びドレイン電極層が実質的に基板面に対して平行に配置されており、(2)前記ソース電極層及びドレイン電極層が、導電性部材からなり、(3)前記活性層が、中心原子として4価又は6価の元素をもち、かつ、分子面の上下方向からそれぞれ配位子X1及びX2が配位したフタロシアニン系化合物から実質的に構成され、(4)前記化合物の各分子の分子面がソース電極層及びドレイン電極層の少なくとも一方に対して平行状態となるように、前記化合物が積層されている、縦型有機FETに係る。  (もっと読む)

(もっと読む)

電気光学装置用基板、電気光学装置、電子機器、及び電気光学装置用基板の製造方法

【課題】 有機材料を半導体層に用いた半導体装置であって、当該半導体装置が適用される用途に拘らず、特にフレキシビリティが要求されるような用途においても好適に用いることができ、クラックや剥離等の不具合の生じ難い半導体装置を安価に提供する。

【解決手段】 本発明の電気光学装置用基板は、基板上に、複数のデータ線と、前記複数のデータ線と交差する複数の走査線と、前記複数の交差に応じて形成される複数のトランジスタと、前記複数のトランジスタに応じて形成される複数の第1の封止層と、を有し、前記各トランジスタはそれぞれ有機半導体層からなるチャネル領域を有し、 前記各第1の封止層は前記各チャネル領域のいずれかひとつを覆うように形成され、前記各第1の封止層は無機材料からなることを特徴とする。

(もっと読む)

薄膜トランジスタ表示板の製造方法

【課題】プラスチック基板の熱膨張による整列誤差を最小化する。

【解決手段】第1間隔Lを有する複数のゲート電極を含むゲート線121を、熱膨張率を有する基板上に形成する段階;ゲート線121上にゲート絶縁膜140及び半導体層150,160を形成する段階;半導体層150,160を第1間隔Lと異なる第2間隔L+αを有する半導体用マスクでパターニングし、複数の半導体部材154,164を形成する段階、半導体部材154,164及びゲート絶縁膜140上にソース電極を含むデータ線171及びソース電極と対向するドレイン電極175を形成する段階;ドレイン電極と接続されている画素電極を形成する段階;を含む。

(もっと読む)

81 - 100 / 137

[ Back to top ]