Fターム[5F110NN63]の内容

Fターム[5F110NN63]に分類される特許

1 - 20 / 36

半導体装置及び半導体装置の作製方法

【課題】結晶性の高い酸化物半導体をチャネル層に用いて、優れた特性を有する半導体装置を提供することを課題の一つとする。また、下地膜の平坦性を向上させた半導体装置を提供する。

【解決手段】トランジスタの下地膜に化学機械研磨処理を行い、化学機械研磨処理した後、プラズマ処理を行うことで、下地膜の中心線平均粗さRa75値を、0.1nm未満とすることができる。プラズマ処理及び化学機械研磨処理の組み合わせにより得られた平坦性を有する下地膜上に結晶性の高い酸化物半導体層を形成することで、半導体装置の特性向上を図る。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

仮想ボディ・コンタクト型トライゲート

【課題】FETデバイスにおける閾値電圧をより良く制御できるデバイスの提供。

【解決手段】基板101と、基板101の上のSiGe層103と、SiGe層上の半導体層105と、基板、SiGe層及び半導体層に隣接した絶縁層109aと、絶縁層に隣接した一対の第1のゲート構造体111と、絶縁層上の第2のゲート構造体113とを含む電界効果トランジスタ(FET)と、FETを形成する方法である。絶縁層は、SiGe層の側面、並びに半導体層の上面、半導体層の下面及び導体層の側面に隣接していることが好ましい。SiGe層は、炭素を含むことが好ましい。一対の第1のゲート構造体が、第2のゲート構造体に対して実質的に横断方向にあることが好ましい。さらに、第1のゲート構造体の対は、絶縁層によりカプセル封入されることが好ましい。

(もっと読む)

埋め込みガードリング及び耐放射線性分離構造並びにその製造方法

【課題】大量の商業マイクロエレクトロニクスメーカーがアクセスし易い最先端の基礎設備を使用して、高性能且つ費用対効果に優れた耐放射線性集積回路(RHICs)を提供する。

【解決手段】様々な形式の放射線エネルギーによって引き起こされる有害な影響を減少し、又は排除するために、従来の設計及びプロセスを使用する一方で特殊構造を含んで半導体デバイスを作成する。このような半導体デバイスは本願で開示された1台以上の寄生的な分離デバイス、及び/又は、埋め込みガードリング構造を含む。これら新規な構造に対応する設計、及び/又は、工程ステップの導入には、従来のCMOS製作工程との互換性がある。したがって、比較的低い費用で比較的簡単に実施することができる。

(もっと読む)

半導体装置

【課題】基板を介したクロストークを抑制でき、放熱性が高い半導体装置を提供する。

【解決手段】実施形態に係る半導体装置1は、半導体基板10を備える。前記半導体基板の内部には空洞11が形成されている。また、前記半導体基板の内部には、前記空洞を前記半導体基板の上面に連通させる連通孔12も形成されている。前記半導体装置は、さらに、前記空洞及び前記連通孔の内面上に設けられた絶縁膜13と、前記空洞及び前記連通孔の内部に埋め込まれ、熱伝導率が前記絶縁膜の熱伝導率よりも高い伝熱部材14と、前記半導体基板における前記空洞の直上域に形成された素子21,22と、を備える。

(もっと読む)

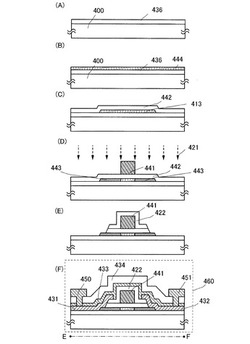

電子装置、電子装置の素子分離方法、電子装置の製造方法、及び電子装置を備えた表示装置

【課題】半導体電子素子を含む電子装置の微細化、及び低コスト化を実現する。

【解決手段】半導体膜を含む電子素子を複数備える電子装置であって、電子素子の素子間に素子分離領域が存在し、素子分離領域は、バンドギャップが1.95eV以上である半導体膜と、絶縁体膜と、素子分離電極と、を含み、素子分離電極は、絶縁体膜によって素子分離領域の半導体膜と隔てられ、電圧が印加されて素子分離領域の半導体膜を高抵抗化し、電子素子間を電気的に分離するための電極であることを特徴とする電子装置。

(もっと読む)

半導体装置およびその製造方法

【課題】アンテナスイッチで発生する高調波歪みをできるだけ低減できる技術を提供する。

【解決手段】界面キャリア層SCLを構成する電子の移動抑制手段として、MISFETQN1とMISFETQN2の間に電極層ELを設けて電極層ELと界面キャリア層SCLとの間に容量素子Cを形成する手段をとっている。そして、この容量素子Cの上部電極となる電極層ELに正電位を印加することにより、電極層ELに相対する界面キャリア層SCLの電子を固定している。

(もっと読む)

半導体装置

【課題】第1、第2素子形成領域間でノイズが伝播することを抑制することができる半導体装置を提供することを目的とする。

【解決手段】第1、第2素子形成領域20、30に形成された半導体素子のうち、第1素子形成領域20に形成された半導体素子を外部機器と接続し、第1素子形成領域20と第2素子形成領域30との間に、第1導電型層60と、当該第1導電型層60に挟まれる第2導電型層61とを配置し、第1、第2導電型層60、61の間に、オフ時に半導体層12の表面から埋込絶縁膜11に達し、第1、第2素子形成領域20、30との間を仕切る空乏層63、64を構成する。

(もっと読む)

チャネルが埋込み誘電体層を通り抜けているメモリセル

【課題】浮動チャネルまたは浮動ゲートを持つFET(Field Effect Transistor(電界効果トランジスタ))により形成されたメモリセル、複数のメモリセルから成るメモリアレイの提供。

【解決手段】絶縁層BOXによってベース基板から隔てられた半導体材料の薄層を含むセミコンダクタ・オン・インシュレータ基板と、少なくとも基本的にセミコンダクタ・オン・インシュレータ基板の薄層中に配列されたソース領域S、ドレイン領域D、トレンチがその中に作られているチャネルC、トレンチ中のゲート領域Gを含むFETトランジスタを備え、トレンチが、絶縁層BOXを越えベース基板の深さの中に延びていること、チャネルが、絶縁層の下でソース領域とドレイン領域の間に延びていることを特徴とするメモリセル。複数のメモリセルを備えるメモリアレイ、およびメモリセルを製作するプロセス。

(もっと読む)

絶縁膜下の埋め込みバック・コントロール・ゲートを有するSeOI上の同型のトランジスタからなる回路

【課題】リソグラフィーパターン転写に存在する変動性によって発生する問題の解決、STIを使用せず、構造を厳密化して空間を節約すること、転写されるべきより規則的かつ緻密な構造の提供。

【解決手段】SeOI基板上に形成された半導体デバイスであり、電界効果トランジスタから形成された行の形で配置されパターンのアレイを備え、電界効果トランジスタのチャンネル領域の上方に形成されたフロント・コントロール・ゲート領域を備え、各行に含まれるソース領域およびドレイン領域も同じ寸法を有し、かつ所定の寸法を有するフロント・コントロール・ゲート領域だけ隔てられ、パターンに含まれる少なくとも1つのトランジスタT1〜T4がチャンネル領域の下方に存在するベース基板内に形成されたバック・コントロール・ゲート領域を有し、トランジスタのしきい電圧をシフトさせて、バック・コントロール・ゲート領域がバイアスされることを可能とする。

(もっと読む)

半導体集積回路装置

【課題】絶縁耐圧の向上、電位ノイズマージンの強化、および多結晶シリコン配線の微細化を実現したIGBTやMOSトランジスタ等の半導体集積回路装置を提供する。

【解決手段】埋め込み酸化膜102を有するSOI基板100のSOI層99に、埋め込み酸化膜102に達する深さまで第1絶縁分離トレンチ109を形成し、第1絶縁分離トレンチ109に取り囲まれて絶縁分離された素子領域103にIGBTを形成する。さらに、第1絶縁分離トレンチ109を取り囲んで、埋め込み酸化膜102に達する深さまで第2絶縁分離トレンチ110を形成する。そして、第1絶縁分離トレンチ109と第2絶縁分離トレンチ110との間にSOI層からなる電位固定領域104を形成し、その電位固定領域104は、IGBTのコレクタ電位と同電位になるように設定(接続)する。

(もっと読む)

電源遮断トランジスタを有する半導体装置

【課題】パワーゲーティングの適用に困難さをもたらすコストアップと性能低下のトレードオフを打開する。

【解決手段】P型基板2と、P型基板2に互いに離れて形成されている第1のPウェル4および第2のPウェル5と、を有し、第1のPウェル4にN型ロジックトランジスタLTnが形成され、第2のPウェル5に電源遮断トランジスタPGTが形成され、第1のPウェル4と第2のPウェル5との間に、P型基板2内の電位干渉を遮蔽する遮蔽部(例えば2つのPN接合)が形成されている。遮蔽部により電位干渉が遮蔽された2つの基板領域のうち、第2のPウェル5側の基板領域に、電源遮断トランジスタPGTに基板バイアス電圧VBBを印加するための基板コンタクト領域11が形成されている。

(もっと読む)

薄膜トランジスタおよびアクティブマトリクスディスプレイ

薄膜トランジスタが、絶縁基板上の半導体アイランド内に形成される。このトランジスタは、第1の伝導型のソース(1502)およびドレイン(1504)と、逆の第2の伝導型のチャネル(1508)とを備えている。チャネルは、1つまたは複数の絶縁ゲート(1510)と重なっており、分離ダイオードを備えている。各分離ダイオードは、低濃度にドープされた第1の領域(1506)と、高濃度にドープされ、第2の伝導型である第2の領域(1512)とを備えている。ダイオードは、絶縁ゲート(1510)とは重なっていない。第1の領域(1506)および第2の領域(1512)は、隣接するソースまたはドレインの長さよりも短い距離だけ、チャネル(1508)から延びている。低濃度にドープされた領域(1506)は、ソースまたはドレインから延びており、高濃度にドープされた領域(1512)は、低濃度にドープされた領域から延びているため、第1の領域(1506)および第2の領域(1512)は、トランジスタの主要伝導経路に直角の方向においては、隣接するソースまたはドレインとpn接合を形成するが、主要伝導経路に平行な方向においては形成しない。  (もっと読む)

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】窒化ガリウム系の高電子移動度トランジスタについて、2次元電子濃度及び電子移動度を高くするとともに、ショートチャネル効果を生じさせない。

【解決手段】下地20上に順次に積層されたチャネル層40である第1GaN層と、電子供給層50であるAlN層と、キャップ層60である第2GaN層とを備える。AlN層の厚みが2.5nm以上8nm以下である。

(もっと読む)

半導体装置

【課題】複数の回路を搭載する場合において、回路間のノイズ伝播などの誤動作を抑制することが可能な半導体装置を提供すること。

【解決手段】支持基板と、前記支持基板上に設けられた絶縁層と、前記絶縁層上に設けられ第1回路を有する第1半導体層と、前記絶縁層上に設けられ、前記第1半導体層と絶縁され、第2回路を有する第2半導体層と、前記絶縁層上のうち前記第1半導体層と前記第2半導体層との間に設けられ、前記第1半導体層及び前記第2半導体層とそれぞれ絶縁された分離層と、前記分離層との間で静電容量を保持するように前記分離層の上層に設けられ、電気的に接地された容量層とを備える。

(もっと読む)

半導体回路

【課題】高速のスイッチング特性と小サブスレッショルド電流特性とが両立可能なMOS−FETで構成される半導体回路を提供する。

【解決手段】MOS−FETQ1,Q2により構成される論理回路1を有した半導体回路において、MOS−FETQ1,Q2のバックゲートバイアス電圧Vcc,VSSとは異なる電圧Vpp,Vbbを供給する電圧供給手段15,13と、MOS−FETQ1,Q2のバックゲートバイアス電圧を、電圧Vcc,VSSと電圧Vcc,VSSとは異なる電圧Vpp,Vbbとに切り換えるスイッチング手段10とを備えた構成となっている。

(もっと読む)

半導体装置

【課題】分離領域幅を拡大することなく、LDMOSトランジスタのスイッチング電圧波形を滑らかにする。

【解決手段】素子領域15を分断用トレンチ16で囲むと共に、分断用トレンチ16で囲まれた素子領域15のうちのいずれかに、当該素子領域15をさらに絶縁分離する分離用トレンチ17を設ける。この場合、素子形成基板1のうち、絶縁膜3とドレイン電極14との間に絶縁膜3に達する分離用トレンチ17を設ける。これにより、1つの分断用トレンチ16内で電気的に絶縁された領域を複数形成し、各領域に接続される各ゲート抵抗20〜22、24の抵抗値を調節することで、各領域を絶縁分離するための分離領域幅を拡大することなく、LDMOSトランジスタ5のスイッチング電圧波形を滑らかにする。

(もっと読む)

有機トランジスタ、有機トランジスタアレイ及び表示装置

【課題】本発明は、オフ電流を低下させることが可能な有機トランジスタ、該有機トランジスタを有する有機トランジスタアレイ及び該有機トランジスタアレイを有する表示装置を提供することを目的とする。

【解決手段】有機トランジスタ10aは、基板1、ゲート電極2、分離用電極3、ゲート絶縁膜4、ソース電極5、ドレイン電極6及び有機半導体層7を有し、ゲート絶縁膜4を介して、分離用電極3と、有機半導体層7が積層されている領域を有し、分離用電極3に電源が接続されている。

(もっと読む)

マイクロ電子デバイス構造体およびその形成方法(ガード・リングまたはコンタクトをSOI基板に形成する方法)

【課題】セミコンダクタ・オン・インシュレータ(SOI)基板(120)のバルク半導体領域(116)とコンタクトする導電素子(110、310、410a、410b、510)を形成する方法が提供される。

【解決手段】第1の開口部(228)は、トレンチ分離領域(124)の上を覆う共形層(126)に形成される。トレンチ分離領域(124)は、基板(120)のSOI層(108)と端部を共有してもよい。誘電体層(114)は、共形層(126)およびトレンチ分離領域(124)の上面を覆って付着されるのが望ましい。次に、誘電体層(114)および共形層(126)の第1の開口部(228)を通って延びる第2の開口部(416)を形成することができる。バルク半導体領域(116)の一部および共形層の上面(128、328、414a、414b、514)は、第2の開口部(416)内に露出されるのが望ましい。その後、第2の開口部(416)は、金属または半導体のうちの少なくとも1つで充填されて、バルク半導体領域(116)および共形層(126)の上面(128、328、414a、414b、514)の露出部分とコンタクトする導電素子(110、310、410a、410b、510)を形成することができる。

(もっと読む)

半導体集積回路装置

【課題】 デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としないSOI基板及び半導体集積回路装置を提供する。

【解決手段】 P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

1 - 20 / 36

[ Back to top ]