Fターム[5F110NN65]の内容

Fターム[5F110NN65]の下位に属するFターム

LOCOS (413)

Fターム[5F110NN65]に分類される特許

141 - 160 / 962

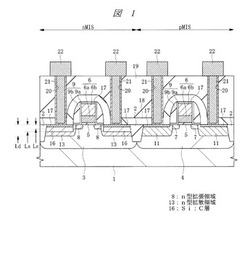

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

半導体装置

【課題】半導体装置における素子形成領域エッジ部分の電界集中を抑制し、素子の消費電力低減を図る。

【解決手段】半導体装置は、シリコンを含む絶縁膜上に選択的に形成された厚さが35nm以下の半導体膜と、半導体膜の周囲に、半導体膜以上の厚みの酸化シリコン膜で絶縁膜上に形成された素子分離膜と、素子分離膜上及び半導体膜上に、素子分離膜及び半導体膜で構成される凹部に沿って平面図で直線状に形成されたゲート電極膜と、を有するため、半導体膜上面は、その周囲に設けられた酸化シリコン膜の上面よりも低く構成される。そのため、ゲート電極膜が半導体膜の側面の一部にまわりこんで形成されることはなく、従来のような電界集中の問題を抑制することができる。

(もっと読む)

半導体装置

【課題】SOI構造の単結晶半導体層(SiGe層/歪みSi層/SiGe層)上のMISFETの提供

【解決手段】半導体基板1に選択的に設けられた第1のトレンチの下部側面及び底面に絶縁膜3が設けられ、側面絶縁膜3間の底面絶縁膜3上に空孔4が設けられ、空孔4及び側面絶縁膜3上には単結晶半導体層が設けられ、半導体層は絶縁膜2が埋め込まれた第2のトレンチにより、島状に絶縁分離され、歪みSi層6直上にはゲート酸化膜11を介してゲート電極12が設けられ、半導体層には、ゲート電極12に自己整合してn型ソースドレイン領域(8、9)が、ゲート電極12の側壁のサイドウォール13に自己整合して、n+型ソースドレイン領域(7、10)がそれぞれ設けられ、ゲート電極12(配線図示せず)及びn+型ソースドレイン領域にはバリアメタル16を有する導電プラグ17を介してバリアメタル19を有する配線20が接続されているMISFET。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタ160と、第2のトランジスタ162と、第1のトランジスタ160のソース領域またはドレイン領域120と、第2のトランジスタ162のチャネル形成領域144との間に設けられた絶縁層128と、を含むメモリセルを有し、第1のトランジスタ160と、第2のトランジスタ162とは、少なくとも一部が重畳して設けられる半導体装置である。また、絶縁層128と第2のトランジスタのゲート絶縁層146は、式((ta/tb)×(εrb/εra)<0.1)を満たす。(但し、式中、taはゲート絶縁層146の膜厚を示し、tbは絶縁層128の膜厚を示し、εraはゲート絶縁層146の誘電率を示し、εrbは絶縁層128の誘電率を示す。)

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ソース線と、ビット線と、第1の信号線と、第2の信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセルと、ソース線及びビット線と電気的に接続された第1の駆動回路と、第1の信号線と電気的に接続された第2の駆動回路と、第2の信号線と電気的に接続された第3の駆動回路と、ワード線と電気的に接続された第4の駆動回路と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含んで構成される。

(もっと読む)

半導体装置及びその製造方法

【課題】容易なプロセスにより単結晶半導体層を形成したSOI構造のMISFETの提供

【解決手段】半導体基板1上に、第1の絶縁膜2を介して、一部に空孔4を有する第2の絶縁膜3が設けられ、空孔4上及び第2の絶縁膜3の一部上に島状に絶縁分離された半導体層6が設けられ、半導体層6上にゲート酸化膜12を介して、空孔4直上に空孔4の幅以下のゲート電極13が設けられ、半導体層6には、ゲート電極13に自己整合して低濃度のソースドレイン領域(9,10)が、ゲート電極13の側壁に設けられたサイドウォール14に自己整合して高濃度のソースドレイン領域(8,11)がそれぞれ設けられ、ゲート電極13(配線図示せず)及び高濃度のソースドレイン領域(8,11)にはバリアメタル17を有する導電プラグ18を介してバリアメタル20を有する配線21が接続されているMISFET。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、メモリセルアレイを有する半導体装置において、直列に接続された第1乃至第mのメモリセルに含まれる各ノードに生じる寄生容量の値を同等の値とすることで、安定して動作可能な半導体装置とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ソース線と、ビット線と、信号線と、ワード線と、ソース線とビット線との間に、並列に接続されたメモリセル1100と、ソース線及びビット線とスイッチング素子を介して電気的に接続された第1の駆動回路1111と、ソース線とスイッチング素子を介して電気的に接続された第2の駆動回路1112と、信号線と電気的に接続された第3の駆動回路1113と、ワード線と電気的に接続された第4の駆動回路1114と、を有し、メモリセルは、第1のゲート電極、第1のソース電極、および第1のドレイン電極を有する第1のトランジスタと、第2のゲート電極、第2のソース電極、および第2のドレイン電極を有する第2のトランジスタと、容量素子と、を有し、第2のトランジスタは、酸化物半導体材料を含む。

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積の増大を抑制しつつ、信頼性に優れた構造を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板12と、化合物半導体基板12に埋め込まれた埋込電極と、を備え、化合物半導体基板12の主面に溝22、24が設けられており、少なくとも溝22、24の側壁上に設けられた第一の金属膜10a、10bと、少なくとも溝22、24の底面上に設けられており、第一の金属膜10a、10bと異種材料で構成される第二の金属膜9a、9bと、を含む積層体により溝22、24を埋め込むことで、上記埋込電極が構成されており、第一の金属膜10a、10bのフェルミエネルギーは化合物半導体基板12の真性フェルミエネルギーと異なり、第二の金属膜9a、9bのフェルミエネルギーは化合物半導体基板12の真性フェルミエネルギーと異なる。

(もっと読む)

半導体装置の製造方法

【課題】第2絶縁膜からセルフアラインに所定の距離だけ離して半導体素子を形成可能で、第2絶縁膜と単結晶層との界面の上部でのリーク電流の発生の低減が可能な半導体装置の製造方法を提供する。

【解決手段】SOI基板の単結晶層の上方に形成した第1絶縁膜をストッパに単結晶層と第1耐酸化膜をエッチングして第1絶縁膜の上に単結晶柱5aを形成し、第1耐酸化膜を単結晶柱5aの上に配置したまま単結晶柱5aを一部熱酸化し単結晶柱5aの側面を囲むように閉ループパターンで形成され第1耐酸化膜の外周部の直下にせり出し部10aを有する第2絶縁膜10を形成し、第1耐酸化膜を除去して単結晶柱5aの上面を露出させ、単結晶柱5aの上面に半導体素子を形成する。第2絶縁膜10を形成したことにより、せり出し部10aの下の単結晶柱5aの上面は、側面の近くになるにつれ徐々にその上面の高さが低くなり側面につながる傾斜面になっている。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】第1のトランジスタと第2のトランジスタを有し、第1のトランジスタと第2のトランジスタとは少なくとも一部が重畳する第1のメモリセルと、第3のトランジスタと第4のトランジスタを有し、第3のトランジスタと第4のトランジスタとは少なくとも一部が重畳する第2のメモリセルと、駆動回路と、を有し、第2のメモリセルは、第1のメモリセル上に設けられ、第1のトランジスタは、第1の半導体材料を含んで構成され、第2のトランジスタ、第3のトランジスタ、および第4のトランジスタ、は、第2の半導体材料を含んで構成される半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に集積され定格電圧を埋め込み酸化膜と素子活性層のドレインとで分担する高耐圧半導体素子において、耐圧特性の変動が少ない高信頼度でかつ実用化に有効な半導体装置を得ること。

【解決手段】ソース側にフローティングリサーフ層とドレイン側にn型の電界緩和層を設けソースおよびドレイン領域での電界集中を同時に緩和させる手段を設けることで、耐圧特性の変動が少ない高信頼の高耐圧半導体装置が提供できる。

(もっと読む)

半導体装置

【課題】低電位領域と高電位の配線が交差することの無い優れた耐圧性能を示す半導体装置を提供することを課題とする。

【解決手段】本発明の半導体装置は、ロジック回路(501)と、ロジック回路からの制御信号に従い低電位側パワー素子を駆動する低電位側駆動回路(502)と、ロジック回路からの制御信号がレベルシフト回路を介して入力され、高電位側パワー素子(506)を駆動する高電位側駆動回路(505)と、複数に重なったトレンチ分離領域により、前記高電位側パワー素子を含む高電位島を分離する多重トレンチ分離領域(508)と、を有する。

(もっと読む)

半導体装置

【課題】高度な集積化を実現した、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】チャネル形成領域を含む半導体層と、チャネル形成領域と電気的に接続するソース電極およびドレイン電極と、チャネル形成領域と重畳するゲート電極と、チャネル形成領域とゲート電極との間のゲート絶縁層と、を含み、チャネル形成領域を含む半導体層の側面の一部と、ソース電極またはドレイン電極の側面の一部と、は、平面方向から見て概略一致している半導体装置である。

(もっと読む)

半導体装置

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型のトランジスタにおいてゲートからシリサイドの位置を精度よく制御できるようにする。

【解決手段】柱状半導体14の中央部には、その周囲を囲むように、ゲート絶縁膜9が形成され、さらに、ゲート絶縁膜9の周囲を囲むように、ゲート層6が形成されている。この柱状半導体14の中央部、ゲート絶縁膜9、ゲート層6により、MIS構造が形成されている。ゲート層6の上下には、第1絶縁膜4が形成されている。第1絶縁膜4は、柱状半導体14にも接している。柱状半導体14の側面には、シリサイド18及びn型拡散層(不純物領域)19が形成されている。シリサイド18は、第1絶縁膜4によってセルフ・アラインされた位置に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】良好な特性を有しながら、半導体製造工程における半導体製造装置と半導体装置とへの金属汚染を抑制するような構造を有する半導体装置、および、その製造方法を提供する。

【解決手段】本発明の半導体装置は、nMOS SGT220であり、第1の平面状シリコン層上234に垂直に配置された第1の柱状シリコン層232表面に並んで配置された、第1のn+型シリコン層113と、金属を含む第1のゲート電極236と、第2のn+型シリコン層157とから構成される。そして、第1の絶縁膜129が、第1のゲート電極236と第1の平面状シリコン層234との間に、第2の絶縁膜162が第1のゲート電極236の上面に配置されている。また、金属を含む第1のゲート電極236が、第1のn+型シリコン層113、第2のn+型シリコン層157、第1の絶縁膜129、および、第2の絶縁膜162に囲まれている。

(もっと読む)

141 - 160 / 962

[ Back to top ]