Fターム[5F110NN71]の内容

Fターム[5F110NN71]の下位に属するFターム

Fターム[5F110NN71]に分類される特許

161 - 180 / 2,024

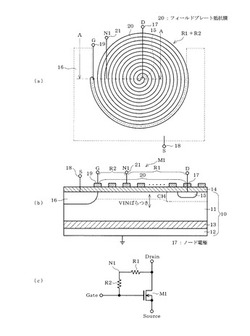

過電流保護回路

【課題】入力電源電圧の動作保証範囲が大きいとしても当該電圧変動の影響を抑制して正常に過電流保護を図るようにした過電流保護回路を提供する。

【解決手段】支持基板10が第1半導体層11および第2半導体層12を絶縁層13で挟んで構成されている。第1半導体層11上には絶縁膜14を介してフィールドプレート抵抗膜20が形成されている。可変電流源ISが、ゲート電極19からドレイン電極17にかけて絶縁膜14上に沿って形成されたフィールドプレート抵抗膜20(フィールドプレート抵抗R1およびR2)に生じるノードN1の電圧に応じて出力電流値を変更してセンス抵抗Rsの検出電圧V2を補正する。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

電界効果型トランジスタ、表示素子、画像表示装置、及びシステム

【課題】低コストで、後工程にて形成される上層の塗布性に優れ、かつ高信頼性を示す電界効果型トランジスタなどの提供。

【解決手段】絶縁性基板と、前記絶縁性基板上に形成されたゲート電極と、前記ゲート電極上に形成されたゲート絶縁層と、前記ゲート絶縁層上に形成されたソース電極及びドレイン電極と、前記ゲート絶縁層上に形成され、かつ、少なくとも前記ソース電極及び前記ドレイン電極との間に形成された酸化物半導体層と、前記酸化物半導体層を被覆するように形成された保護層とを有し、前記保護層が、フッ素樹脂を含有し、前記保護層形成後の前記保護層の水に対する接触角が、75°以上90°以下である電界効果型トランジスタである。

(もっと読む)

半導体装置の製造方法、及び電気光学装置の製造方法

【課題】情報処理と光制御とを一括して光制御基板1枚で処理する場合、例えば低リークを必要とするTFTと、高速動作するTFT等、特性の異なるTFTを同一基板上に形成することが必要となってくる。しかしながら、フォトマスク数を増やすことで特性の異なるTFTを形成すると、TATが延び、価格も高騰するという課題があった。

【解決手段】第1LDDと、第2LDDの2水準の濃度を持つLDDを一つのハーフトーンマスクでレジストを形成した。レジスト膜厚は、第1LDDには低加速エネルギーでは不純物が透過せず、高加速エネルギーでは不純物が通る設定とし、第2LDDではレジストを開口させた。低加速エネルギーでイオン注入することで、第2LDDにはこのイオン注入で1回めのイオン注入が行われる。次に、高加速エネルギーでイオン注入することで第1LDDには高加速エネルギー分の不純物が入り、第2LDDには2回分の不純物が入る。

(もっと読む)

放射線検出装置、放射線撮像装置および放射線撮像システム

【課題】信号配線、ゲート配線の寄生容量を低下させ、感度の向上、ノイズの減少を図る放射線検出装置を提供する。

【解決手段】絶縁基板上に配置されたスイッチ素子と、スイッチ素子上に配置された放射線を電荷に変換する変換素子とを含み、スイッチ素子と変換素子とは接続されている画素を有し、画素は絶縁基板上に行列に二次元配列され、絶縁基板上に配置された行方向に配列された複数のスイッチ素子が共通に接続されるゲート配線と、列方向に配列された複数のスイッチ素子が共通に接続される信号配線と、を有し、スイッチ素子と変換素子の間に複数の絶縁層が配置され、ゲート配線又は信号配線の少なくとも一方が、複数の絶縁層に挟まれて配置されている。

(もっと読む)

発光装置

【課題】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、トランジスタのばらつきを低減する。

【解決手段】駆動用トランジスタと、スイッチング用トランジスタを有する発光装置において、駆動用トランジスタのチャネル幅をチャネル長よりも小さくする。その際、ゲート配線と平行にアノード側電源線を設けて、フルカラー表示を行う。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

表示装置および電子機器

【課題】配線層を低抵抗に保ち、かつ薄膜トランジスタにおける膜剥がれを防止した表示装置および電子機器を提供する。

【解決手段】基板11上に薄膜トランジスタ10および配線層20を備える。薄膜トランジスタ10は、基板11側からゲート電極12,ゲート絶縁膜13および半導体層14を有し、配線層20は、配線層20aおよび配線層20bにより構成されている。配線層20bとゲート電極12とは同一の膜厚および構成材料からなる。配線層20とゲート電極12との厚みは異なっている。具体的には、ゲート電極12の厚みは配線層20の厚みよりも薄く、ゲート電極12の膜内応力が小さくなっている。

(もっと読む)

発光装置の製造方法

【課題】発光装置を製造するときに生じ得る静電気に起因した素子の損傷を低減することのできる発光装置の製造方法について提供することを課題とする。また、静電気に起因した素子の損傷による不良が低減された発光装置を提供することを課題とする。

【解決手段】本発明の発光装置の製造方法は、発光素子を駆動するためのプレーナ型のトランジスタを作製する工程を有する。そして、トランジスタを作製する工程において、活性層として機能する半導体層を形成するときに、行方向及び列方向に延びた格子状の第1の半導体層を基板上に形成すると共に、前記第1の半導体層の間に、島状に分離した第2の半導体層を複数形成することを特徴としている。ここで、第2の半導体層は、トランジスタの活性層として機能する層である。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】トランジスタ上に第1の絶縁膜を有し、第1の絶縁膜上に第1及び第2の配線を有し、第1及び第2の配線上に第2の絶縁膜を有し、第2の絶縁膜上に電極を有し、電極上に第3の絶縁膜を有し、第3の絶縁膜上に画素電極を有し、画素電極は、電極と重なる第1の領域と、電極と重ならない第2の領域と、を有し、画素電極は、第1の配線に電気的に接続されており、第1の配線は、トランジスタのソース又はドレインの一方と電気的に接続されており、電極は、画素部の外側において前記第2の配線と電気的に接続されている。

(もっと読む)

酸化物半導体薄膜の製造方法、電界効果型トランジスタ、表示装置及びセンサ

【課題】SGZO系酸化物半導体薄膜において、低温アニールによる低抵抗化が起こらず、成膜時の抵抗値と低温アニール後の抵抗値が同等となる組成を明らかとし、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した製造方法を提供する。

【解決手段】構成元素の組成比をSn:Ga:Zn=a:b:cとした場合、組成比が、a+b=2、且つ1≦a≦2、且つ1≦c≦11/2、且つc≧−7b/4+11/4を満たす酸化物半導体薄膜を基板上に成膜する成膜工程と、成膜工程後、酸化性雰囲気中で100℃以上300℃未満の熱処理を施す熱処理工程と、を有する。

(もっと読む)

薄膜トランジスタアレー基板、薄膜集積回路装置及びそれらの製造方法

【課題】TFT特性が良好で表示品質や回路配線の層間絶縁性を確保できるTFTアレー基板の製造方法等を提供する。

【解決手段】基材1上への酸化物半導体膜3のパターン形成工程、酸化物半導体膜へのソース電極接続領域3s及びドレイン電極接続領域3dの形成工程、酸化物半導体膜を覆うゲート絶縁膜4の形成工程、ゲート絶縁膜にコンタクトホールを開けてソース電極6s及びドレイン電極6dをソース電極接続領域及びドレイン電極接続領域に接続するとともに酸化物半導体膜上にゲート絶縁膜を介してゲート電極7を形成し、第1回路配線群17を形成する工程、ソース電極、ドレイン電極、ゲート電極及び第1回路配線群上に層間絶縁膜18を形成する工程、層間絶縁膜上に第2回路配線群19を形成する工程を有し、ゲート絶縁膜4の厚さを100nm〜500nmの範囲とし、層間絶縁膜18の厚さを1μm以上且つゲート絶縁膜4の2倍〜10倍の厚さとする。

(もっと読む)

電気光学装置の製造方法

【課題】新たなパラメーターによって半導体層内における不純物分布を制御して電界効果

型トランジスターを形成することのできる電気光学装置の製造方法を提供すること。

【解決手段】LDD構造の電界効果型トランジスターからなる画素トランジスターを基板

本体10wの一方面10sに形成するにあたって、一方面10s側の半導体層1aに不純

物を導入する不純物導入工程を行う。その後、不純物拡散工程において、一方面10s側

にレーザーアニール装置、ヒートガスアニール装置、ランプアニール装置等の加熱装置9

20を配置し、一方面10s側を他方面10t側より温度を高くした状態で半導体層1a

を加熱する。

(もっと読む)

半導体装置

【課題】小型化、薄型化、軽量化を実現した半導体装置の提供を課題とする。また、作製時間を短縮し、歩留まりを向上することができる半導体装置の作製方法の提供を課題とする。

【解決手段】トランジスタと、トランジスタ上に設けられた絶縁層と、絶縁層に設けられた開口部を介して、トランジスタのソース領域又はドレイン領域に電気的に接続された第1の導電層(ソース配線又はドレイン配線に相当)と、絶縁層及び第1の導電層上に設けられた第1の樹脂層と、第1の樹脂層に設けられた開口部を介して、第1の導電層に電気的に接続された導電性粒子を含む層と、第2の樹脂層及びアンテナとして機能する第2の導電層が設けられた基板とを有する。上記構成の半導体装置において、第2の導電層は、導電性粒子を含む層を介して、第1の導電層に電気的に接続されている。また、第2の樹脂層は、第1の樹脂層上に設けられている。

(もっと読む)

可撓性表示装置及びこの製造方法

【課題】可撓性表示装置の製造方法を提供する。

【解決手段】可撓性表示装置の製造方法は、キャリア基板上に抵抗を有する導電物質を含む発熱部を形成する段階と、発熱部上に可撓性基板を形成する段階と、可撓性基板上に薄膜トランジスタを含む駆動回路部を形成する段階と、駆動回路部上に発光素子および封止部材を形成する段階と、発熱部に電圧を印加してジュール熱を発生させることによって可撓性基板に直接熱を加えて発熱部から可撓性基板を分離する段階とを含む。

(もっと読む)

電界効果型トランジスタ、表示装置、センサ及び電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの移動度を向上させる。

【解決手段】ゲート絶縁膜22と、活性層としてSn,Zn及びO、又はSn,Ga,Zn及びOを主たる構成元素とする酸化物半導体層14と、ゲート絶縁膜22と酸化物半導体層14との間に配置され、酸化物半導体層14よりも抵抗率が高い酸化物中間層16と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、半導体素子、特にパワー半導体素子を提供する。

【解決手段】半導体基材100と、上記半導体基材100内の、半導体材料からなるドリフト領域2と、ドリフト領域2に対し、少なくとも部分的に隣り合って配置され、接続電極19を含む、半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3との間に配置された蓄積誘電体4と、第1素子領域8と、第1素子領域8との間にドリフト領域2が配置され、第1素子領域8から離れて配置された第2素子領域5と、ドリフト制御領域3の接続電極19および第1素子領域8の間に接続された容量性素子50とを含む。

(もっと読む)

表示装置

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】基板上に第1の材料層11を設け、前記第1の材料層11に接して第2の材料層12を設け、さらに積層成膜または500℃以上の熱処理やレーザー光の照射処理を行っても、剥離前の第1の材料層が引張応力を有し、且つ第2の材料層が圧縮応力であれば、物理的手段で容易に第2の材料層12の層内または界面において、きれいに分離することができる。

(もっと読む)

薄膜トランジスタ及びその製造方法、表示装置

【課題】低温プロセスで製造できる酸化物半導体を用いた高信頼性の薄膜トランジスタ及びその製造方法、表示装置を提供する。

【解決手段】薄膜トランジスタは、基板と、前記基板上に設けられ、インジウムを主成分とする酸化物で形成された半導体層140と、前記半導体層140のソース電極コンタクト領域およびドレイン電極コンタクト領域を除いた上面を覆う第1の絶縁膜と、少なくとも前記半導体層140の1対の側面を覆う、前記第1の絶縁膜と異なる条件で成膜された第2の絶縁膜と、前記絶縁膜上または前記半導体層140下に設けられたゲート電極120と、前記半導体層140のソース電極コンタクト領域上に設けられたソース電極161と、前記半導体層140のドレイン電極コンタクト領域上に設けられ、前記半導体層140の1対の側面を挟んで前記ソース電極161と対向するドレイン電極162と、を有する。

(もっと読む)

161 - 180 / 2,024

[ Back to top ]