Fターム[5F110NN73]の内容

Fターム[5F110NN73]に分類される特許

81 - 100 / 1,949

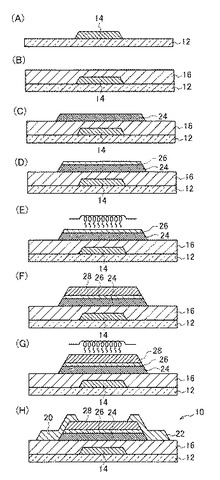

電界効果型トランジスタの製造方法、並びに、電界効果型トランジスタ、表示装置、イメージセンサ及びX線センサ

【課題】光照射時のTFT特性を安定化する。

【解決手段】ゲート電極14上に配置されたゲート絶縁層16上に、第一の酸化物半導体膜24を成膜する第一工程と、第一の酸化物半導体膜24とカチオン組成が異なり、且つ第一の酸化物半導体膜24より低い電気伝導度を有する第二の酸化物半導体膜26を成膜する第二工程と、酸化性雰囲気の下300℃超で熱処理する第三工程と、第一の酸化物半導体膜24とカチオン組成が異なり、且つ第一の酸化物半導体膜24より低い電気伝導度を有する第三の酸化物半導体膜28を成膜する第四工程と、酸化性雰囲気の下300℃超で熱処理する第五工程と、第三の酸化物半導体膜28上に、ソース電極20及びドレイン電極22を形成する電極形成工程と、を有している。

(もっと読む)

薄膜トランジスタアレイ基板、有機発光表示装置、及び薄膜トランジスタアレイ基板の製造方法

【課題】薄膜トランジスタアレイ基板、有機発光表示装置、及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】基板10上に配置され、活性層212、ゲート電極214、ソース電極218a、ドレイン電極218b、活性層とゲート電極との間に配置された第1絶縁層13、及びゲート電極とソース電極及びドレイン電極との間に配置された第2絶縁層15を含む薄膜トランジスタと、第1絶縁層及び第2絶縁層上に配置され、ソース電極及びドレイン電極のうち一つと連結される画素電極117と、ゲート電極と同一層で形成された下部電極314及び画素電極と同一材料を含む上部電極317を含むキャパシタと、第2絶縁層と画素電極との間及び下部電極と上部電極との間に直接配置された第3絶縁層116と、ソース電極、ドレイン電極及び上部電極を覆って画素電極を露出させる第4絶縁層19と、を含む薄膜トランジスタアレイ基板。

(もっと読む)

液晶表示装置及び電子機器

【課題】リフレッシュレートを低減した際に、静止画を表示する際の画像の劣化を抑制す

る。

【解決手段】駆動回路によって制御される表示部と、駆動回路を制御するためのタイミン

グコントローラと、を有し、タイミングコントローラには、静止画を表示するための画像

信号が供給されており、タイミングコントローラにより、画像信号の階調数が小さいほど

、表示部で画像信号に応じた画像を表示する際のリフレッシュレートを小さくする。

(もっと読む)

半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを

課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を

用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導

体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時

に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と該酸化物半導体膜と接する下地となる膜との界面の電子状態が良好なトランジスタ。

【解決手段】下地となる膜は酸化物半導体膜と同様の原子配列を有し、下地となる膜と酸化物半導体膜とが接している面において、面内の下地膜の最隣接原子間距離と酸化物半導体の格子定数の差を、下地となる膜の同面内における最隣接原子間距離で除した値は0.15以下、好ましくは0.12以下、さらに好ましくは0.10以下、さらに好ましくは0.08以下とする。例えば、立方晶系の結晶構造を有し(111)面に配向する安定化ジルコニアを含む下地となる膜上に酸化物半導体膜を成膜することで、下地となる膜の直上においても結晶化度の高い結晶領域を有する酸化物半導体膜が得られる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

液晶表示装置

【課題】非晶質半導体膜の結晶化工程において、非晶質半導体膜上に金属元素を導入して加熱処理を行なった、レーザアニールを行って得られた多結晶半導体膜を基に作製された薄膜トランジスタの電気的特性は非常に高いものとなるが、ばらつきが顕著になる場合がある。

【解決手段】非晶質半導体膜上に金属元素を導入して加熱処理を行なって連続的な結晶化領域の中に非晶質領域が点在する第1の多結晶半導体膜103bを得る。このとき、非晶質領域を所定の範囲に収めておく。そして、結晶化領域より非晶質領域にエネルギーを加えることができる波長域にあるレーザビームを第1の多結晶半導体膜103bに照射すると、結晶化領域を崩すことなく非晶質領域を結晶化させることができる。以上の結晶化工程を経て得られた第2の多結晶半導体膜を基にTFTを作製すると、その電気的特性は高く、しかもばらつきの少ないものが得られる。

(もっと読む)

半導体装置

【課題】半導体膜と電極又は配線との接触抵抗を低減し、かつ半導体膜と電極又は配線と

の被覆率を改善し、特性を向上させた半導体装置を得ることを課題とする。

【解決手段】基板上にゲート電極と、前記ゲート電極上にゲート絶縁膜と、前記ゲート絶

縁膜上に第1のソース電極又はドレイン電極と、前記第1のソース電極又はドレイン電極

上に島状半導体膜と、前記島状半導体膜及び前記第1のソース電極又はドレイン電極上に

第2のソース電極又はドレイン電極とを有し、前記第2のソース電極又はドレイン電極は

前記第1のソース電極又はドレイン電極と接触しており、前記第1のソース電極又はドレ

イン電極及び第2のソース電極又はドレイン電極が前記島状半導体膜を挟みこんでいる半

導体装置及びその作製方法に関するものである。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタ及びその作製方法を提供する。または、該トランジスタを含む信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】チャネル形成領域と、該チャネル形成領域を挟むように設けられ、チャネル形成領域よりも低抵抗な領域であるソース領域及びドレイン領域と、を含み、チャネル形成領域、ソース領域及びドレイン領域はそれぞれ結晶性領域を含む酸化物半導体層を有する半導体装置を提供する。

(もっと読む)

アクティブマトリクス基板及び液晶表示装置

【課題】 アクティブマトリクス基板の特性の向上、及び、白黒表示間のコントラストが向上した液晶表示装置を提供する。

【解決手段】 マトリクス状に配置された画素電極と、行方向に隣接する2つの画素電極の両方と重畳して配置された列方向に伸びるソース配線と、ソース配線と交差して配置された行方向に伸びる保持容量配線とを備えるアクティブマトリクス基板であって、上記画素電極、ソース配線及び保持容量配線は、絶縁膜を介してそれぞれ異なる層に形成されており、上記ソース配線は、行方向に隣接する2つの画素電極下にそれぞれ屈曲点を有し、かつ、行方向に隣接する2つの画素電極の間隙を横切る横断部を有し、上記保持容量配線は、行方向に隣接する2つの画素電極の間隙と重畳して配置された列方向に伸びる延伸部を有し、上記ソース配線は、実質的に保持容量配線との交差点でのみ保持容量配線と重畳しているアクティブマトリクス基板。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体膜を不活性ガス雰囲気化で加熱し、その後、酸化物半導体膜を酸素雰囲気化で加熱する。本工程によって、水素、水分、水酸基又は水素化物などの不純物を酸化物半導体膜より意図的に排除し、酸化物半導体膜を高純度化することができる。不純物を排除する際、酸化物半導体を構成する主成分材料である酸素が欠損する場合があるが、酸素雰囲気化で加熱することによって、酸素を供給することができる。

(もっと読む)

半導体装置

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜に、金属元素を含む膜と接した状態で加熱処理することにより導入された金属元素と、注入法により該金属元素を含む膜を通過して導入されたドーパントとを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

OLEDデバイスのための電流駆動型配置の提供

【課題】電流型アクティブマトリックスOLEDを改良すること。

【解決手段】電流型アクティブ・マトリックスOLEDデバイスの製造方法は、基板の上方に、半導体層と、導電層と、その半導体層と導電層の間に挟まれた絶縁層を設け;上記半導体層または上記導電層の上方に有機発光ダイオードを画素ごとに設け;第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成する操作を含んでいる。この方法は、第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;パルス式レーザーを用いて半導体層の特定の領域をアニーリングする操作も含んでいる。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信

頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】絶縁表面上において、ゲート絶縁膜を間に挟んでゲート電極上に酸化物半導

体膜を形成し、酸化物半導体膜上に、チタン、モリブデンまたはタングステンを含む第1

の導電膜を形成し、第1の導電膜上に、電気陰性度が水素より低い金属を含む第2の導電

膜を形成し、第1の導電膜及び第2の導電膜をエッチングすることでソース電極及びドレ

イン電極を形成し、酸化物半導体膜、ソース電極及びドレイン電極上に、酸化物半導体膜

と接する絶縁膜を形成する半導体装置の作製方法。

(もっと読む)

半導体装置

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加

する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有す

るICチップをボンディング等により実装することが困難となり、製造コストが増大する

という問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、駆動回路の少

なくとも一部の回路を、酸化物半導体を用いた逆スタガ型薄膜トランジスタで構成する。

同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層421と、ゲート電極層上に設けられるゲート絶縁層402と、ゲート絶縁層上に設けられる第1の酸化物半導体層442と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層443と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

半導体装置

【課題】ブラックマトリックス層の幅を設計値以上に拡張しなくても、位置合わせずれによる光漏れが生じることを抑制する。

【解決手段】ボトムゲート電極12aと第1のブラックマトリックス層17aで第1の半導体層14を挟むシングルゲート型の薄膜トランジスタを有する半導体装置であって、前記第1の半導体層と前記第1のブラックマトリックス層は重畳している半導体装置である。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の

影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置

を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電

極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トラン

ジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を

用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

81 - 100 / 1,949

[ Back to top ]