Fターム[5F110NN73]の内容

Fターム[5F110NN73]に分類される特許

161 - 180 / 1,949

電界効果型トランジスタ、表示装置、センサ及び電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタの移動度を向上させる。

【解決手段】ゲート絶縁膜22と、活性層としてSn,Zn及びO、又はSn,Ga,Zn及びOを主たる構成元素とする酸化物半導体層14と、ゲート絶縁膜22と酸化物半導体層14との間に配置され、酸化物半導体層14よりも抵抗率が高い酸化物中間層16と、を有する。

(もっと読む)

表示装置および電子機器

【課題】配線層を低抵抗に保ち、かつ薄膜トランジスタにおける膜剥がれを防止した表示装置および電子機器を提供する。

【解決手段】基板11上に薄膜トランジスタ10および配線層20を備える。薄膜トランジスタ10は、基板11側からゲート電極12,ゲート絶縁膜13および半導体層14を有し、配線層20は、配線層20aおよび配線層20bにより構成されている。配線層20bとゲート電極12とは同一の膜厚および構成材料からなる。配線層20とゲート電極12との厚みは異なっている。具体的には、ゲート電極12の厚みは配線層20の厚みよりも薄く、ゲート電極12の膜内応力が小さくなっている。

(もっと読む)

液晶表示装置

【課題】横電界方式で液晶層を駆動する液晶表示装置において、その画像表示性能を向上させる。

【解決手段】画素領域のそれぞれには、ドレイン信号線DLに接続された薄膜トランジスタTFTと、複数のスリットを有し且つ透明導電膜で形成される第1の電極と、前記薄膜トランジスタと前記第1の電極を接続する接続領域を有し、透明導電膜で形成される平面状の第2の電極を有し、前記第2の電極は、前記第1の電極と前記第1の基板間に形成され、且つ、前記第1の電極とゲート信号線GLに重畳し、さらに、隣接する前記画素領域の第2の電極と接続されていることを特徴とする液晶表示装置である。

(もっと読む)

ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

(もっと読む)

表示装置

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って歩留まりよく剥離することを可能とすることを目的としている。また、様々な基材に被剥離層を貼りつけ、軽量された半導体装置およびその作製方法を提供することを課題とする。特に、フレキシブルなフィルムにTFTを代表とする様々な素子を貼りつけ、軽量された半導体装置およびその作製方法を提供する。

【解決手段】基板上に第1の材料層11を設け、前記第1の材料層11に接して第2の材料層12を設け、さらに積層成膜または500℃以上の熱処理やレーザー光の照射処理を行っても、剥離前の第1の材料層が引張応力を有し、且つ第2の材料層が圧縮応力であれば、物理的手段で容易に第2の材料層12の層内または界面において、きれいに分離することができる。

(もっと読む)

EL表示装置

【課題】開口率の高い表示装置又は素子の面積の大きい半導体装置を提供することを課題

とする。

【解決手段】隣接する画素電極(又は素子の電極)の間に設けられた配線との下方にマル

チゲート構造のTFTのチャネル形成領域を設ける。そして、複数のチャネル形成領域の

チャネル幅の方向を前記画素電極の形状における長尺方向と平行な方向とする。また、チ

ャネル幅の長さをチャネル長の長さよりも長くすることでチャネル形成領域の面積を大き

くする。

(もっと読む)

表示装置および電子機器

【課題】安定した特性を有するセルフアライン構造の薄膜トランジスタを備えた表示装置、およびこの表示装置を備えた電子機器を提供する。

【解決手段】薄膜トランジスタ1の第1酸化物半導体膜20のソース領域20Sおよびドレイン領域20Dの上面から深さ方向における少なくとも一部に、チャネル領域20Aよりも酸素濃度が低い第1低抵抗領域21を設ける。基板11の薄膜トランジスタ1が設けられた領域以外の領域に第2酸化物半導体膜80を設け、上面から深さ方向における少なくとも一部に、チャネル領域20Aよりも酸素濃度が低い第2低抵抗領域81を設ける。薄膜トランジスタ1,第2酸化物半導体膜80および基板11を高抵抗膜50で覆い、この高抵抗膜50のうち、第1低抵抗領域21に接する領域に第1透光領域51を設け、第2低抵抗領域81に接する領域に第2透光領域52を設ける。

(もっと読む)

表示装置および半導体装置用Al合金膜

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、膜自体の電気抵抗(配線抵抗)も低く、アルカリ環境下の耐食性にも優れた表示装置用Al合金膜を提供する。

【解決手段】Geを0.01〜2.0原子%と、Ta、Ti、Zr、Hf、W、Cr、Nb、Mo、Ir、Pt、Re、およびOsよりなる群(X群)から選択される少なくとも一種の元素とを含み、450〜600℃の加熱処理を行なったとき、下記(1)の要件を満足する表示装置もしくは半導体装置用Al合金膜である。

(1)Alと、前記X群から選択される少なくとも一種の元素と、Geとを含む第1の析出物について、円相当直径50nm以上の析出物が200,000個/mm2以上の密度で存在する。

(もっと読む)

半導体装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安

価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピン

グ法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時

に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300

℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶

質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

薄膜トランジスタ及びその製造方法、表示装置

【課題】低温プロセスで製造できる酸化物半導体を用いた高信頼性の薄膜トランジスタ及びその製造方法、表示装置を提供する。

【解決手段】薄膜トランジスタは、基板と、前記基板上に設けられ、インジウムを主成分とする酸化物で形成された半導体層140と、前記半導体層140のソース電極コンタクト領域およびドレイン電極コンタクト領域を除いた上面を覆う第1の絶縁膜と、少なくとも前記半導体層140の1対の側面を覆う、前記第1の絶縁膜と異なる条件で成膜された第2の絶縁膜と、前記絶縁膜上または前記半導体層140下に設けられたゲート電極120と、前記半導体層140のソース電極コンタクト領域上に設けられたソース電極161と、前記半導体層140のドレイン電極コンタクト領域上に設けられ、前記半導体層140の1対の側面を挟んで前記ソース電極161と対向するドレイン電極162と、を有する。

(もっと読む)

液晶表示装置

【課題】動作性能および信頼性の高い液晶表示装置を提供する。

【解決手段】第1のチャネル形成領域713と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域714と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜664と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線668と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線672と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

TFT基板

【課題】アクティブマトリクス型の表示装置の作製工程又は完成品における静電気による不良の発生を抑制する。

【解決手段】本発明に係る表示装置は、アクティブマトリクス回路の角の部分に隣接して、前記アクティブマトリクス回路に接続されていない格子状の放電パターンが形成されていることを特徴とする。また、本発明に係る表示装置は、アクティブマトリクス回路の周辺に、前記アクティブマトリクス回路を構成するゲイト線又はソース線と交わる放電パターンが形成され、前記放電パターンの長さは、前記アクティブマトリクス回路の画素ピッチよりも長いことを特徴とする。これらにより、各種静電破壊によるアクティブマト

クス型表示装置の不良の発生を抑制することができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】半導体装置の作製工程において、フォトリソグラフィ工程数を削減する。

【解決手段】トランジスタの、ゲート電極となる導電膜、ゲート絶縁膜となる絶縁膜、チャネル領域が形成される半導体膜およびチャネル保護膜となる絶縁膜を連続で形成し、多階調マスクであるフォトマスクによって露光し現像したレジストマスクを用いて、(1)レジストマスクのない領域において、チャネル保護膜となる絶縁膜、チャネル領域が形成される半導体膜、ゲート絶縁膜となる絶縁膜およびゲート電極となる導電膜を連続してエッチングし、(2)レジストマスクをアッシングなどによって後退させ、レジストマスクを残膜厚が小さい領域のみを除去することで、チャネル保護膜となる絶縁膜の一部を露出させ、(3)露出したチャネル保護膜となる絶縁膜の一部をエッチングし、一対の開口部を形成する。

(もっと読む)

半導体装置

【課題】被剥離層に損傷を与えない剥離方法を提供し、小さな面積を有する被剥離層の剥離だけでなく、大きな面積を有する被剥離層を全面に渡って剥離することを可能とする。

【解決手段】基板上に金属層を形成する工程と、前記金属層上に酸化物層を形成する工程と、前記酸化物層上に絶縁層を形成する工程と、前記絶縁層上に薄膜トランジスタを形成する工程と、前記薄膜トランジスタ上に発光素子を形成する工程と、人間の手又は前記薄膜トランジスタを引き剥がす装置を用いることにより、前記酸化物層の層内または界面において前記基板から前記薄膜トランジスタを剥離する工程とを有する。

(もっと読む)

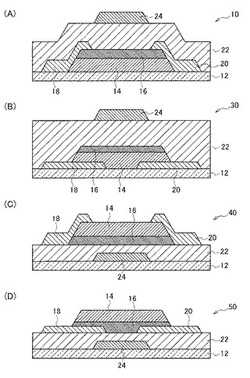

薄膜トランジスタおよびその製造方法、並びに表示装置

【課題】良好な伝達特性を有する薄膜トランジスタおよびその製造方法を提供する。

【解決手段】ゲート電極11およびゲート絶縁膜12上に酸化物半導体よりなるチャネル層13および導電性のチャネル保護膜をこの順に形成する。チャネル保護膜上にソース・ドレイン電極15A,15Bを形成したのち、チャネル保護膜をソース・ドレイン電極15A,15B間において電気的に分離(間隙14Cを形成)し、チャネル保護膜14A,14Bとする。チャネル保護膜を電気的に分離する工程において、チャネル層13を結晶酸化物半導体により形成するようにしたため、容易にチャネル層13とチャネル保護膜との選択的なエッチングを行うことができる。

(もっと読む)

薄膜トランジスタならびに表示装置および電子機器

【課題】多結晶酸化物半導体をチャネルとして用い、キャリアの移動度を保ちつつ、素子特性のばらつきを低減することが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ1は、ボトムゲート型のTFTであり、基板11上に、ゲート電極12、ゲート絶縁膜13、多結晶酸化物半導体を主成分とするチャネル層14およびソース・ドレイン電極15A,15Bをこの順に備えている。チャネル層14の膜厚は、チャネル層を構成する多結晶酸化物半導体の平均結晶粒の直径よりも薄くなるように形成することにより、キャリアの走行方向が制御され素子特性が安定化する。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製に用いるフォトリソグラフィ工程を従来よりも少なくし、且つ、信頼性の高い半導体装置を提供する。

【解決手段】第1の基板上に酸化物半導体層を有するトランジスタを含む回路と、当該第1の基板とシール材で固定された第2の基板とを有し、当該シール材、当該第1の基板、及び当該第2の基板で囲まれる閉空間は、減圧状態、或いは乾燥空気を充填する半導体装置に関する。当該シール材は、少なくとも前記トランジスタを囲み、閉じられたパターン形状を有する。また当該回路は、酸化物半導体層を有するトランジスタを含む駆動回路である。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製及び表示装置の作製に用いるフォトマスクの枚数を従来よりも少なくすることを課題の一とする。

【解決手段】ゲート電極を形成する工程と、島状半導体層を形成するための工程を、1回のフォトリソグラフィ工程で行い、平坦化絶縁層を形成した後、コンタクトホールを形成する工程を1回のフォトリソグラフィ工程で行い、ソース電極及びドレイン電極を形成する工程と画素電極を形成する工程を1回のフォトリソグラフィ工程で行い、合計3回のフォトリソグラフィ工程で表示装置を作製する。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

161 - 180 / 1,949

[ Back to top ]