Fターム[5F110PP01]の内容

Fターム[5F110PP01]の下位に属するFターム

ランプ(例;RTA) (805)

レーザ (4,317)

電子ビーム (10)

Fターム[5F110PP01]に分類される特許

141 - 160 / 1,217

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2

の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上

に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を

有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第

3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のド

ーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】アモルファス半導体膜の結晶化を低温で短時間に行うことができ、大粒径の結晶粒を形成することが可能な半導体装置の製造方法を提供する。

【解決手段】実施形態による半導体装置の製造方法では、基板上にアモルファス半導体膜を形成する。さらに、前記方法では、前記基板上にマイクロ波を照射することにより、前記アモルファス半導体膜をアニールして、前記アモルファス半導体膜から多結晶半導体膜を形成する。さらに、前記方法では、前記多結晶半導体膜をチャネルとするトランジスタを形成する。

(もっと読む)

半導体素子の作製方法

【課題】閾値電圧が制御され、動作速度が速く、製造工程が比較的簡単であり、十分な信

頼性を有する、酸化物半導体を用いた薄膜トランジスタ、及び薄膜トランジスタの作製方

法を提供することを課題の一つとする。

【解決手段】酸化物半導体層に含まれるキャリア濃度に影響する不純物、例えば、水素原

子や、H2Oなど水素原子を含む化合物を排除すればよい。酸化物半導体層に接して未結

合手に代表される欠陥を多く含む酸化物絶縁層を形成し、当該酸化物絶縁層に不純物を拡

散させ、上記酸化物半導体層中の不純物濃度を低減すればよい。また、酸化物半導体層、

又は酸化物半導体層に接する酸化物絶縁層を、クライオポンプを用いて排気して不純物濃

度が低減された成膜室内で成膜すればよい。

(もっと読む)

表示装置

【課題】簡便な構成及び動作によって表示装置の消費電力を低減すること。

【解決手段】表示装置が入力デバイスを備え、該入力デバイスから出力される画像操作信号に応じて、駆動回路に対する画像信号の入力を制御する。具体的には、入力デバイスが操作されない際の画像信号の入力頻度を、入力デバイスが操作される際の画像信号の入力頻度よりも低くする。これにより、当該表示装置が使用される際の表示の劣化(表示品質の低下)を抑制することが可能となり、且つ使用されない際の消費電力を低減することが可能になる。

(もっと読む)

半導体装置

【課題】可撓性を有し、曲げ等の物理的変化に対して耐性を有する半導体装置および当該

半導体装置の作製方法を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた、半導体膜、半導体膜上にゲート絶縁膜

を介して設けられたゲート電極およびゲート電極を覆って設けられた層間絶縁膜とを有す

る複数のトランジスタと、複数のトランジスタの間に設けられた屈折部分とを有し、屈折

部分は、層間絶縁膜に設けられた開口部に層間絶縁膜より弾性率が低い物質が充填されて

設けられている。また、本発明では、開口部に充填する物質として他にも、層間絶縁膜よ

りガラス転移点が低い物質や塑性を有する物質を設けることができる。

(もっと読む)

半導体装置

【課題】カラーフィルタに含まれる不純物による汚染の問題を解決する。

【解決手段】薄膜トランジスタと、薄膜トランジスタに電気的に接続されるソース電極及

びドレイン電極と、薄膜トランジスタ、ソース電極及びドレイン電極上の第1の絶縁膜と

、第1の絶縁膜上のカラーフィルタと、カラーフィルタ上の第2の絶縁膜と、第2の絶縁

膜上の画素電極とを有し、第1の絶縁膜は窒化シリコンを有し、カラーフィルタは第1の

開口部を有し、第2の絶縁膜は第2の開口部を有し、第2の開口部は第1の開口部の内側

に設けられ、画素電極は、第1の開口部及び第2の開口部を介してソース電極及びドレイ

ン電極の一方に電気的に接続され、カラーフィルタは、画素電極、ソース電極及びドレイ

ン電極に接触しない。

(もっと読む)

記憶素子および信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる記憶装置、当該記憶装置を用いた信号処理回路を提供する。

【解決手段】インバータまたはクロックドインバータなどの、入力された信号の位相を反転させて出力する位相反転素子を用いた記憶素子内に、データを保持するための容量素子と、当該容量素子における電荷の蓄積および放出を制御するスイッチング素子とを設ける。上記スイッチング素子には、アモルファスシリコン、ポリシリコン、微結晶シリコン、あるいは酸化物半導体等の化合物半導体をチャネル形成領域に含み、そのチャネル長が最小加工線幅の10倍以上あるいは、1μm以上であるトランジスタを用いる。上記記憶素子を、信号処理回路が有する、レジスタやキャッシュメモリなどの記憶装置に用いる。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置

を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく

作製することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層、ソース領域及びドレイン領域を酸化物半

導体層とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体層

の純度を高め、不純物である水分などを低減する加熱処理(脱水化または脱水素化のため

の加熱処理)を行う。

(もっと読む)

酸化物半導体膜の形成方法および半導体装置の作製方法

【課題】良好な半導体特性を有する酸化物半導体膜の形成方法を提供する。さらに、該酸化物半導体膜を適用し、良好な電気特性を有する半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜を形成し、酸化物半導体膜上に接して設けられた水素透過膜を形成し、水素透過膜上に接して設けられた水素捕縛膜を形成し、加熱処理を行うことで、前記酸化物半導体膜から水素を脱離させる酸化物半導体膜の形成方法である。また、該形成方法を用いて作製する半導体装置の作製方法である。

(もっと読む)

記憶回路、記憶装置、信号処理回路

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶回路の提供、消費電力の低減可能な信号処理回路を提供する。

【解決手段】記憶回路は、トランジスタと、容量素子と、第1の演算回路と、第2の演算回路と、第3の演算回路と、スイッチと、を有し、第1の演算回路の出力端子は、第2の演算回路の入力端子と電気的に接続され、第2の演算回路の入力端子は、スイッチを介して第3の演算回路の出力端子と電気的に接続され、第2の演算回路の出力端子は、第1の演算回路の入力端子と電気的に接続され、第1の演算回路の入力端子は、トランジスタのソース及びドレインの一方と電気的に接続され、トランジスタのソース及びドレインの他方は、容量素子の一対の電極のうちの一方、及び第3の演算回路の入力端子と電気的に接続され、トランジスタのチャネルは酸化物半導体層に形成される。

(もっと読む)

半導体装置及び電子器具

【課題】 可撓性を有するアクティブマトリクス型表示装置を実現する方法を提供することを課題とする。また、異なる層に形成された配線間の寄生容量を低減する方法を提供することを課題とする。

【解決手段】 第1の基板上に形成された薄膜デバイスと第2の基板とを接着して固定した後、第1の基板を取り除いて薄膜デバイスに配線等を形成する。その後、第2の基板も取り除き、可撓性を有するアクティブマトリクス型表示装置を形成する。また、第1の基板を取り除いた後、配線を活性層のゲート電極が形成されていない側に形成することにより、寄生容量を低減することができる。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリを提供する。

【解決手段】ビット線と、ソース線と、複数の不揮発性メモリが直列に接続されたNAND型セルと、選択トランジスタと、を有し、不揮発性メモリは、第1の絶縁膜を介した半導体上の電荷蓄積層と、第2の絶縁膜を介した電荷蓄積層上の制御ゲートと、を有し、NAND型セルの一方の端子は、選択トランジスタを介して、ビット線に接続され、NAND型セルの他方の端子は、ソース線に接続されたNAND型不揮発性メモリであって、第1の絶縁膜は、半導体に酸素雰囲気で高密度プラズマ処理を行った後、窒素雰囲気で高密度プラズマ処理を行うことで形成されるNAND型不揮発性メモリ。

(もっと読む)

表示装置、液晶表示装置及びプロジェクター

【課題】高開口率な半導体装置を提供する。

【解決手段】絶縁表面上に第1配線と、第1配線上に第1絶縁膜と、第1絶縁膜上に半導体膜と、半導体膜上に第2絶縁膜と、第2絶縁膜上に第2配線と、第1配線と接続するゲート電極と、第2配線及びゲート電極上に第3絶縁膜と、第3絶縁膜上に半導体膜と接続する第3の配線とを有する半導体装置。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を介して対向する一対の第2の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられるゲート絶縁膜と、ゲート絶縁膜上に設けられて、かつ第1の領域に重畳する第1の電極と、を有し、第1の領域は、c軸配向した結晶部を有する非単結晶の酸化物半導体領域であり、一対の第2の領域は、ドーパントを含んで、かつ複数の結晶部を有する酸化物半導体領域であることを特徴とする半導体装置である。

(もっと読む)

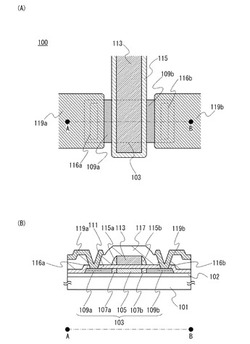

フィン型電界効果トランジスタ

【課題】フィン型電界効果トランジスタはその動作原理から、低消費電力化を図るためには、動作時のバルク領域は完全空乏化される必要があった。結果として、プロセスばらつきがバルク領域のばらつきを生み、消費電力にばらつきを与えるという問題が生じていた。

【解決手段】本発明のフィン型電界効果トランジスタは、ゲート絶縁膜を介してチャネル領域に電界を印加するためのゲート電極を備えるフィン型電界効果トランジスタにおいて、バルク領域に所定の電位を印加するためのバルク電極を、ゲート電極と別に備えられている。このような構造にすることで、フィンの幅を空乏層程度に保つことを必要せず、基板電位を変化させることでデバイスの特性を変化させる、基板バイアス効果によって消費電力を削減することが可能となる。

(もっと読む)

半導体装置及びその作製方法

【課題】しきい値電圧の制御が困難な酸化物半導体を活性層に用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】一対の第1の領域、一対の第2の領域及び第3の領域を有する酸化物半導体膜と、酸化物半導体膜と接して設けられる一対の電極と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介し、一対の電極の間に設けられたゲート電極と、を有し、一対の第1の領域は一対の電極と重畳し、第3の領域はゲート電極と重畳し、一対の第2の領域は一対の第1の領域及び第3の領域の間に形成され、一対の第2の領域及び第3の領域には窒素、リン、または砒素のいずれかの元素が含まれており、該元素の濃度は、第3の領域より一対の第2の領域のほうが高い構成とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置の提供。

【解決手段】酸化物半導体材料を用いたトランジスタ162と、酸化物半導体以外の半導体材料を用いたトランジスタ160を組み合わせて用いることにより、書き込み回数にも制限が無く、長期間にわたる情報の保持ができる、新たな構造の半導体装置を実現することができる。さらに、酸化物半導体以外の半導体材料を用いたトランジスタと酸化物半導体材料を用いたトランジスタとを接続する接続電極130bを、当該接続電極と接続する酸化物半導体以外の半導体材料を用いたトランジスタの電極129より小さくすることにより、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることができる。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】新たな構造の半導体装置を提供し、書き込み後の当該半導体装置のメモリセルのしきい値電圧のばらつきを小さくし、動作電圧を低減する、または記憶容量を増大する。

【解決手段】酸化物半導体を用いたトランジスタと、酸化物半導体以外の材料を用いたトランジスタとをそれぞれ有する複数のメモリセルと、複数のメモリセルを駆動する駆動回路と、駆動回路に供給する複数の電位を生成する電位生成回路と、複数のメモリセルへのデータの書き換えが終了したか否かを検知する書き込み終了検知回路と、を有し、駆動回路は、データバッファと、複数のメモリセルのそれぞれに複数の電位のうちいずれか一の電位をデータとして書き込む書き込み回路と、メモリセルに書き込まれたデータを読み出す読み出し回路と、読み出されたデータと、データバッファに保持されたデータとが一致するか否かをベリファイするベリファイ回路と、を有する。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

141 - 160 / 1,217

[ Back to top ]