Fターム[5F110PP05]の内容

Fターム[5F110PP05]に分類される特許

61 - 80 / 661

表示装置

【課題】本発明では、高画質で信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】本発明は、画素領域における画素電極層上、及び画素電極層周辺を覆う隔壁として機能する絶縁層上に、スペーサを有する。このスペーサによって、発光材料を画素電極層上に形成する際、選択的に形成するためのマスクは支持され、マスクのよじれやたわみなどによって画素電極層に接することを防止する。よって、画素電極層にはマスクによる傷などの損傷が生じず、画素電極層は形状不良とならないので、高繊細な表示を行う、高信頼性な表示装置を作製することができる。

(もっと読む)

半導体装置の作製方法

【課題】基板裏面からの二次ビームを原因とする干渉の影響を抑え、被照射物を均一にレーザアニールすることができ、且つスループットが良好である半導体装置の作製方法を提供する。

【解決手段】基板上に形成された半導体膜に、少なくとも1つのガルバノミラーとfθレンズとを用いた光学系を用いてパルス発振のレーザビームを照射する半導体装置の作製方法であって、前記基板の屈折率をn、前記基板の厚さをd(メートル)、真空中の光速をc(メートル/秒)とした場合に、前記レーザビームのパルス幅であるt(秒)を、t<2nd/cという式により算出し、前記レーザビームのパルス幅を前記算出したtの範囲から選択して、前記レーザビームを照射する。

(もっと読む)

半導体装置

【課題】遮光層の端部で回折した光が半導体層に照射されTFT特性の変動を引き起こしているため、この光の照射を防止する事により、高い表示品質をもつ液晶表示装置を提供する。

【解決手段】第3の遮光層108の端部で回折した光117を完全に遮光するため、半導体層103をゲート電極104と第2の遮光部106とで覆うことによって、回折した光の照射を防止し、TFT特性の変動を回避でき、良好な表示画像を得る事ができる。

(もっと読む)

半導体装置

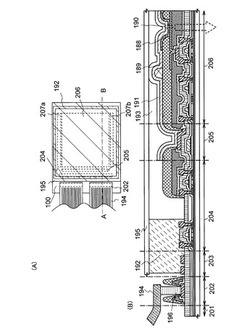

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、および表示装置

【課題】信頼性を向上させると共に、電気的特性を改善することができる薄膜トランジスタの製造方法を提供する。

【解決手段】ガラス基板11上に成膜された非晶質シリコン膜20に、ガラス基板11の裏面側からレーザ光を照射することによって、縦成長モードで多結晶シリコン膜30を形成する。多結晶シリコン膜30は、溶融した半導体の表面に高い密度で形成された種結晶からガラス基板11側に向かって固化することにより形成される。これにより、多結晶シリコン膜30の表面付近には、微結晶シリコン領域を多く含む不完全結晶層32が形成される。そこで、不完全結晶層32をエッチングにより除去して、多結晶シリコン膜33を形成し、多結晶シリコン膜33を活性層とするTFTを製造する。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】絶縁表面上に設けられたnチャネル型TFTを有する半導体装置は、半導体膜が引っ張り応力を受けるように、導電膜、例えばゲート電極に不純物元素が導入され、絶縁表面上に設けられたpチャネル型TFTを有する半導体装置は、半導体膜が圧縮応力を受けるように、導電膜、例えばゲート電極に不純物が導入されている。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

表示装置及びプロジェクター

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

薄膜トランジスタ、その製造方法、及びこれを含む表示装置

【課題】不完全結晶成長領域を含まない多結晶シリコンでゲート電極または遮光部材のような金属パターン上に位置する半導体層を形成することにより、駆動特性及び信頼性を向上させる薄膜トランジスタ、その製造方法、及びこれを含む表示装置を提供する。

【解決手段】多結晶シリコンで形成された半導体層142を含む薄膜トランジスタにおいて、前記半導体層と基板110との間に前記半導体層と絶縁するように位置する金属パターンをさらに含み、前記半導体層の多結晶シリコンは、結晶成長方向と平行な結晶粒界を含み、表面における波状線の最大ピークと最小ピークとの間の距離として定義される表面粗度が15nm以下である。

(もっと読む)

半導体装置及び電子機器

【課題】駆動回路の低駆動電圧化に対応し、入力信号の電圧振幅が小さい場合にも十分な振幅変換能力を有するレベルシフタを提供する。

【解決手段】信号の電圧振幅の変換部分に、カレントミラー回路150および差動回路160を利用したレベルシフタを用いる。トランジスタ105、106を介して差動回路160に入力された信号の電位差を増幅して出力するため、入力信号の電圧振幅が小さい場合にも、トランジスタのしきい値の影響を受けることなく、正常な電圧振幅の変換を可能とする。

(もっと読む)

結晶性半導体膜の形成方法、および、半導体デバイスの製造方法

【課題】結晶粒界の方向とチャネル領域の方向とが直交しているトランジスタの性能を向上させるとともに、各トランジスタの特性のバラツキを少なくする。

【解決手段】本発明の結晶性半導体膜の形成方法は、基板11上にアモルファスシリコン膜(非晶質半導体膜)12を形成する工程と、第1のレーザ光20aおよび基板11のうちの少なくとも一方を移動させながら、アモルファスシリコン膜12に対して第1のレーザ光20aを照射し、その移動方向に沿って半導体膜の結晶を成長させてアモルファスシリコン膜12から多結晶シリコン膜(結晶性半導体膜)13を得る工程と、多結晶シリコン膜13に対して、第1のレーザ光20aよりもエネルギー量の小さい第2のレーザ光30aを照射して、半導体膜の厚さ方向に対して結晶を成長させて、再結晶化後の多結晶シリコン膜(結晶性半導体膜)14を得る工程と、を含む。

(もっと読む)

表示デバイスおよびその製法、ならびにスパッタリングターゲット

【課題】アルミニウム合金膜と透明電極が直接コンタクトすることを可能とし、バリアメタルの省略を可能にするアルミニウム合金膜を用いた表示デバイスとその製造技術を提供すること。

【解決手段】ガラス基板上に配置された薄膜トランジスタと、透明電極によって形成された画素電極と、これら薄膜トランジスタと画素電極を電気的に接続するアルミニウム合金膜によって形成された接続配線部を主たる構成要素として備えた表示デバイスとその製法を開示する。

(もっと読む)

半導体装置及びその作製方法

【課題】プラスチックフィルム基板などの柔軟性を有するフレキシブル基板に転写後のデバイスに対してFPCを圧着する際、クラック等の不良発生を防止する。

【解決手段】転写する被剥離層として、素子を有する回路を含む層405aと、端子電極405bとを形成し、その上にクラックを防止するための樹脂からなる保護層405cを形成す。FPCの接続を行う部分において、端子電極の電極面が露出している。FPC407を圧着して異方性導電フィルム406により接続を行う。この圧着工程において、保護層405cによって配線が保護されているため、加圧変形によるクラックの発生を防止することができる。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置及びその製造方法、発光装置並びに電子機器

【課題】チャネル保護層に対するソース、ドレイン電極及び不純物層のアライメントずれが生じた場合であっても、オン電流特性のばらつきを抑制することができる半導体装置及びその製造方法を提供する。また、製品の歩留まりを向上させることができるとともに、良好な画質を有する発光装置、並びに、該発光装置を実装した電子機器を提供する。

【解決手段】薄膜トランジスタTFTの半導体層14上に設けられるチャネル保護層15と、ソース、ドレイン電極18及び不純物半導体層17との間に、カーボン絶縁膜16が設けられている。半導体層14は、例えば非晶質シリコンをレーザーアニール処理することにより結晶化された微結晶シリコンにより形成されている。カーボン絶縁膜16は、このレーザーアニール処理において適用される光熱変換層であり、当該光熱変換層の一部を残したものである。

(もっと読む)

半導体装置及びその製造方法

【課題】リーク電流が低く、電界効果移動度が高いなどの優れた特性を有するTFTを備え、駆動回路を内蔵して部材点数を減らすことが可能な半導体装置において、駆動回路内部における腐食などの発生を防止する。

【解決手段】本発明の半導体装置においては、駆動回路を内蔵したTFTアレイ基板100に、ゲート電極2と、ゲート絶縁膜3と、結晶性半導体部分を含んでチャネル領域4cが形成される半導体層4と、チャネル領域4cを保護するチャネル保護膜5と、半導体層4に接続されたソース電極6及びドレイン電極7を備えたTFT、並びに、ゲート電極2と同層に形成された配線層2aとソース電極6と同層に形成された配線層6aを駆動回路内部においてコンタクトホール13を介し直接接触させて接続させる配線変換部12を備えるものである。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレイン電極と半導体膜とのコンタクト不良を抑制することが可能な半導体装置等を提供する。

【解決手段】両端部30s、30dの膜厚が平坦部30cの膜厚よりも厚い半導体膜30を形成する。ゲート絶縁膜40は、両端部30s、30dが露出されるように形成される。両端部30s、30dには、ソース・ドレイン電極50s、50dとソース・ドレイン領域とを接続する中間電極50s、50dが形成され、この中間電極50s、50dまで開口するコンタクトホールが形成される。

(もっと読む)

半導体装置の作製方法

【課題】結晶粒の位置とその大きさを制御した結晶質半導体膜を作製し、さらにその結晶質半導体膜をTFTのチャネル形成領域に用いることにより高速動作を可能にする。

【解決手段】基板1上に、島状で且つ端部にテーパーを有する膜2を設け、無機絶縁膜3、非晶質半導体膜を形成する。そして、レーザーアニールにより非晶質半導体膜を結晶化させる。島状で且つ端部にテーパーを有する膜2または無機絶縁膜3の材料及び膜厚を適宜調節することによって半導体膜の冷却速度を遅くして結晶粒径の大きな第1領域4aを形成する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】レーザを照射して薄膜トランジスタに用いる微結晶薄膜を形成する工程において、結晶性の周期的な劣化を回避し、安定して均一性能の微結晶膜を形成することができる平面表示装置の製造方法を提供する。

【解決手段】連続発振レーザ光を非晶質シリコン膜表面に照射し、一定の速度でレーザを基板に対して相対的に走査しながら結晶化する際に、非晶質シリコン膜の一領域あたりへのレーザ照射時間が0.1ms以上となるように走査し、結晶化を行う。

(もっと読む)

61 - 80 / 661

[ Back to top ]