Fターム[5F110PP16]の内容

Fターム[5F110PP16]に分類される特許

1 - 20 / 28

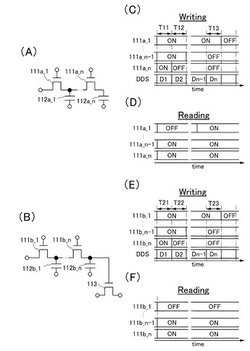

半導体装置及び半導体記憶装置

【課題】ノイズによるデータ信号への影響を抑制する半導体記憶装置を提供する。

【解決手段】記憶回路を具備し、記憶回路は、それぞれが電界効果トランジスタであり、1個目の電界効果トランジスタ111a−1のソース及びドレインの一方にデジタルデータ信号が入力され、k個目(kは2以上n(nは2以上の自然数)以下の自然数)の電界効果トランジスタのソース及びドレインの一方がk−1個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続されるn個の電界効果トランジスタと、それぞれ一対の電極を有し、m個目(mはn以下の自然数)の容量素子の一対の電極の一方が、n個の電界効果トランジスタのうち、m個目の電界効果トランジスタのソース及びドレインの他方に電気的に接続され、少なくとも2つの容量素子における容量値が異なるn個の容量素子112aー1〜112aーnとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

半導体装置の作製方法

【課題】金属元素を用いた結晶化法において、ゲッタリングのために必要な不純物元素の濃度が高く、その後のアニールによる再結晶化の妨げとなり問題となっている。

【解決手段】

本発明は半導体膜に、希ガス元素を添加した不純物領域を形成し、加熱処理およびレーザアニールにより前記不純物領域に半導体膜に含まれる金属元素を偏析させるゲッタリングを行なうことを特徴としている。そして、半導体膜が形成された基板(半導体膜基板)の上方または下方からレーザ光を照射してゲート電極を加熱し、その熱によってゲート電極の一部と重なる不純物領域を加熱する。このようにして、ゲート電極の一部と重なる不純物領域の結晶性の回復および不純物元素の活性化を行なうことを可能とする。

(もっと読む)

逆スタガ構造の薄膜トランジスタ及びその製造方法

【課題】生産性を向上させ、かつトランジスタ特性が良好な逆スタガ構造の薄膜トランジスタ及びその製造方法を提供すること。

【解決手段】本発明にかかる逆スタガ構造の薄膜トランジスタは、ソース領域41、ドレイン領域42、及びチャネル領域43を有する結晶性半導体膜40を備える。また、薄膜トランジスタは、チャネル領域43上に形成された絶縁膜5と、ソース領域41及びドレイン領域42上に形成されたシリサイド層61とを備える。そして、チャネル領域43は、ソース領域41及びドレイン領域42における結晶粒よりも小さい結晶粒により構成される。

(もっと読む)

半導体装置

【課題】本発明は、駆動力を向上させることができるFin状の半導体部を有する半導体装置を提供することを目的とする。

【解決手段】本発明に係る1つの実施の形態による半導体装置は、Fin状の半導体部3と、ゲート電極8と、ライナー膜9とを備える。Fin状の半導体部3は、一方にソース領域、他方にドレイン領域が形成される。ゲート電極8は、ソース領域とドレイン領域との間で、Fin状の半導体部3をゲート絶縁膜を介して囲むように形成される。ライナー膜9は、ゲート電極7を被うように形成され、少なくともFin状の半導体部3の高さ方向に応力を印加する。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】膜厚バラツキを抑制し、かつドライエッチングダメージの発生を抑制できる優れた素子特性を兼ね備えた薄膜半導体装置及びその製造方法を提供すること。

【解決手段】透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜及びゲート電極、前記ゲート電極の側壁に形成された、低温酸化膜、低温窒化膜及び低温酸化膜の3層構造のサイドウォールスペーサー、及び島状半導体層及びゲート電極を覆う層間絶縁膜を具備することを特徴とする。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 優れたコンタクト特性及び優れた素子特性を持った薄膜半導体装置及びその製造方法を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて不純物を含むソース領域ドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成されたコンタクト孔内にそれぞれ埋め込まれた不純物を含む多結晶半導体層、及び前記多結晶半導体層に接続する高融点金属層を含む配線層を具備し、前記多結晶半導体層と配線層の高融点金属層との間には、高融点金属と半導体との化合物からなる薄層が形成されていることを特徴とする。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

半導体装置

【課題】高いgm(高いオン電流)を発揮し、比較的簡素な構成でSi−MOSFETに匹敵する特性を有する半導体装置を実現する。

【解決手段】非晶質透明基板と、前記非晶質透明基板上に形成された動作半導体薄膜と、前記非晶質透明基板上において、前記動作半導体薄膜の上下にそれぞれ絶縁膜を介して同一の金属材料から形成されてなる上部ゲート電極及び下部ゲート電極とを含み、動作半導体薄膜のチャネル領域が微結晶シリコン半導体からなり、ソース・ドレイン領域が多結晶シリコンからなる半導体装置。

(もっと読む)

薄膜半導体装置の製造方法

【課題】良好なシリサイド/シリコン界面の形成、低抵抗のソース・ドレイン領域及びコンタクトの形成、及び急峻な不純物分布の形成を可能とする薄膜半導体素子を製造する方法を提供する。

【解決手段】透明絶縁性基板10上に結晶化半導体膜15を形成し、その上にゲート絶縁膜24及びゲート電極19を形成する。得られた構造の表面に高融点金属膜25を形成した後、前記高融点金属膜25を介してSi又はGeを導入して前記結晶化半導体膜15の表面近傍を非結晶化する。前記ゲート電極19をマスクとして前記結晶化半導体膜15のソース及びドレイン予定領域に不純物を導入した後、熱処理して前記結晶化半導体膜15と前記高融点金属膜25との界面にシリサイド膜を形成する第1の熱処理工程を具備するとともに、前記導入された不純物を活性化し、前記結晶化半導体膜15にソース領域及びドレイン領域を形成する第2の熱処理工程を具備する。

(もっと読む)

半導体装置、その製造方法、及び表示装置

【課題】開口率を向上させることができる半導体装置を提供すること。

【解決手段】本発明に係る半導体装置は、基板上の所望の位置に形成される遮光層41と、遮光層41及び基板20上に形成される下地膜21と、下地膜21上に形成され、ソース領域及びドレイン領域並びにチャネル領域を有する第1の半導体領域31及び第2の半導体領域42と、第1の半導体領域31及び第2の半導体領域42上に形成されたゲート絶縁膜22と、ゲート絶縁膜22上に、第1の半導体領域31及び第2の半導体領域42と対向する位置にそれぞれ形成されたゲート電極を備え、第1の半導体領域42のチャネル領域は遮光層41と対向する位置に形成され、非晶質半導体からなり、第2の半導体領域31のチャネル領域は多結晶半導体からなる。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 基板の歪を生ずることなく、不純物領域の不純物の活性化率を向上させ、優れた特性の薄膜半導体装置を製造することを可能とする薄膜半導体装置の製造方法を提供すること。

【解決手段】 絶縁性基板上に非単結晶半導体層を形成する工程と、前記非単結晶半導体層にレーザー光を照射して結晶化領域を形成する工程と、前記結晶化領域上にゲート絶縁膜及びゲート電極を形成する工程と、前記結晶化領域の所定の位置の上層部を非結晶化するプリアモルファス化工程と、前記結晶化領域の所定の位置に不純物をドーピングする工程と、熱処理により前記結晶化領域の所定の位置にソース領域及びドレイン領域を形成する工程とを具備することを特徴とする。

(もっと読む)

表示装置

【課題】画素の開口率の向上を図った表示装置の提供。

【解決手段】基板上の画素領域に、透明酸化物層、絶縁膜、導電層が順次積層され、

前記導電層はゲート信号線に接続される薄膜トランジスタのゲート電極を有し、

前記透明酸化物層は少なくとも前記ゲート電極の直下のチャネル領域部を除いた他の領域が導電体化され、この導電体化された部分でソース信号線、このソース信号線に接続される前記薄膜トランジスタのソース領域部、画素電極、この画素電極に接続される前記薄膜トランジスタのドレイン領域部を構成している。

(もっと読む)

応力印加チャネル領域を有する電界効果トランジスタを備えた半導体構造の形成方法

半導体構造の製造方法は、第1トランジスタ素子および第2トランジスタ素子を有する半導体基板を提供するステップを有する。前記第1トランジスタ素子は少なくとも1つの第1アモルファス領域を含み、前記第2トランジスタ素子は少なくとも1つの第2アモルファス領域を含む。前記第1トランジスタ素子の上に応力発生層が形成される。前記応力発生層は、前記第2トランジスタ素子は覆わない。第1アニールプロセスが実施される。前記第1アニールプロセスは、前記第1アモルファス領域および前記第2アモルファス領域を再結晶化させるために適合されている。前記第1アニールプロセス後に、第2アニールプロセスが実施される。前記第2アニールプロセス中は、前記応力発生層が前記基板上に残されている。  (もっと読む)

(もっと読む)

カルコゲナイド層を持つ薄膜トランジスタ及びその製造方法

【課題】カルコゲナイド層を有する薄膜トランジスタ及びその製造方法を提供する。

【解決手段】チャンネル層を構成する非晶質のカルコゲナイド層と、非晶質のカルコゲナイド層の両側部にそれぞれ形成されてソース及びドレイン領域を構成する結晶質のカルコゲナイド層と、結晶質のカルコゲナイド層に連結されたソース電極及びドレイン電極と、非晶質のカルコゲナイド層の上部または下部に、ゲート絶縁層を介在して形成されたゲート電極とを備える薄膜トランジスタである。これにより、カルコゲナイド層を光伝導層として利用して光薄膜トランジスタを具現したり、非晶質のカルコゲナイド層と結晶質のカルコゲナイド層とによって、ダイオード整流機能を具備する電気薄膜トランジスタを具現できる。

(もっと読む)

insituまたはexsitu熱処理と組み合わされた改良型電界効果トランジスタ向けのイオン注入(FETデバイスを製造する方法およびFETデバイス)

【課題】所望のドーパント密度プロファイルを達成することができ、アモルファス化される層の厚さが十分に限定され、または歪み緩和のレベルが十分に低く、あるいはこれらがともに達成されるイオン注入法を提供することにある。

【解決手段】本発明は、イオン注入ステップをin situまたはex situ熱処理と組み合わせて、注入誘起性のアモルファス化(超薄シリコン・オン・インシュレータ層のFETのソース/ドレイン(S/D)領域の潜在的な問題)、および歪まされたS/D領域の注入誘起性の塑性緩和(その下の基板層と格子不整合の状態にある埋込みS/D領域によってチャネル歪みが誘起される歪みチャネルFETの潜在的な問題)をともに回避し、またはともに最小化し、あるいは一方を回避し、もう一方を最小化する方法を教示する。第1の実施形態では、イオン注入を高温で実行することによって、イオン注入がin situ熱処理と組み合わされる。第2の実施形態では、熱注入を実行する能力を有する手段を必要としない「デバイデッド−ドーズ−アニール−イン−ビトウィーン」(DDAB)法において、イオン注入がex situ熱処理と組み合わせられる。

(もっと読む)

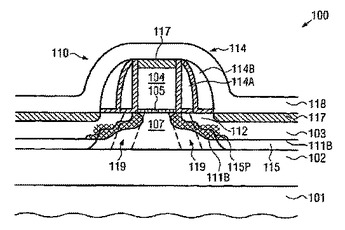

ボディポテンシャルが低減したSOIトランジスタとその製造法

炭素、フッ素などの原子種(111B)をドレイン及びソース領域(115、206)とボディ領域(107、207)とに導入することで、SOIトランジスタ(110、210M)の接合部のリークが著しく増加し、これにより、蓄積した少数電荷キャリアに対してリークパス(119、219A)が強化される。これにより、ボディポテンシャルの変動が著しく減り、その結果、最新のSOIデバイス(100)の全体のパフォーマンスが向上する。具体的な実施形態では、このメカニズムは、スタティックRAM領域(250M)などのしきい値電圧にセンシティブなデバイス領域に選択的に適用することができる。  (もっと読む)

(もっと読む)

液晶表示装置の作製方法

【課題】性能の優れた液晶表示装置の作成方法を提供することを課題とする。

【解決手段】ガラス基板上にゲイト電極を形成し、ゲイト電極上にゲイト絶縁膜を形成し、ゲイト絶縁膜上に微結晶の半導体膜を形成し、半導体膜上にマスクを形成し、マスクを用いて、半導体膜の選択された部分に不純物を導入し、マスクを残したまま光を照射する液晶表示装置の作製方法であって、光はガラス基板の少なくとも上方から照射されることを特徴とする。

(もっと読む)

シリコン・オン・インシュレータ装置におけるソースおよびドレイン形成

シリコン・オン・インシュレータ装置は、埋設した絶縁層(12)上にシリコン層(10)を有する。ニッケル層を、ゲート(16)上に、ゲート(16)側面における側壁スペーサ(22)上に、また、ゲート(16)両側方でシリコン層(10)上のキャビティに、堆積する。ドープしたアモルファスシリコン層により、キャビティを充填する。つぎに、アニール処理を行って、側壁スペーサ(22)およびゲート(16)上にポリシリコン(40)を形成するが、ニッケルが単結晶シリコン(10)に隣接している箇所では、NiSi層(44)が、背後にドープした単結晶シリコン(42)の表面に移行し、ソース、ドレイン、ならびにソース接点およびドレイン接点を1ステップで形成する。  (もっと読む)

(もっと読む)

多層に応力が加えられたゲート電極を有するfinFET構造体

【課題】 性能が強化されたfinFET構造体、及び、finFET構造体を製造する方法を提供すること。

【解決手段】 半導体構造体及びその製造方法が、基板の上に配置された半導体フィンを含む。半導体フィンの上にゲート電極が配置される。ゲート電極は、半導体フィンのより近くに配置された第1の領域における第1の応力と、該半導体フィンからより遠くに配置された第2の領域における、第1の応力とは異なる第2の応力とを有する。基板内の台座の上に半導体フィンを位置合わせすることもできる。半導体デバイス性能を強化するために、半導体構造体が、望ましい応力条件下でアニールされる。

(もっと読む)

1 - 20 / 28

[ Back to top ]