Fターム[5F110QQ08]の内容

Fターム[5F110QQ08]に分類される特許

81 - 100 / 698

半導体装置の作製方法

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成する。

(もっと読む)

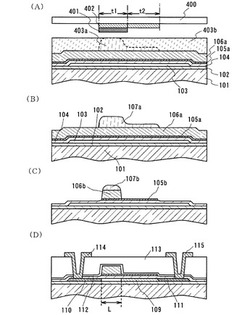

半導体装置および半導体装置の作製方法

【課題】半導体装置の作製工程において、フォトリソグラフィ工程数を削減する。

【解決手段】トランジスタの、ゲート電極となる導電膜、ゲート絶縁膜となる絶縁膜、チャネル領域が形成される半導体膜およびチャネル保護膜となる絶縁膜を連続で形成し、多階調マスクであるフォトマスクによって露光し現像したレジストマスクを用いて、(1)レジストマスクのない領域において、チャネル保護膜となる絶縁膜、チャネル領域が形成される半導体膜、ゲート絶縁膜となる絶縁膜およびゲート電極となる導電膜を連続してエッチングし、(2)レジストマスクをアッシングなどによって後退させ、レジストマスクを残膜厚が小さい領域のみを除去することで、チャネル保護膜となる絶縁膜の一部を露出させ、(3)露出したチャネル保護膜となる絶縁膜の一部をエッチングし、一対の開口部を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

アレイ基板及び液晶表示装置

【課題】製造歩留まりの高いアレイ基板及び液晶表示装置を提供する。

【解決手段】アレイ基板は、複数の補助容量電極と、複数の半導体層15と、複数のゲート電極20を含んだ複数の走査線19と、複数の補助容量線と、複数のコンタクトホールを有した層間絶縁膜と、複数のコンタクトホールを通って複数の半導体層のソース領域に電気的に接続された複数の信号線と、複数の画素電極と、を備えている。走査線19が延在した方向に互いに隣合う一方の画素電極が接続された補助容量電極と、他方の画素電極が接続された補助容量電極とは、走査線を挟んで位置している。薄膜トランジスタのチャネル面積CSは、24μm2以上である。

(もっと読む)

半導体装置

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

半導体装置およびその作製方法

【課題】従来のDRAMは、データを保持するために数十ミリ秒間隔でリフレッシュをしなければならず、消費電力の増大を招いていた。また、頻繁にトランジスタのオン状態とオフ状態が切り換わるのでトランジスタの劣化が問題となっていた。この問題は、メモリ容量が増大し、トランジスタの微細化が進むにつれて顕著なものとなっていた。

【解決手段】酸化物半導体を有するトランジスタを用い、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。ソース電極とドレイン電極との距離を狭くしてもゲート電極用のトレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

薄膜トランジスタの製造方法

【課題】良好なトランジスタ特性を得ることができる印刷用版およびそれを用いたパターン形成方法、および薄膜トランジスタの製造方法を提供すること。

【解決方法】少なくとも、絶縁性の基材と、ゲート電極と、ゲート絶縁層と、ソース電極及びドレイン電極と、前記ソース電極及びドレイン電極と接続するよう形成された半導体層と、前記半導体層を封止する封止層と、を有する薄膜トランジスタの製造方法であって、

表面に凹部と凸部が形成された印刷用版の凹部にインキ供給手段により機能性インキを供給する工程と、前記凹部に供給された機能性インキをブランケット上に転写する工程と、前記ブランケット上の機能性インキを前記基材上又は前記ゲート絶縁層上に転写して前記ゲート電極、ソース電極、ドレイン電極、半導体層のいずれかを形成する工程と、をこの順に行うとしたもの。

(もっと読む)

半導体装置及びその製造方法並びに抵抗器及び半導体素子

【課題】pn接合におけるリーク電流を抑制する。

【解決手段】N−型半導体層10と、シリサイド層20sがその表面に形成されたP−型半導体層20とが、絶縁体9上に形成される。半導体層10にはPMOSトランジスタを、半導体層20にはNMOSトランジスタを、それぞれ形成することができる。半導体層10,20がpn接合J50aを形成する場合、これはシリサイド層20sの端部から近く、結晶欠陥が小さい位置に存在するので、ここにおけるリーク電流は非常に小さい。半導体層10,20が形成するpn接合は、シリサイド層20sの端部から2μm以下の距離にあることが望ましい。

(もっと読む)

半導体装置の製造方法

【課題】低電圧領域として使用されるSOI型MISFETと、高電圧領域として使用されるバルク型MISFETとが共存する半導体装置であっても半導体装置全体を縮小でき、更にプロセスが複雑化することなく作製できる半導体装置と製造方法を提供する。

【解決手段】単結晶半導体基板1、単結晶半導体基板から薄い埋め込み絶縁膜4で分離された薄い単結晶半導体薄膜(SOI層)3を持つSOI基板を用い、SOI型MISFET100およびバルク型MISFET200のウエル拡散層領域6と、ドレイン領域9、11、14、16と、ゲート絶縁膜5と、ゲート電極20とを同一工程にて形成する。バルク型MISFETとSOI型MISFETとを同一基板上に形成できるので、基板の占有面積を縮小できる。SOI型MISFETとバルク型MISFETとの作製工程の共通化により簡易プロセスを実現することができる。

(もっと読む)

微結晶半導体膜及びその作製方法、並びに半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜及びその作製方法を提供する。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】厚さが70nm以上100nm以下の微結晶半導体膜であり、微結晶半導体膜の表面から一部が突出する結晶粒を有し、当該結晶粒は配向面を有し、且つ13nm以上の大きさの結晶子を有する微結晶半導体膜である。また、微結晶半導体膜の膜密度が2.25g/cm3以上2.35g/cm3以下、好ましくは2.30g/cm3以上2.33g/cm3以下である。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製に用いるフォトリソグラフィ工程を従来よりも少なくし、且つ、信頼性の高い半導体装置を提供する。

【解決手段】第1の基板上に酸化物半導体層を有するトランジスタを含む回路と、当該第1の基板とシール材で固定された第2の基板とを有し、当該シール材、当該第1の基板、及び当該第2の基板で囲まれる閉空間は、減圧状態、或いは乾燥空気を充填する半導体装置に関する。当該シール材は、少なくとも前記トランジスタを囲み、閉じられたパターン形状を有する。また当該回路は、酸化物半導体層を有するトランジスタを含む駆動回路である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】オフ電流の極めて小さい半導体装置を提供する。また、該半導体装置を適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上にゲート電極を有し、ゲート電極上にゲート絶縁層を有し、ゲート絶縁層上に酸化物半導体層を有し、酸化物半導体層上にソース電極及びドレイン電極を有し、酸化物半導体層の外縁のうちソース電極の外縁からドレイン電極の外縁に達する部分の長さを、チャネル長の3倍以上、好ましくは5倍以上とする。また、熱処理により、ゲート絶縁層から酸化物半導体層へ酸素を供給する。また、酸化物半導体層を選択的にエッチングした後、絶縁層を成膜する。

(もっと読む)

半導体装置

【課題】表示パネルに設けられるパッド部として適した構造を提供することを目的の一と

する。酸化物半導体の他、絶縁膜及び導電膜を積層して作製される各種用途の表示装置に

おいて、薄膜の剥がれに起因する不良を防止することを目的の一とする。

【解決手段】走査線と信号線が交差し、マトリクス状に配列する画素電極層と、該画素電

極層に対応して設けられた画素部を有し、該画素部に酸素の含有量が異なる少なくとも二

種類の酸化物半導体層とを組み合わせて構成される逆スタガ型薄膜トランジスタが設けら

れた表示装置である。この表示装置において画素部の外側領域には、走査線、信号線を構

成する同じ材質の導電層によって、画素電極層と対向する共通電極層と電気的に接続する

パッド部が設けられている。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において、積層構造の単純化を図り、しかも高品質な表示を可能とする。

【解決手段】電気光学装置は、基板(10)上に、互いに交差するデータ線(6)及び複数の走査線(11)と、データ線に電気的に接続された第1ソースドレイン領域、及び第2ソースドレイン領域を含んでなる半導体層(30a)と、複数の走査線のうち一の走査線に電気的に接続されたゲート電極とを有するトランジスター(30a)と、半導体層と基板との間に配置され、第2ソースドレイン領域に電気的に接続された第1容量電極(71)と、第1容量電極に対向するように設けられるとともに一の走査線に隣り合う走査線に電気的に接続された第2容量電極(73)とを有する蓄積容量(70)と、を備え、蓄積容量は、基板上に設けられた溝の内部の少なくとも一部に設けられている。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置

【課題】SOI−MISFETにおいて、多結晶シリコンの残存による電気的な短絡、ゲート電極の寄生容量の増大を防止する。逆狭チャネル効果の抑制。

【解決手段】シリコン膜13を有するSOI基板上にゲート絶縁膜14、第1の多結晶シリコン膜15、ストッパー窒化膜(16)を順次堆積する。シリコン膜13、第1の多結晶シリコン膜15の側面に逆テーパー面(テーパー角θが鈍角)が形成されるようにエッチングして素子分離溝を形成する。STI埋め込み絶縁膜17を堆積し、CMPにより平坦化した後、等速性のRIEによりストッパー窒化膜(16)と絶縁膜17をエッチングして平坦な表面を得、その上に第2の多結晶シリコン膜18を堆積し(e)、積層多結晶シリコン膜をエッチングして積層ゲート電極(15、18)を形成する(f)。以下、ソース・ドレイン領域21、シリサイド膜22、層間絶縁膜23及びメタル配線24等を形成する(g)。

(もっと読む)

発光装置およびモジュール

【課題】開口部をシンプルにしてシュリンクの問題を解決する。

【解決手段】駆動トランジスタと、スイッチングトランジスタと、消去用トランジスタと、を画素内に有する3トランジスタ型の発光装置の場合において、スイッチング用TFT5505と消去用TFT5506の2つのTFTを、第1のゲート信号線5502と第2のゲート信号線5503の間に配置する。このように配置することで開口率を上げ、開口部もシンプルな形状にすることが出来る。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して、歪みSi層6を挟み、左右にSiGe層5を有する構造からなる第1のエピタキシャル半導体層及び歪みGe層8を挟み、左右にSiGe層7を有する構造からなる第2のエピタキシャル半導体層が島状に絶縁分離されて設けられ、歪みSi層6には概略チャネル領域が形成され、SiGe層5には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成された包囲型ゲート電極構造のNチャネルのMISFETと、歪みGe層8には概略チャネル領域が形成され、SiGe層7には概略高濃度のソースドレイン領域(14、15)が形成された包囲型ゲート電極構造のPチャネルのMISFETとから構成したCMOS。

(もっと読む)

有機発光表示装置及び有機発光表示装置の製造方法

【課題】有機発光表示装置及びその製造方法を提供する。

【解決手段】本発明による有機発光表示装置は、キャパシタ領域を含む基板と、前記基板上に位置するバッファ層と、前記キャパシタ領域の前記バッファ層の上部に位置する半導体層と、前記半導体層の上部に形成されるゲート絶縁膜と、前記キャパシタ領域の前記ゲート絶縁膜の上部に形成される透明電極を含み、断面の前記透明電極の幅は前記半導体層の幅より小さいことを特徴とする。

(もっと読む)

81 - 100 / 698

[ Back to top ]