Fターム[5F110QQ08]の内容

Fターム[5F110QQ08]に分類される特許

101 - 120 / 698

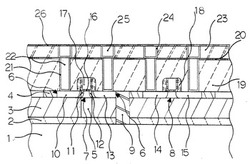

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して貼り合わせられ、島状に絶縁分離されたGe層8(第2の半導体層)が設けられ、このGe層8に高濃度のソースドレイン領域(14、15)が形成されたPチャネルのMISFETと、Si基板1上にシリコン窒化膜2及び一部に空孔5を有するシリコン酸化膜3を介して、空孔5直上の歪みSi層7を挟み、左右にSiGe層6を有する構造からなるエピタキシャル半導体層(第1の半導体層)が島状に絶縁分離されて設けられ、歪みSi層7には概略チャネル領域が形成され、SiGe層6には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成されたNチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジ

スタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁

層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化

物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トラ

ンジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極

層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソ

ース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレ

イン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極やゲート配線及びソース配線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供することを目的とする。

【解決手段】絶縁表面上のゲート電極及びソース配線と、前記ゲート電極及びソース配線上の第1の絶縁層と、前記第1の絶縁膜上の半導体層と、前記半導体膜上の第2の絶縁層と、前記第2の絶縁層上の前記ゲート電極と接続するゲート配線と、前記ソース電極と前記半導体層とを接続する接続電極と、前記半導体層と接続する画素電極とを有することを特徴としている。

(もっと読む)

半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【解決手段】基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層とから形成されていることを特徴としている。このような構成とすることで、フォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる。

(もっと読む)

半導体装置の製造方法

【課題】MOSトランジスタの形成工程を利用して、トレンチアイソレーションを形成できるようにした半導体装置の製造方法を提供する。

【解決手段】シリコン基板1にDTI層20とMOSトランジスタとを有する半導体装置の製造方法であって、シリコン基板1に深いトレンチを形成し、トレンチが形成されたシリコン基板1に熱酸化を施して、PMOSトランジスタ50のゲート酸化膜13を形成すると同時に、トレンチの内側面にSiO2膜14を形成する。次に、トレンチを埋め込むようにシリコン基板1上にポリシリコン膜15を堆積し、このポリシリコン膜15をパターニングする。これにより、PMOSトランジスタ50のゲート電極17を形成すると同時に、トレンチ内にSiO2膜14とポリシリコン膜18とを含むDTI層20を形成する。

(もっと読む)

半導体装置、液晶モジュール、電子機器及び配線

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

半導体装置

【課題】従来に比してオン電圧性能に優れた横型IGBT、および順方向電圧特性に優れた横型FWDを同一基板上に構成可能とする半導体装置を提供する。

【解決手段】半導体基板上において、横型IGBTと、横型FWDとが、絶縁体であるトレンチ絶縁仕切り部を挟むように横方向に隣接配置されて成る半導体装置であって、横型IGBTは、平面視した場合に、エミッタ領域と当該横型IGBTのドリフト領域との境界面の幅がコレクタ領域と当該横型IGBTのドリフト領域との境界面の幅より狭くなるよう形成されており、横型FWDは、平面視した場合に、カソード領域と当該横型FWDのドリフト領域との境界面の幅がアノード領域と当該横型FWDのドリフト領域との境界面の幅より狭くなるよう形成されていることを特徴とする、半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

結晶性半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性半導体の核生成を均一にする。

【解決手段】ガス管から導入された成膜ガスを拡散する第2のガス拡散室と、前記第2のガス拡散室と分散板を隔てて設けられ、該分散板のガス孔から成膜ガスが導入される第1のガス拡散室と、を介して、前記第1のガス拡散室とシャワー板を隔てて設けられた処理室内に該シャワー板のガス孔から成膜ガスを供給し、前記成膜ガスを導入することによって前記処理室内の圧力を2000Pa以上100000Pa以下とし、前記処理室内に電界を生じさせる一対の電極のうち、一方の電極面から電界強度が均一な高周波電力を供給することでグロー放電プラズマを生成させ、前記対向する電極の他方に配された基板上に結晶核を生じさせ、その後、該結晶核を成長させて結晶性半導体膜を作製する。

(もっと読む)

半導体装置およびその製造方法

【課題】溝型の素子間分離部により囲まれた活性領域に形成される電界効果トランジスタにおいて、所望する動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部SIOを、溝型素子分離膜6L,6Sと、溝型素子分離膜6L,6Sの上面に形成されたシリコン膜またはシリコン酸化膜からなる厚さ10〜20nmの拡散防止膜20と、拡散防止膜20の上面に形成された厚さ0.5〜2nmのシリコン酸化膜21L,21Sとから構成し、拡散防止膜20の組成をSiOx(0≦x<2)とし、溝型素子分離膜6L,6Sおよびシリコン酸化膜21L,21Sの組成をSiO2とする。

(もっと読む)

半導体装置

【課題】本願発明で開示する発明は、従来と比較して、さらに結晶成長に要する熱処理時間を短縮してプロセス簡略化を図る。

【解決手段】

一つの活性層204を挟んで二つの触媒元素導入領域201、202を配置して結晶化を行い、触媒元素導入領域201からの結晶成長と、触媒元素導入領域202からの結晶成長とがぶつかる境界部205をソース領域またはドレイン領域となる領域204bに形成する。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造コストの削減が可能であるとともに、安定したトランジスタ特性を得ることが可能な薄膜トランジスタ回路基板及びその製造方法を提供する。

【解決手段】絶縁基板上に酸化物半導体薄膜を形成し、前記酸化物半導体薄膜の上にゲート絶縁層を形成し、前記ゲート絶縁層の上にゲート層を形成し、前記ゲート層の上にレジストパターンを形成し、前記レジストパターンをマスクとして、前記ゲート絶縁層及び前記ゲート層を一括してパターニングして、ゲート絶縁膜上にゲート電極を形成するとともに、ソース領域及びドレイン領域となる前記酸化物半導体薄膜を露出させ、露出させた前記酸化物半導体薄膜を、少なくともシラン(SiH4)を含むガスに晒し、前記シランを含むガスに晒した後に連続して層間絶縁膜を形成する、ことを特徴とする薄膜トランジスタ回路基板の製造方法。

(もっと読む)

液晶パネル、TFTアレイ基板及びその製造方法

【課題】液晶パネル、TFTアレイ基板及びその製造方法を提供する。

【解決手段】本発明は、液晶パネル、TFTアレイ基板及びその製造方法に関する。ベース基板と、前記ベース基板上に形成されたゲート走査線と、データ走査線と、前記ゲート走査線および前記データ走査線を上から覆う保護層とを備えるTFTアレイ基板であって、前記保護層における封止剤を塗布した領域の、ゲート走査線と/またはデータ走査線に対応する位置に、導電層が設けられる。前記導電層は、当該TFTアレイ基板における封止剤の外部領域に延びるとともに、接地端に接続される。前記導電層を形成する材料としては、透明導電材料を有する。

(もっと読む)

ディスプレイ装置及びその製造方法

【課題】構造及び製造工程を簡素化しながら、開口率を向上させた、ディスプレイ装置及びその製造方法を提供する。

【解決手段】本発明の実施形態に係るディスプレイ装置101は、基板111、前記基板111上に形成された前記第1透明導電膜1301及び前記第1透明導電膜1301上に形成された第1金属膜1302を含む多重膜構造と前記第1透明導電膜1301で形成された単一膜構造とを含むゲート配線、前記ゲート配線の一部の領域上に形成された半導体層153、そして前記半導体層上に形成された第2透明導電膜1701及び前記第2透明導電膜1701上に形成された第2金属膜1702を含む多重膜構造と前記第2透明導電膜1701で形成された単一膜構造とを含むデータ配線を含む。

(もっと読む)

発光装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にp型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

EL表示装置及びその作製方法

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

発光表示装置及び発光表示装置の作製方法

【課題】薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製する方法を提供する。

【解決手段】剥離層を介して基板上に素子領域を形成する際に、半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行う。更に素子領域を基板から剥離して、じん性の高い第1の支持体に設け、第1の支持体及びじん性の高い第2の支持体で液晶素子を挟持することで、薄く、軽量であり且つ破壊が生じにくい発光表示装置を、作製工程を大幅に削減して低コストで作製できる。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

101 - 120 / 698

[ Back to top ]