Fターム[5F110QQ08]の内容

Fターム[5F110QQ08]に分類される特許

61 - 80 / 698

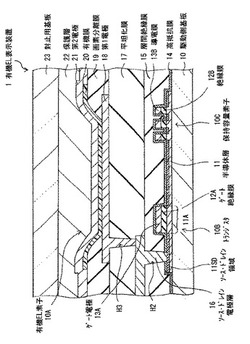

表示装置および電子機器

【課題】画質劣化を抑制することが可能な表示装置および電子機器を提供する。

【解決手段】有機EL表示装置1は、駆動側基板10上に、有機EL素子10Aと、トランジスタ10Bと、映像信号に対応する電荷を保持する保持容量素子10Cとを備えたものである。保持容量素子10Cは、酸化物半導体よりなる半導体層11上に絶縁膜12Bを介して導電膜13Bを有し、かつ半導体層11上の選択的な領域に、導電膜13Bおよび絶縁膜12Bのうちの少なくとも一部が除去されてなる凹部を有している。保持容量素子10Cでは、そのような凹部を通じて、半導体層11の酸化物半導体から酸素が離脱し易くなり、これにより、印加電圧に依存する容量変動が抑制される。

(もっと読む)

微結晶半導体膜、及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜の作製方法を提供することを課題とする。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、種結晶上に、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を形成し、第2の微結晶半導体膜上に、第2の微結晶半導体膜に含まれる混相粒の隙間を埋めつつ、結晶成長を促す第4の条件で、第3の微結晶半導体膜を積層形成する。

(もっと読む)

薄膜トランジスタアレイ、表示装置、およびそれらの製造方法

【課題】本発明は、開口率を大きくする必要がなく、印刷に適し、複数画素を用いずに面積階調できる薄膜トランジスタアレイ、表示装置、および薄膜トランジスタアレイの製造方法を提供する。

【解決手段】画素の有効領域の幅をA、画素の有効領域のネガパターンの幅をBとしたとき、幅Bが幅Aよりも大きな薄膜トランジスタとする。あるいは、対向電極と画素電極の距離をCとしたとき、距離Cが幅Bの4分の1以上B以下である表示装置とする。

(もっと読む)

シリコン・オン・インシュレータ内に形成された金属酸化膜半導体デバイス

【課題】デバイスの破壊電圧を大きく低下させずにLDMOSデバイスのオン抵抗を減少可能にすること。

【解決手段】半導体デバイスが、第1導電型の基板、基板の少なくとも一部分上に形成された絶縁層、および絶縁層の少なくとも一部分上に形成された第2導電型のエピタキシャル層を備える。第1、第2導電型のソース/ドレイン領域が、エピタキシャル層内でその上面に近接して形成され、第1、第2ソース/ドレイン領域は互いに横に間隔を置いて設置される。ゲートは、エピタキシャル層の上でその上面に近接して、少なくとも部分的に第1および第2ソース/ドレイン領域の間に形成される。このデバイスはさらに、エピタキシャル層と、絶縁層を貫通して形成され、基板、第1ソース/ドレイン領域、およびエピタキシャル層と直接に電気的に接続するように構成された第1のソース/ドレイン接点と、エピタキシャル層を貫通して形成され、第2ソース/ドレイン領域に直接に電気的に接続できるように構成された第2ソース/ドレイン接点とを備える。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

回路基板の製造方法

【課題】絶縁膜に形成されるヴィアホールの直径を縮小化することが可能で、高密度化に寄与することのできる回路基板の製造方法を提供する。

【解決手段】本発明の回路基板の製造方法は、基板10上に第1導電体を形成する第1導電体形成工程と、第1導電体を被覆する様にゲート絶縁膜21を成膜する第1絶縁膜成膜工程と、第1導電体上のゲート絶縁膜21に貫通孔32を開口して、当該貫通孔32を介して第1導電体の表面および基板の表面を部分的に露出させる貫通孔形成工程と、貫通孔32内に露出する第1導電体の表面を撥液化させる撥液化工程と、貫通孔32内に露出する第1導電体以外の領域に第2絶縁膜を形成する第2絶縁膜形成工程と、を含むことを特徴とする。

(もっと読む)

表示装置、表示装置の製造方法および電子機器

【課題】低コストかつ簡易なプロセスで製造することが可能な表示装置およびその製造方法を提供する。

【解決手段】表示装置1は、酸化物半導体よりなる半導体層12上の選択的な領域(チャネル領域12A)に、ゲート絶縁膜13を介してゲート電極14が設けられ、そのチャネル領域12Aに隣接する領域(ソース・ドレイン接続領域12B)にソース・ドレイン電極層16が電気的に接続される。半導体層12では、これらのチャネル領域12Aおよびソース・ドレイン接続領域12Bとは異なる領域(画素電極部12C)がアノードとして利用される。製造プロセスにおいて、フォトマスク、フォトレジストなどの使用部材を減らし、工程数を削減することができる。

(もっと読む)

薄膜トランジスタ及びその製造方法並びに画像表示装置

【課題】薄膜トランジスタにおいて、ゲート絶縁膜に直接ストライプ状に凹部を形成することで隔壁形成プロセスを省き、前記凹部をガイドとして塗布法により精度よく半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタの構造を提供する。また、その構造を用いた薄膜トランジスタの製造方法、及びそれを用いたが画像表示装置を提供すること。

【解決手段】基板と、前記基板上に形成されたゲート電極と、前記基板上及び前記ゲート電極上のゲート絶縁体層と、前記ゲート絶縁体層に形成された凹部と、前記絶縁体層の凹部内に形成される半導体層と、前記半導体層上の中央部に設けられる保護膜と、前記半導体層の両端部で接続されるソース電極とドレイン電極と、を有する薄膜トランジスタにおいて、前記ゲート絶縁体層の凹部がストライプ状に形成されていることを特徴とする薄膜トランジスタとする。

(もっと読む)

表示装置およびその製造方法

【課題】TFTの特性劣化を抑制しつつクロス容量を低下することが可能な表示装置およびその製造方法を提供する。

【解決手段】基板11上にゲート電極12および第1配線層21を形成したのち、全面にゲート絶縁膜13を形成する。次に、ゲート絶縁膜13上に半導体層14Aを形成したのち、半導体層14A上に第1保護膜15を形成する。第1配線層に対向する領域の半導体層14および第1保護膜15の除去およびその他の領域をエッチングにより加工する。次いで、全面に第2保護膜23を形成および加工したのち、ソース・ドレイン電極17および第2配線層24を形成する。これにより、チャネル層14表面の損傷が防止されると共に、配線部20のクロス容量が低減される。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

半導体記憶装置およびその作製方法

【課題】半導体記憶装置におけるデータ保持のためのリフレッシュ動作の回数を低減し、消費電力の小さい半導体記憶装置を提供する。また、三次元の形状を適用することで、集積度を高めても短チャネル効果の影響が低減され、かつ従来に比べてフォトリソグラフィ工程数の増加を抑えた半導体記憶装置を提供する。

【解決手段】溝部の設けられた絶縁膜103と、溝部を挟んで離間した一対の電極116と、溝部の側面および底面と接し、溝部の深さよりも厚さの薄い、一対の電極116と接する酸化物半導体膜106と、酸化物半導体膜106を覆うゲート絶縁膜112と、ゲート絶縁膜112を介して酸化物半導体膜106と重畳して設けられたゲート電極112と、を有するトランジスタ150と、キャパシタ160と、を有する半導体記憶装置である。

(もっと読む)

薄膜トランジスタアレー基板、薄膜集積回路装置及びそれらの製造方法

【課題】TFT特性が良好で表示品質や回路配線の層間絶縁性を確保できるTFTアレー基板の製造方法等を提供する。

【解決手段】基材1上への酸化物半導体膜3のパターン形成工程、酸化物半導体膜へのソース電極接続領域3s及びドレイン電極接続領域3dの形成工程、酸化物半導体膜を覆うゲート絶縁膜4の形成工程、ゲート絶縁膜にコンタクトホールを開けてソース電極6s及びドレイン電極6dをソース電極接続領域及びドレイン電極接続領域に接続するとともに酸化物半導体膜上にゲート絶縁膜を介してゲート電極7を形成し、第1回路配線群17を形成する工程、ソース電極、ドレイン電極、ゲート電極及び第1回路配線群上に層間絶縁膜18を形成する工程、層間絶縁膜上に第2回路配線群19を形成する工程を有し、ゲート絶縁膜4の厚さを100nm〜500nmの範囲とし、層間絶縁膜18の厚さを1μm以上且つゲート絶縁膜4の2倍〜10倍の厚さとする。

(もっと読む)

液晶表示装置

【課題】横電界方式で液晶層を駆動する液晶表示装置において、その画像表示性能を向上させる。

【解決手段】画素領域のそれぞれには、ドレイン信号線DLに接続された薄膜トランジスタTFTと、複数のスリットを有し且つ透明導電膜で形成される第1の電極と、前記薄膜トランジスタと前記第1の電極を接続する接続領域を有し、透明導電膜で形成される平面状の第2の電極を有し、前記第2の電極は、前記第1の電極と前記第1の基板間に形成され、且つ、前記第1の電極とゲート信号線GLに重畳し、さらに、隣接する前記画素領域の第2の電極と接続されていることを特徴とする液晶表示装置である。

(もっと読む)

薄膜半導体装置

【課題】工程を複雑にすることなく、多結晶シリコン膜に回路特性に適した複数の異なる

ゲート絶縁膜厚を有する薄膜トランジスタ(TFT)を同一基板に形成することができる

薄膜半導体装置とその製造方法を提供。

【解決手段】ガラス基板上に形成した多結晶シリコン膜に駆動電圧が異なるTFTを混載

する際に、低電圧駆動TFTではチャネル領域の不純物をアクセプタがより多くなるよう

にしあるいはドナーがより少なくなるようにし、高電圧駆動TFTではチャネル領域の不

純物をドナーがより多くなるようにしあるいはアクセプタがより少なくなるようにする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】薄膜領域TA1中に第1の素子領域、第2の素子領域および第1の分離領域を有し、厚膜領域TA2中に第3の素子領域、第4の素子領域および第2の分離領域を有する半導体装置を次のように製造する。(a)絶縁層1bを介してシリコン層1cが形成された基板を準備する工程と、(b)基板の第1の分離領域および第2の分離領域のシリコン層中に素子分離絶縁膜3を形成する工程と、を有するよう製造する。さらに、(c)薄膜領域TA1にハードマスクを形成する工程と、(d)ハードマスクから露出した、第3の素子領域および第4の素子領域のシリコン層上に、それぞれシリコン膜7を形成する工程と、(e)第3の素子領域および第4の素子領域のシリコン膜7間に、素子分離絶縁膜11を形成する工程と、を有するよう製造する。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、容易に素子分離もできる半導体装置を提供する。

【解決手段】第1絶縁膜2の上の第1導電型の第1半導体層3の表面を含む上部に設けられた第2導電型の第1半導体領域7と、第1半導体領域7の上部に設けられた第1導電型の第2半導体領域8と、側面が第1半導体層3と第1半導体領域7と第2半導体領域8に接する第1トレンチ4と、第1トレンチ4の側面に沿って設けられたゲート絶縁膜5と、第1トレンチ4内に埋め込まれたゲート電極6と、第1半導体領域7と第1トレンチ4から離れて第1半導体層3の上部に設けられた第1導電型の第3半導体領域9と、側面が第3半導体領域9に接し第3半導体領域9に対して第1半導体領域7の反対側に配置された第2トレンチ15と、第2トレンチ15の側面に沿って設けられた素子分離絶縁膜10と、第2トレンチ15内に埋め込まれたポリシリコン埋め込み領域11とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置の小型化を実現する。

【解決手段】 第1の絶縁膜上に、島状の半導体層及び前記半導体層を囲む第2の絶縁膜を形成し、前記半導体層の上面と平面的に重なるようにして導電膜からなる抵抗素子(例えばポリシリコン抵抗素子)を配置する。

(もっと読む)

表示装置及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を

同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電

極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気

的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成

された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを

介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成

された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的

に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体装置の作製方法

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成する。

(もっと読む)

61 - 80 / 698

[ Back to top ]