Fターム[5F110QQ08]の内容

Fターム[5F110QQ08]に分類される特許

21 - 40 / 698

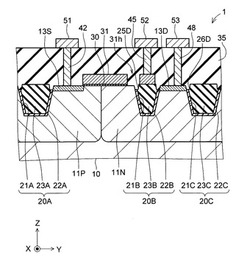

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

液晶パネル用基板、液晶パネル、電子機器及び投射型表示装置

【課題】半導体を基板とする液晶パネルは、ウェル領域があるため、漏れ光がトランジスタ部分のみでなくそこから離れた半導体基板を通過しただけで光リーク電流が流れることがある。この光リーク電流が、ガラス基板上にスイッチング素子としてのTFTを配置した液晶パネルに比べて多くなるという欠点がある。

【解決手段】反射電極となる画素電極(14)と、画素電極への電圧印加を制御するスイッチング素子とを有する画素単位が基板上にマトリックス状に配置されてなる液晶パネル用基板において、両素電極とスイッチング素子の端子電極を構成する導電層(6a)との間に、両者を接続するためのコンタクトホールを形成し、このコンタクトホールの形成箇所を囲む開口を有し、隣接する複数の画素電極の間の領域には開口を有さない遮光層を、画素電極と導電層との間に設けることにより、画素電極どうしの隙間から漏込む光による弊害を防ぐ。

(もっと読む)

半導体装置

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な

容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜

上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、

前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、

容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

表示装置

【課題】熱処理による特性変動を抑制した酸化物半導体を用いた表示装置を提供する。

【解決手段】実施形態によれば、絶縁層と、絶縁層上のゲート電極と、ゲート電極上にゲート絶縁膜を介して設けられ酸化物層より形成された半導体層と、半導体層の上において、ゲート電極を挟むように離間して設けられたソース電極及びドレイン電極と、を含む薄膜トランジスタと、ソース電極及びドレイン電極のいずれかに接続され、前記酸化物層より形成され前記半導体層よりも電気抵抗が低い画素電極と、画素電極に与えられる電気信号によって光学特性の変化と発光との少なくともいずれかを生ずる光学素子と、画素電極の下に設けられゲート絶縁膜と同じ材料で形成された膜と、を備え、ゲート電極の上のゲート絶縁膜の半導体層の側の表面は、画素電極の下に設けられた膜の画素電極の側の表面よりも平滑性が高い表示装置が提供される。

(もっと読む)

半導体装置

【課題】新規な不揮発性のラッチ回路及びそれを用いた半導体装置を提供する。

【解決手段】第1の素子の出力は第2の素子の入力に電気的に接続され、第2の素子の出

力は第2のトランジスタを介して第1の素子の入力に電気的に接続されるループ構造を有

するラッチ回路であって、チャネル形成領域を構成する半導体材料として酸化物半導体を

用いたトランジスタをスイッチング素子として用い、またこのトランジスタのソース電極

又はドレイン電極に電気的に接続された容量を有することで、ラッチ回路のデータを保持

することができる。これにより不揮発性のラッチ回路を構成することができる。

(もっと読む)

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

液晶表示装置

【課題】オフリーク電流を抑制することが可能な液晶表示装置を提供する。

【解決手段】本発明の液晶表示装置では、半導体層53は、平面視においてゲート電極51の範囲内に配置される。ソース電極55及びドレイン電極57は、平面視において半導体層53の範囲内に配置される。シールド7は、保護絶縁膜4上に配置され、画素電極6と同一の材料からなり、画素電極6と電気的に接続されていない。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複

数種の薄膜トランジスタを備えたアクティブマトリクス型液晶表示装置を提供することを

課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる

酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャ

ネル保護型を用い、かつ、画素用薄膜トランジスタの主要な部分を透光性材料で構成する

ことにより、開口率を上げる。

(もっと読む)

半導体装置

【課題】不揮発性を有し、書き込み回数に制限のない新たな構造の半導体装置を提供する。

【解決手段】複数の記憶素子が直列に接続され、複数の記憶素子の一は、第1〜第3のゲート電極、第1〜第3のソース電極、および第1〜第3のドレイン電極を有する第1〜第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含んで構成され、第1のゲート電極と、第2のソース電極または第2のドレイン電極の一方とは、電気的に接続され、第1の配線と、第1のソース電極と、第3のソース電極とは、電気的に接続され、第2の配線と、第1のドレイン電極と、第3のドレイン電極とは、電気的に接続され、第3の配線と、第2のソース電極または第2のドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のゲート電極とは、電気的に接続され、第5の配線と、第3のゲート電極とは電気的に接続された半導体装置。

(もっと読む)

電気装置の製造方法、半導体基板の製造方法、電気装置用形成基板、及び電子機器

【課題】静電破壊を防止して歩留まり良く製造できる電気装置の製造方法、半導体基板の製造方法、電気装置用形成基板、及び電子機器を提供する。

【解決手段】支持体上に、樹脂材料からなる基材を複数積層することで第1基板を形成する工程と、素子基板から前記支持体を剥離する工程と、素子基板との間で機能素子を挟持するように第2基板を貼り付ける工程と、を有する電気装置の製造方法に関する。素子基板の形成工程においては、複数の基材間のいずれかに挟持するように電極層を配置するとともに、電極層よりも上層であって複数の前記基材間のいずれかに挟持する或いは基板本体の表面に配置するように機能素子を駆動するための半導体素子を設ける。

(もっと読む)

半導体装置

【課題】SRAMメモリセルを有する半導体装置において、その特性の向上を図る。

【解決手段】SRAMを構成するドライバトランジスタ(Dr1)が配置される活性領域(Ac)の下部に、絶縁層(BOX)を介して、素子分離領域(STI)により囲まれたn型のバックゲート領域(nBG)を設け、ドライバトランジスタ(Dr1)のゲート電極(G)と接続する。また、n型のバックゲート領域(nBG)の下部に配置され、少なくともその一部が、素子分離領域(STI)より深い位置に延在するp型ウエル領域(Pwell)を設け、接地電位(VSS)に固定する。かかる構成によれば、トランジスタの閾値電位(Vth)をトランジスタがオン状態の時には高く、逆に、オフ状態の時には低くなるように制御し、また、p型ウエル領域(Pwell)とn型のバックゲート領域(nBG)との間のPN接合も順バイアスさせないよう制御することができる。

(もっと読む)

薄膜トランジスタアレイ基板、有機発光表示装置、及び薄膜トランジスタアレイ基板の製造方法

【課題】薄膜トランジスタアレイ基板、有機発光表示装置、及び薄膜トランジスタアレイ基板の製造方法を提供する。

【解決手段】基板10上に配置され、活性層212、ゲート電極214、ソース電極218a、ドレイン電極218b、活性層とゲート電極との間に配置された第1絶縁層13、及びゲート電極とソース電極及びドレイン電極との間に配置された第2絶縁層15を含む薄膜トランジスタと、第1絶縁層及び第2絶縁層上に配置され、ソース電極及びドレイン電極のうち一つと連結される画素電極117と、ゲート電極と同一層で形成された下部電極314及び画素電極と同一材料を含む上部電極317を含むキャパシタと、第2絶縁層と画素電極との間及び下部電極と上部電極との間に直接配置された第3絶縁層116と、ソース電極、ドレイン電極及び上部電極を覆って画素電極を露出させる第4絶縁層19と、を含む薄膜トランジスタアレイ基板。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインが、第1半導体結晶層を構成する原子とニッケル原子との化合物、第1半導体結晶層を構成する原子とコバルト原子との化合物または第1半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、第2半導体結晶層を構成する原子とニッケル原子との化合物、第2半導体結晶層を構成する原子とコバルト原子との化合物、または、第2半導体結晶層を構成する原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

アクティブマトリクス基板及び液晶表示装置

【課題】 アクティブマトリクス基板の特性の向上、及び、白黒表示間のコントラストが向上した液晶表示装置を提供する。

【解決手段】 マトリクス状に配置された画素電極と、行方向に隣接する2つの画素電極の両方と重畳して配置された列方向に伸びるソース配線と、ソース配線と交差して配置された行方向に伸びる保持容量配線とを備えるアクティブマトリクス基板であって、上記画素電極、ソース配線及び保持容量配線は、絶縁膜を介してそれぞれ異なる層に形成されており、上記ソース配線は、行方向に隣接する2つの画素電極下にそれぞれ屈曲点を有し、かつ、行方向に隣接する2つの画素電極の間隙を横切る横断部を有し、上記保持容量配線は、行方向に隣接する2つの画素電極の間隙と重畳して配置された列方向に伸びる延伸部を有し、上記ソース配線は、実質的に保持容量配線との交差点でのみ保持容量配線と重畳しているアクティブマトリクス基板。

(もっと読む)

薄膜トランジスタ、これを備えた表示装置、およびその製造方法

【課題】薄膜トランジスタ、これを備えた表示装置、およびその製造方法に関する。

【解決手段】本発明に係る薄膜トランジスタは、基板上に形成され、金属触媒の作用による結晶の成長によって結晶化したアクティブ層と、アクティブ層の一部領域上に形成されたゲート絶縁膜パターンと、ゲート絶縁膜パターンの一部領域上に形成されたゲート電極と、ゲート絶縁膜パターン上にゲート絶縁膜パターンと同じパターンで形成され、ゲート電極を覆うエッチング防止膜パターンと、アクティブ層およびエッチング防止膜パターン上に形成されたソース電極およびドレイン電極と、アクティブ層およびエッチング防止膜パターンとソース電極およびドレイン電極の間にソース電極およびドレイン電極と同じパターンで形成され、アクティブ層の結晶化に用いられた金属触媒を除去するゲッタリング層パターンとを含む。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】本発明は、低温かつ簡便で安価な製造工程により作製可能であり、トランジスタ特性に優れる、ダブルゲート構造を有する薄膜トランジスタおよびその製造方法を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成された第1ゲート電極と、上記第1ゲート電極を覆うように形成された第1ゲート絶縁層と、上記第1ゲート絶縁層上に形成され、低抵抗領域であるソースコンタクト領域およびドレインコンタクト領域ならびに高抵抗領域であるチャネル領域を有する酸化物半導体層と、上記ソースコンタクト領域に接して形成されたソース電極と、上記ドレインコンタクト領域に接して形成されたドレイン電極と、上記酸化物半導体層上に形成され、絶縁性有機材料を含む第2ゲート絶縁層と、上記第2ゲート絶縁層上に形成された第2ゲート電極とを有することを特徴とする薄膜トランジスタを提供する。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

記憶装置及び信号処理回路

【課題】電源の供給を停止しても、記憶している論理状態が消えない記憶装置を提供する。また、該記憶装置を用いることで、電源供給停止により消費電力を抑えることができる信号処理回路を提供する。

【解決手段】第1乃至第4のノードを有する論理回路と、第1のノード、第2のノード、及び第3のノードと接続された第1の制御回路と、第1のノード、第2のノード、及び第4のノードと接続された第2の制御回路と、第1のノード、第1の制御回路、及び第2の制御回路に接続された第1の記憶回路と、第2のノード、第1の制御回路、及び第2の制御回路に接続された第2の記憶回路と、を有する記憶装置である。

(もっと読む)

21 - 40 / 698

[ Back to top ]