Fターム[5F110QQ08]の内容

Fターム[5F110QQ08]に分類される特許

161 - 180 / 698

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の長時間にわたる保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと、第2のトランジスタと、を含む複数のメモリセルと、増幅回路と、スイッチ素子と、を含む読み出し回路と、リフレッシュ制御回路と、を有し、第1のチャネル形成領域と第2のチャネル形成領域は、異なる材料を主成分として構成され、第1のゲート電極と、第2のソース電極および第2のドレイン電極の一方は電気的に接続され、第2のソース電極および第2のドレイン電極の他方と、増幅回路の入力端子の一は電気的に接続され、増幅回路の出力端子は、スイッチ素子を介して第2のソース電極および第2のドレイン電極の他方と接続され、スイッチ素子の導通状態または非導通状態は、リフレッシュ制御回路によって制御される半導体装置である。

(もっと読む)

対向電極を有する小型電界効果トランジスタおよび製造方法

【課題】小型化の増進を可能にするとともに、実現が容易な、対向電極を備えた電界効果トランジスタの製造方法を提供する。

【解決手段】ゲート電極9ソースコンタクト12,ドレインコンタクト13、および対向電極コンタクトの輪郭描写パターンを含むエッチングマスクが、セミコンダクタ・オン・インシュレータ型の基板上に形成される。基板は、誘電体5の層およびゲート材料により覆われる。対向電極コンタクトは、ゲート電極9のパターン内に配置される。ゲート材料は、ゲート電極9、ソースコンタクト12およびドレインコンタクト13、ならびに対向電極コンタクトを画定するためにエッチングされる。支持基板2の一部分は、対向電極コンタクト領域のパターンの中を通って解放される。導電性材料22が支持基板2の自由部分上に堆積されて、対向電極コンタクトを形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

表示装置及びプロジェクター

【課題】液晶の配向不良を抑制するために画素電極を平坦化し、開口率を下げずに十分な容量を得られる容量素子を有する半導体装置を実現することを課題とする。

【解決手段】薄膜トランジスタ上の遮光膜、前記遮光膜上の容量絶縁膜、前記容量絶縁膜上に導電層、前記導電層と電気的に接続するように画素電極を有する半導体装置であり、前記遮光膜、前記容量絶縁膜および前記導電層から保持容量素子を形成することにより、容量素子として機能する領域の面積を増やすことができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化することを目的の一とする。

【解決手段】酸化物半導体膜を有するボトムゲート構造のトランジスタの作製工程において、熱処理による脱水化または脱水素化処理、及び酸素ドープ処理を行う。酸素ドープ処理されたゲート絶縁膜、熱処理による脱水化または脱水素化処理された酸化物半導体膜を有するトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減できており、信頼性の高いトランジスタとすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

結晶化半導体薄膜の製造方法および結晶化半導体薄膜

【課題】アモルファス薄膜の溶融結晶化時に生じる凹凸の影響を受けないようなトップゲート型TFT素子などの作製が可能な結晶化半導体薄膜の製造方法および該凹凸が表面にない結晶化半導体薄膜を提供する。

【解決手段】本発明の結晶化半導体薄膜の製造方法は、第1基板1上層に剥離層2を介して剥離可能に形成したアモルファス半導体薄膜4aを溶融結晶化させ、その後、結晶化した結晶化半導体薄膜4pの表面側を接合面にして接着剤6を介して第2基板5上層に前記結晶化半導体薄膜4pを接合するとともに該結晶化半導体薄膜4pを第1基板側1から剥離する。本発明の結晶化半導体薄膜は、基板上層に設けられた結晶化半導体薄膜であって、該結晶化半導体薄膜は、前記基板上層に接合層を介して接合されており、かつ該接合層に対する接合面側に溶融結晶化に伴う凹凸形状を有する。

(もっと読む)

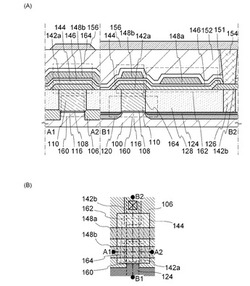

半導体装置及びその製造方法

【課題】低いチャネル抵抗を具現し、電界効果移動度が高くなる効果がある二重ゲートトランジスタを含む半導体装置及びその製造方法を提供する。

【解決手段】本発明による半導体装置は、下部ゲート電極と、前記下部ゲート電極上の上部ゲート電極と、前記下部ゲート電極と前記上部ゲート電極の間に介在され、前記下部ゲート電極と前記上部ゲート電極を連結するコンタクトプラグと、前記上部ゲート電極と同一の高さに前記上部ゲート電極から離隔して形成された機能電極と、を含む。本発明によれば、電界効果移動度が高い二重ゲートトランジスタを半導体装置に適用させることによって、半導体装置の特性を改善することができる。特に、本発明によれば、別途のマスク工程や蒸着工程を追加する必要がないので、工程コストの上昇や収率減少をもたらすことなく、大面積・高画質の半導体装置を大量生産することができる。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】酸化物半導体層を有するトランジスタにおいて、ゲート絶縁層を酸化ガリウム膜として、酸化物半導体層と接する構成とする。また、酸化物半導体層の上下を挟むように酸化ガリウム膜を配置することによって信頼性の向上を実現する。また、ゲート絶縁層は、酸化ガリウム膜と酸化ハフニウム膜の積層構造としてもよい。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置の作製方法及び電気光学装置

【課題】TFTに適したSOI基板およびその作製方法を提供する。またSOI基板を用

いて信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】SIMOX、ELTRAN、Smart−Cutに代表される技術を用いて

SOI基板を作製するにあたって、主表面(結晶面)が{110}面である単結晶半導体

基板を用いる。その様なSOI基板は下地となる埋め込み絶縁層と単結晶シリコン層との

密着性が高く、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

電気光学装置用基板の製造方法、電気光学装置用基板、電気光学装置及び電子機器

【課題】例えば電極パッドと薄膜素子との間に剥離層を介して静電結合が生じることを低減する。

【解決手段】電気光学装置用基板の製造方法は、転写元基板(10)に形成した薄膜素子(310)を転写先基板(70)に転写することにより電気光学装置用基板を製造する製造方法であって、転写元基板上に設けられた剥離層(11)上に絶縁膜(5)を介して薄膜素子を形成する工程と、転写元基板上における薄膜素子よりも上層側に電極パッド(500)を形成する工程と、転写元基板上の積層構造における絶縁膜と電極パッドとの間に、転写元基板上で平面的に見て電極パッドに少なくとも部分的に重なるように、遮蔽電極(710)を形成する工程とを含む。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミスを防ぐことが可能である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。また、新たな構造の半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させることを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワイドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、半導体装置の各メモリセルを構成する、酸化物半導体を用いたトランジスタを直列に接続することにより、隣り合うメモリセルにおいて、酸化物半導体を用いたトランジスタのソース電極またはドレイン電極をお互いに接続させることができ、メモリセルの占有面積を低減することができる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】容易に製造することができ、かつ信頼性の高い薄膜トランジスタおよびその製造方法を提供する。

【解決手段】薄膜トランジスタの製造方法は、基板上にゲート電極、ゲート絶縁膜および活性層し、活性層上に第1の保護層となるGa酸化物膜を形成する。Ga酸化物膜上に第2の保護層となる感光性有機系絶縁膜を形成し、感光性有機系絶縁膜においてチャネル領域に整合する部分をパターン部とし、それ以外の部分を非パターン部とする。この非パターン部を除去し、この非パターン部の除去とともにパターン部をマスクとして非パターン部下のGa酸化物膜を除去して、第1の保護層および第2の保護層を形成しチャネル保護膜を得る。チャネル保護膜を覆うようにソース電極およびドレイン電極となる膜を形成し、この膜上にレジストパターンを形成し、チャネル保護膜をエッチングストッパとして膜をエッチングし、ソース電極およびドレイン電極を形成する。

(もっと読む)

アクティブマトリクス型駆動基板、その製造方法及び表示装置

【課題】電子ペーパー等の表示装置に適用した場合に、その消費電力を小さくでき、歩留まりを向上させることができるアクティブマトリクス型駆動基板及びその製造方法等を提供する。

【解決手段】第1絶縁膜2を表面に有する導電基材1上に設けられた薄膜トランジスタ10及び保持容量20と、薄膜トランジスタ10及び保持容量20を第2絶縁膜16,17を介して覆う画素電極30を有し、保持容量20が第1電極21と誘電体膜22と薄膜トランジスタ10のソース・ドレイン電極14,15に接続する第2電極23との積層体であるアクティブマトリクス型駆動基板50であって、導電基材1と第1電極21とが第1絶縁膜2の開口部4で接続されているように構成する。第2絶縁膜(16,17)が少なくとも層間絶縁膜17を有し、導電基材1が金属基材であり、第1絶縁膜2が金属基材1の表面粗さを低減する平坦化膜であることが好ましい。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供することを課題の一とする。また、信頼性の高い半導体装置の作製方法を提供することを課題の一とする。また、消費電力が低い半導体装置を提供することを課題の一とする。また、消費電力が低い半導体装置の作製方法を提供することを課題の一とする。また、量産性の高い半導体装置を提供することを課題の一とする。また、量産性の高い半導体装置の作製方法を提供することを課題の一とする。

【解決手段】酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すれば良い。具体的には、酸化物半導体層にハロゲン元素を添加した後に加熱処理を施し、不純物を除去して使用すれば良い。ハロゲン元素としては、フッ素が好ましい。

(もっと読む)

161 - 180 / 698

[ Back to top ]