Fターム[5F110QQ08]の内容

Fターム[5F110QQ08]に分類される特許

121 - 140 / 698

液晶表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】島状半導体層を形成するためのフォトリソグラフィ工程及びエッチング工程を省略し、ゲート電極(同一層で形成される配線等を含む)を形成する工程、ソース電極及びドレイン電極(同一層で形成される配線等含む)を形成する工程、コンタクトホールを形成する(コンタクトホール以外の絶縁層等の除去を含む)工程、画素電極(同一層で形成される配線等を含む)を形成する工程の4つのフォトリソグラフィ工程で液晶表示装置を作製する。コンタクトホールを形成する工程において、半導体層が除去された溝部を形成することで、寄生チャネルの形成を防ぐ。

(もっと読む)

半導体装置の作製方法及び液晶表示装置の作製方法

【課題】作製工程を増やすことなく、凹凸形状の画素電極を作製することを目的とする。

【解決手段】凸部は、フォトマスクを用いて作製すると再現性の高いものが得られるため、画素TFT1203の作製工程にしたがって作製すればよい。画素TFT1203の作製と同様に積層される半導体層、ゲート絶縁膜および導電膜を積層して凸部を形成する。こうして形成された凸部および同一工程で形成された画素TFT、駆動回路に含まれるTFTを覆うように層間絶縁膜を形成する。凹凸を有する層間絶縁膜が形成されたら、その上に画素電極を形成する。画素電極の表面も絶縁膜の凹凸の影響を受け表面が凹凸化する。

(もっと読む)

薄膜トランジスタ、表示装置、及び液晶表示装置

【課題】正孔電子対と、ソース電極(ドレイン電極)付近に発生する強電界とがともに抑制されることにより、リーク電流が抑制される薄膜トランジスタ、及びそれを備える表示装置又は液晶表示装置の提供。

【解決手段】光源から光が照射されるゲート電極膜と、前記ゲート電極膜の、前記光源側との反対側に、絶縁膜を介して形成される半導体膜と、前記半導体膜に電気的に接続して形成される第1及び第2の電極膜と、前記ゲート電極膜と同一層に形成されるとともに、前記ゲート電極膜と電気的に遮断される第1の遮光膜と、を備える薄膜トランジスタであって、前記第1の遮光膜は、前記半導体膜の一部と前記光の照射方向から見て重なり合うとともに、前記第1の電極膜の少なくとも一部と、前記光の照射方向から見て重なり合う、ことを特徴とする。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタを備える画像表示装置、薄膜トランジスタの製造方法、画像表示装置の製造方法

【課題】作製コストを低減させることが可能な、薄膜トランジスタ、薄膜トランジスタを備える画像表示装置、薄膜トランジスタ及び画像表示装置の製造方法を提供すること。

【解決手段】第一基板と、当該第一基板上に設けられたゲート電極と、前記第一基板及び前記ゲート電極上に設けられたゲート絶縁膜と、当該ゲート絶縁膜上に設けられた半導体層と、当該半導体層上に設けられた保護膜と、前記半導体層及び前記保護膜上に設けられたソース電極及びドレイン電極と、を備え、前記保護膜は、前記半導体層を設けた後に連続して設けられていることを特徴とする薄膜トランジスタとしたもの。

(もっと読む)

半導体装置及びその駆動方法

【課題】半導体装置における電界の集中を緩和する。

【解決手段】ゲート電極とドレイン電極を重畳させずに設け、且つ上面において、ゲート電極とドレイン電極の間には電界制御電極が設けられている。そして、ゲート電極と半導体層の間、及び電界制御電極と半導体層の間には、それぞれ絶縁層が設けられており、電界制御電極と半導体層の間に設けられた絶縁層は、ゲート電極と半導体層の間に設けられた絶縁層よりも厚い。さらには、この半導体装置を駆動させるに際して、電界制御電極の電位は、ソース電位以上であってゲート電位より低ければよく、例えば、電界制御電極とソース電位を接続させることでこのような構成を実現することができる。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】 製造工程を単純化すると同時に、良好な画質を確保できる薄膜トランジスタ表示板を提供することである。また、本発明の他の目的は、画素の開口率を向上することができる薄膜トランジスタ表示板を提供することである。

【解決手段】 本発明の実施形態による薄膜トランジスタ表示板は、基板上に形成されているゲート線と、ゲート線上に形成されているゲート絶縁膜と、ゲート絶縁膜上に形成されている第1半導体と、少なくとも一部分の第1半導体上に形成されているデータ線及びドレイン電極と、ゲート絶縁膜上に形成されている蓄積導電体と、データ線、ドレイン電極及び蓄積導電体上に形成されている第1保護膜と、第1保護膜上に形成され、蓄積導電体上に位置した開口部を有する第2保護膜と、第2保護膜上に形成され、ドレイン電極に接続され、開口部で蓄積導電体と重なる画素電極とを備えることを特徴とする薄膜トランジスタ表示板。

(もっと読む)

微結晶半導体膜の作製方法、及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、生産性高く作製する。

【解決手段】第1の条件により、高い結晶性の混相粒を低い粒密度で有する種結晶を絶縁膜上に形成した後、第2の条件により混相粒を成長させて混相粒の隙間を埋めるように、種結晶上に第1の微結晶半導体膜を形成し、第1の微結晶半導体膜上に、第1の微結晶半導体膜に含まれる混相粒の隙間を広げず、且つ結晶性の高い微結晶半導体膜を成膜する第3の条件で第2の微結晶半導体膜を積層形成する。

(もっと読む)

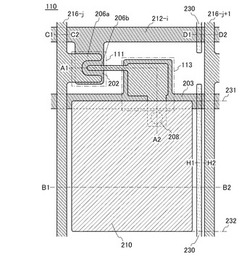

液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】半導体層205のエッチングと、画素電極210とドレイン電極206bを接続するためのコンタクトホール208の形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】複数の基準電位を要する半導体装置、及び半導体装置の駆動において、より消費電力を軽減する。

【解決手段】電源線に直列に接続された複数の抵抗素子により、電源線に供給された電位を抵抗分割し、電源線と電気的に接続するスイッチトランジスタを介して所望の分割された電位を出力する電位分割回路を有する半導体装置であり、スイッチトランジスタのドレイン端子は出力側の回路に設けられたトランジスタのゲート端子(又は容量素子の一方の端子)と電気的に接続しノードを構成する。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法及び発光装置

【課題】薄膜トランジスタのオン電流の安定を図ること。

【解決手段】ELパネル1の駆動トランジスタ6において、ソース電極6iとゲート電極6aおよびドレイン電極6hとゲート電極6aの間にバックゲート効果を発現させないように、ソース電極6iとドレイン電極6hをゲート電極6aから離間させることに十分な膜厚(例えば、2000Å以上4000Å以下の膜厚)を有する保護絶縁膜6dを形成することによって、駆動トランジスタ6のチャネルが乱されることを低減して、オン電流を安定させるようにした。

(もっと読む)

アクティブマトリクス型有機EL表示装置およびその駆動方法

【課題】アクティブマトリクス型有機EL表示装置の表示領域にある薄膜トランジスタの信頼性を高めることにある。

【解決手段】

アクティブマトリクス型有機EL表示装置は、マトリクス状に配置された複数の画素を有する表示領域と、駆動回路を有する周辺領域と、を備える。さらに、アクティブマトリクス型有機EL表示装置の前記画素は、ボトムゲート型の第1トランジスタと、カソード電極と、アノード電極と、カソード電極およびアノード電極の間に設けられた有機EL層と、を有し、前記駆動回路は、ボトムゲート型の第2トランジスタと前記第2トランジスタ上に設けられたバックゲート電極とを有する。前記画素が最低輝度を表示する際に、前記第1トランジスタのゲート電位は前記カソード電極の電位よりも低い。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、基板10と第1絶縁膜11の間に駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、第2絶縁膜12とパッシベーション膜14の間にスイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜6e(5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

回路基板の製造方法

【課題】印刷法にて、回路基板に容易にヴィアホールを開口できる回路基板の製造方法を提供する事。

【解決手段】基板上に第一導電体を形成する第一導電体形成工程を行い、次に第一導電体を被覆する様に第一絶縁膜を成膜する第一絶縁膜成膜工程を行い、次に第一導電体上の第一絶縁膜に貫通孔32を開口して、第一導電体の表面を露出させる貫通孔形成工程を行い、次に第一導電体の表面を撥液化させる撥液化工程を行い、次に貫通孔32以外の領域に前駆体樹脂を印刷し、印刷後に前駆体樹脂を硬化して第二絶縁膜を形成する第二絶縁膜形成工程を行う。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変化しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変動しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

トランジスタ構造体、トランジスタ構造体の製造方法及び発光装置

【課題】トランジスタ特性が変化しにくい薄膜トランジスタを容易に作り分けること。

【解決手段】ボトムゲート構造の第1薄膜トランジスタである駆動トランジスタ6と、トップゲート構造の第2薄膜トランジスタであるスイッチトランジスタ5とを形成する際、駆動トランジスタ6の第1ゲート電極6aとスイッチトランジスタ5の第2遮光膜5eを形成する工程と、スイッチトランジスタ5の第2ゲート電極5aと駆動トランジスタ6の第1遮光膜6eを形成する工程を別工程にし、それ以外の薄膜トランジスタの構成を共通の工程によって形成する。こうして、ゲート電極(6a、5a)と遮光膜(6e、5e)を形成する以外の工程を共通の製造工程とする製造方法によって、駆動トランジスタ6とスイッチトランジスタ5を作り分けることを可能にした。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISデバイスにおいて、pチャネル型電界効果トランジスタの動作特性を劣化させることなく、ひずみシリコン技術を用いたnチャネル型電界トランジスタの動作特性を向上させる。

【解決手段】所望する濃度プロファイルおよび抵抗を有するnMISのソース/ドレイン(n型拡張領域8およびn型拡散領域13)およびpMISのソース/ドレイン(p型拡張領域7およびp型拡散領域11)を形成した後、所望するひずみ量を有するSi:C層16をn型拡散領域13に形成することにより、nMISのソース/ドレインにおいて最適な寄生抵抗と最適なSi:C層16のひずみ量とを得る。また、Si:C層16を形成する際の熱処理を1m秒以下の短時間で行うことにより、すでに形成されているp型拡張領域7およびp型拡散領域11のp型不純物の濃度プロファイルの変化を抑える。

(もっと読む)

薄膜帯電センサー

【課題】帯電体の接触または非接触動きを感知する薄膜帯電センサーを提供する。

【解決手段】基板と、基板上に備えられ、ゲート層、アクティブ層及びソース層/ドレイン層を備える薄膜トランジスタユニットと、ゲート層と電気的に連結された導電材料で形成された第1膜を備えるものであって、帯電体の電場に反応して入力電流を生成する薄膜アンテナユニットと、を備える薄膜帯電センサーである。これにより、簡単な薄膜層の積層過程を通じて容易に製造され、帯電体の電場を利用するため、接触状態だけでなく、非接触状態でも動きを感知できる。

(もっと読む)

121 - 140 / 698

[ Back to top ]