Fターム[5F110QQ17]の内容

Fターム[5F110QQ17]に分類される特許

101 - 120 / 694

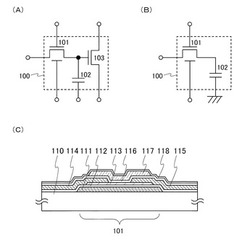

記憶装置、半導体装置

【課題】長い期間においてデータの保持が可能な記憶装置を提供する。

【解決手段】記憶素子と、上記記憶素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタとを有する。上記トランジスタは、通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられており、また、活性層に酸化物半導体を含むためにオフ電流が極めて低い。上記記憶装置では、絶縁膜に囲まれたフローティングゲートに高電圧で電荷を注入するのではなく、オフ電流の極めて低いトランジスタを介して記憶素子の電荷量を制御することで、データの記憶を行う。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

半導体装置

【課題】裏面に対する各種プロセスを必要としない簡素な構造の半導体装置を提供する。

【解決手段】活性層2に対して埋込絶縁膜4との境界部分にn+型埋込領域6が形成されているSOI基板5を用いて、素子領域8と配線引出部9との間にトレンチ分離部11を配置し、トレンチ分離部11をn-型ドリフト層7と同じもしくはそれより深く、かつ、埋込絶縁膜4から離間するように形成する。このような構成とすれば、SOI基板5に対して予め形成しておけるn+型埋込領域6を介して行うことができる。このため、高耐圧MOSFET1の素子領域8と配線引出部9との電気的な接続を裏面電極などを備える必要がなく、裏面に対する各種プロセスを必要としない簡素な構造の半導体装置により、層間絶縁膜18に大きな電位差が掛かることを抑制できる。また、電位分布が不均一になることを防止でき、高耐圧MOSFET1の耐圧低下を抑制することも可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】交流電圧で使用することができる半導体装置を提供する。

【解決手段】半導体基板11に形成された第1トランジスタT1と、半導体基板11上にBOX層12を介して形成された第2トランジスタT2と、を備え、第1トランジスタT1は、半導体基板11の表面に形成された第1ボディ領域11fと、この第1ボディ領域11fを挟むように形成された第1ソース領域11d及び第1ドレイン領域11eと、有し、第1ボディ領域11f上に第2トランジスタT2の第2ドレイン領域13cが配置され、第1ドレイン領域11e上に第2トランジスタT2の第2ボディ領域13aが配置され、第1ドレイン領域11eとBOX層12における第2ボディ領域13aとの間に接続層17が形成され、かつ第2ドレイン領域13cが第1トランジスタT1のゲート電極を兼ねた。

(もっと読む)

半導体装置

【課題】高集積化を図り、単位面積あたりの記憶容量を増加させた新たな構造の半導体装置を提供することを目的の一とする。高集積化に伴い増加する回路素子数の低減が可能で、かつ、素子数低減による電力削減が可能な、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】ビット線と、m(mは3以上の自然数)本のワード線と、ソース線と、m本の信号線と、第1乃至mのメモリセルと、駆動回路と、を有する半導体装置において、メモリセルは、第1のトランジスタ、容量素子に蓄積された電荷を保持する第2のトランジスタを含み、第2のトランジスタは酸化物半導体層で形成されるチャネルを有する。上記構成において、駆動回路は、第j(jは3以上の自然数)の信号線に出力される信号を用いて第(j−1)の信号線に出力される信号を生成する。

(もっと読む)

半導体基板の作製方法

【課題】加速した水素イオンの照射量を増やすことなく、低い加熱処理温度で単結晶半導体基板からベース基板に半導体層を転載できるSOI基板の作製方法を提供することを課題の一とする。

【解決手段】劈開に寄与することなく、脆化領域から半導体基板の表面側に拡散する水素に着眼した。そして、脆化領域からの水素の拡散を防ぎ、且つ脆化領域と半導体基板の表面に挟まれた領域に水素を供給できるキャップ膜を半導体基板に形成し、当該半導体基板からベース基板に半導体層を転載する発明に至った。特に、半導体基板に形成するキャップ膜の水素濃度は水素イオンの照射量以上とすればよい。

(もっと読む)

酸化物半導体薄膜およびその製造方法、並びに薄膜トランジスタ、薄膜トランジスタを備えた装置

【課題】生産性、組成均一性を向上させることができ、かつ低温アニール時に低抵抗化が起こらず、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した酸化物半導体薄膜を得る。

【解決手段】In、GaおよびOを主たる構成元素とする酸化物半導体薄膜であって、In,Gaの組成比が3/4≦Ga/(In+Ga)≦9/10であり、かつ、抵抗率が1Ωcm以上、1×106Ωcm以下を満たすものとする。

(もっと読む)

酸化物半導体薄膜、薄膜トランジスタおよび薄膜トランジスタを備えた装置

【課題】IGZO系酸化物半導体薄膜において、膜中水分量を低減可能な組成を明らかにし、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適した酸化物半導体薄膜を得る。

【解決手段】In、Ga、ZnおよびOを主たる構成元素とする酸化物半導体薄膜において、In,Ga,Znの組成比をZn/(In+Ga+Zn)≦1/3、Ga/(In+Ga+Zn)≦9/11、4/5≦Ga/(In+Ga)≦1、且つIn/(In+Zn)≦1/2を満たすものとする。

(もっと読む)

酸化物半導体薄膜の製造方法および該製造方法により作製された酸化物半導体薄膜、薄膜トランジスタ、並びに薄膜トランジスタを備えた装置

【課題】低温アニールによる低抵抗化が起こらず、再現性が高く、大面積デバイス、特にフレキシブルデバイス作製に適したIGZO系酸化物薄膜を製造する。

【解決手段】In,Ga,Zn,Oを主たる構成元素とし、組成比が11/20≦Ga/(In+Ga+Zn)≦9/10、且つ3/4≦Ga/(In+Ga)≦1、且つZn/(In+Ga+Zn)≦1/3を満たす酸化物半導体薄膜を成膜する成膜工程と、成膜された酸化物半導体薄膜に対して、酸化性雰囲気中で100℃以上、300℃以下の熱処理を施す熱処理工程とを含み、熱処理工程後の酸化物半導体薄膜の抵抗率が1Ωcm以上、1×106Ωcm以下となるように、成膜工程における成膜条件および熱処理工程における熱処理条件を設定する。

(もっと読む)

SOI基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体層のテーパー形状を有する端部の特性を良好にすることを課題とする。

【解決手段】加速されたイオンを単結晶半導体基板に照射することによって、単結晶半導体基板中に脆化領域を形成し、単結晶半導体基板とベース基板とを、絶縁膜を介して貼り合わせ、脆化領域において単結晶半導体基板を分離して、ベース基板上に絶縁膜を介して第1の単結晶半導体層を形成し、第1の単結晶半導体層に対してドライエッチングを行って、端部の形状がテーパー形状である第2の単結晶半導体層を形成し、第2の単結晶半導体層の端部に対して、ベース基板側の電位を接地電位としたエッチングを行う。

(もっと読む)

半導体装置およびその製造方法

【課題】集積性に優れた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1と、半導体基板1上に設けられた埋め込み絶縁膜2と、埋め込み絶縁膜2上に設けられた第1の薄膜FET100と、第1の薄膜FET100と隣接して埋め込み絶縁膜2上に形成された第2の薄膜FET101と、第1の薄膜FET100直下の半導体基板1内に設けられた第1ウェル領域4と、第2の薄膜FET101直下の半導体基板1内に設けられた第2ウェル領域5と、を備え、第1ウェル領域4から第2ウェル領域5までの距離が、第1の薄膜FET100から第2の薄膜FET101までの距離よりも大きい。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】メモリセルアレイを構成する複数のメモリセルが、複数行ごとに複数のブロックに分割され、共通ビット線は、各ブロックにおいて、選択トランジスタを介して分割ビット線と電気的に接続されており、メモリセルの一は、第1のチャネル形成領域を含む第1のトランジスタと、第2のチャネル形成領域を含む第2のトランジスタと、容量素子と、を有し、ソース線は、第1のソース電極と接続され、分割ビット線は、第1のドレイン電極および第2のソース電極と接続され、ワード線は、容量素子の電極の一方と接続され、信号線は、第2のゲート電極と接続され、第1のゲート電極と、第2のドレイン電極と、容量素子の電極の他方とが接続される半導体装置を提供する。

(もっと読む)

半導体装置の製造方法

【課題】第2絶縁膜からセルフアラインに所定の距離だけ離して半導体素子を形成可能で、第2絶縁膜と単結晶層との界面の上部でのリーク電流の発生の低減が可能な半導体装置の製造方法を提供する。

【解決手段】SOI基板の単結晶層の上方に形成した第1絶縁膜をストッパに単結晶層と第1耐酸化膜をエッチングして第1絶縁膜の上に単結晶柱5aを形成し、第1耐酸化膜を単結晶柱5aの上に配置したまま単結晶柱5aを一部熱酸化し単結晶柱5aの側面を囲むように閉ループパターンで形成され第1耐酸化膜の外周部の直下にせり出し部10aを有する第2絶縁膜10を形成し、第1耐酸化膜を除去して単結晶柱5aの上面を露出させ、単結晶柱5aの上面に半導体素子を形成する。第2絶縁膜10を形成したことにより、せり出し部10aの下の単結晶柱5aの上面は、側面の近くになるにつれ徐々にその上面の高さが低くなり側面につながる傾斜面になっている。

(もっと読む)

固体撮像装置、半導体表示装置

【課題】撮像された画像の品質を向上させる固体撮像装置、或いは半導体表示装置を提供する。

【解決手段】グローバルシャッタ方式で駆動を行うことで、電荷の蓄積動作を制御するための電位を全画素で共有することができる。さらに、出力信号が与えられる一の配線に接続されている複数のフォトセンサを第1のフォトセンサ群とし、出力信号が与えられる他の配線に接続されている複数のフォトセンサを第2のフォトセンサ群とすると、電荷の蓄積動作を制御するための電位または信号を第1のフォトセンサ群に与える配線と、上記電位または信号を第2のフォトセンサ群に与える配線とを、接続する。

(もっと読む)

配線基板、半導体装置、及びそれらの作製方法

【課題】集積化が進む配線基板、又は半導体装置において、導通不良を軽減する。信頼性の高い配線基板、又は半導体装置を歩留まり良く作製する。

【解決手段】多層配線構造を有する配線基板、又は半導体装置において、該配線に用いる導電層の接続構造に曲面を有する導電層を用いる。周囲の絶縁層の除去によって露出された下層の導電層の先端部は曲面であり、下層の導電層上に積層する上層の導電層の被覆性を良好とすることができる。曲面な表面を有するレジストマスクを用いて導電層をエッチング加工することによって曲面な表面を有する導電層を形成する。

(もっと読む)

半導体基板、電界効果トランジスタ、集積回路、及び半導体基板の製造方法

【課題】絶縁膜を介在させて基板同士を貼り合わせることで、一方の基板上に形成された半導体層を他方の基板に形成できると共に、この際に当該半導体層の結晶構造を損傷させることなく、高品質な結晶構造を維持したまま簡単に製造できる半導体基板、電界効果トランジスタ、集積回路、及び半導体基板の製造方法を提案する。

【解決手段】MISFET1では、InP基板12上のIII-V族化合物半導体層7に、ALD法を用いて表面が平坦な酸化膜6を形成するようにしたことで、当該酸化膜6とSi基板2とを常温において貼り合わせるだけで、これら酸化膜6とSi基板2とを強固に接合でき、かくして一方のInP基板12上に形成されたIII-V族化合物半導体層7を他方のSi基板2に形成できると共に、III-V族化合物半導体層7の結晶構造を損傷させることなく高品質に維持したまま簡単に製造できる。

(もっと読む)

半導体基板、ナノワイヤトランジスタ及びその製造方法

【課題】従来よりも電気的信頼性を向上できる半導体基板、ナノワイヤトランジスタ及びその製造方法を提案する。

【解決手段】シリコン層5と埋め込み酸化膜3との間にシリコン窒化膜4を形成することにより、熱酸化の際に、耐酸化性膜によりシリコン基板表面6にまで酸素が到達することを妨げることで、シリコン基板表面6に酸化シリコンが形成され難くなり、その分だけ当該酸化シリコンの体積膨張を抑制して、チャネル層形成時のストレスを制御できることで、当該ストレスによるナノワイヤ13の意図しない変形又は当該変形によるナノワイヤ13の断線を防止でき、かくして、従来よりも電気的な信頼性及び特性の低下を防止できる。

(もっと読む)

半導体基板の作製方法、及び半導体装置の作製方法

【課題】絶縁表面に欠陥の少ない単結晶半導体膜を有する半導体基板の、簡便な作製方法を提供することを課題の一つとする。また、歩留まりの良い半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】単結晶半導体基板の表面に絶縁層を形成し、絶縁層をエッチングしながら、絶縁層を介して単結晶半導体基板にイオン照射を行うことで、脆化領域を形成し、単結晶半導体基板の表面に接合層を形成し、単結晶半導体基板と、支持基板とを、接合層を介して貼り合わせ、熱処理を行うことにより、脆化領域内に劈開面を形成して、単結晶半導体基板の一部を分離する、半導体基板の作製方法を提供する。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを各々含む複数のメモリセルをマトリクス状に配置し、メモリセルの一と他のメモリセルとを接続する配線(ビット線とも呼ぶ)と、第1のトランジスタにおけるソース領域またはドレイン領域と、が、導電層および第2のトランジスタにおけるソース電極またはドレイン電極を介して電気的に接続した構成とした半導体装置を提供する。これにより、第1のトランジスタにおけるソース電極またはドレイン電極と、第2のトランジスタにおけるソース電極またはドレイン電極と、をそれぞれ異なる配線に接続する場合と比較して配線の数を削減することができるため、半導体装置の集積度を向上させることができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第1のトランジスタのゲート電極と、該ゲート電極に接する第2のトランジスタのソース電極とは、エッチングの選択比がとれる材料を用いて形成される半導体装置を提供する。第1のトランジスタのゲート電極と、第2のトランジスタのソース電極とをエッチングの選択比がとれる材料を用いて形成することで、レイアウトのマージンを低減させることができるため半導体装置の集積度を向上させることができる。

(もっと読む)

101 - 120 / 694

[ Back to top ]