Fターム[5F110QQ17]の内容

Fターム[5F110QQ17]に分類される特許

121 - 140 / 694

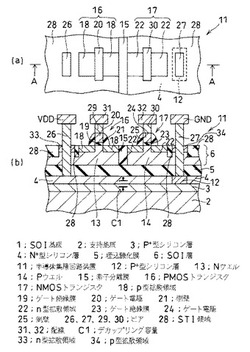

半導体装置

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体素子、及び半導体装置

【課題】半導体素子の微細化に伴うゲート電極サイズの微細化においても、ゲート電極とチャネル形成領域間のリーク電流が抑制された半導体素子を提供することを課題の一とする。また、小型かつ高性能な半導体装置を提供することを課題の一とする

【解決手段】チャネル形成領域として機能する半導体層上に、ゲート絶縁膜として比誘電率が10以上の酸化ガリウムを含む絶縁膜を形成し、前記酸化ガリウム上にゲート電極が形成された構造を有する半導体素子を作製することにより、課題の一を解決する。また、前記半導体素子を用いて半導体装置を作製することにより、課題の一を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】基板1Cは、半導体基板2と絶縁層3と半導体層4とが積層されたSOI領域1Aと、半導体基板2で構成されたバルク領域1Bとを有しており、SOI領域1Aの半導体層4に形成されたMISFETは、チャネル領域に不純物が導入されておらず、バルク領域1Bの半導体基板2に形成されたMISFETは、チャネル領域に不純物が導入されている。SOI領域1AのMISFETを形成する際には、MISFETのチャネル領域に不純物が導入されないようにし、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とは行なわない。バルク領域1BのMISFETを形成する際には、ウエル領域形成用のイオン注入とチャネルドープイオン注入とハローイオン注入とを行う。

(もっと読む)

半導体装置

【課題】貫通電流を低減させることができる相補型の論理回路を用いることで、消費電力を抑えることができる半導体装置の提案を目的の一とする。或いは、貫通電流を低減させることができる相補型の論理回路を用いることで、発熱を抑えることができる半導体装置の提案を目的の一とする。

【解決手段】通常のゲート電極の他に、閾値電圧を制御するための第2のゲート電極が備えられたnチャネル型トランジスタ、或いはpチャネル型トランジスタを、相補型の論理回路に用いる。そして、オフ電流が極めて小さい絶縁ゲート電界効果型トランジスタをスイッチング素子として用い、上記第2のゲート電極の電位を制御する。上記スイッチング素子として機能するトランジスタは、シリコン半導体よりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体材料を、チャネル形成領域に含む。

(もっと読む)

半導体基板、半導体装置、および半導体装置の製造方法

【課題】半導体装置の製造工程において、十分にゲッタリング効果を得ることができる半導体基板を提供する。

【解決手段】半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7と、を備えることを特徴とする半導体基板3を提供する。また、半導体からなる基板本体8と、前記基板本体8上に形成されたリンを含有したシリコン酸化膜からなる絶縁層6と、該絶縁層6上に設けられた半導体層7を備える半導体基板3と、前記半導体層7上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記半導体層7内であって、前記ゲート電極に対して自己整合となる位置に設けられた不純物拡散領域と、を有することを特徴とする半導体装置を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離されたSOI基板にIGBTとその制御回路等が形成される半導体装置において、IGBTの高耐圧化及びターンオフ特性の改善等が必要になる。

【解決手段】ダミー半導体基板16にN型エピタキシャル層8を形成し、N型エピタキシャル層8にトレンチ30を形成し、トレンチ30側壁及びN型エピタキシャル層8表面にN型バッファ層7、次にP型埋め込みコレクタ層6を形成し、トレンチ30底面及びP+型埋め込みコレクタ層6上を埋め込み絶縁膜5で被覆する。埋め込み絶縁膜5上をポリシリコン膜3で被覆し、該ポリシリコン膜3と絶縁膜2を介してP型半導体基板1を貼り合わせた後、ダミー半導体基板16を除去し、略同一平面状に露出するトレンチ30底面の埋め込み絶縁膜5、P+型埋め込みコレクタ層6、N型バッファ層7、N型ドリフト層8a等を具備するSOI基板を形成する。該SOI基板にIGBT等を形成する。

(もっと読む)

多層ウェーハ中のトレンチ構造

【課題】バーズビーク効果を軽減することのできる、SOIウェーハ内にトレンチを製造する方法を提供すること。

【解決手段】本発明は、基板と、基板上の酸化物層と、酸化物層上の半導体層とを備える多層ウェーハ内にトレンチ構造を製造する方法に関し、本方法は、半導体層および酸化物層を貫通して基板中へ延在するトレンチを形成するステップと、トレンチの内部表面において、半導体層のいくらかの材料が、トレンチの内部表面に露出した酸化物層の部分の一部の上に少なくとも流れるように、形成されたトレンチのアニール処理を行うステップとを含む。

(もっと読む)

半導体基板の保持用トレイ、並びに半導体基板および半導体装置の作製方法

【課題】複数枚の絶縁層被覆単結晶半導体基板に対して効率よくイオン注入を行い、大面積の単結晶半導体層を備えた半導体基板の作製方法を提供することを課題の一とする。

【解決手段】半導体基板の作製工程において、表面のファンデルワールス力を調整した保持用トレイに表面に絶縁層が形成された複数枚の単結晶半導体基板を貼り合わせ、複数枚の単結晶半導体基板にイオン照射工程を行うことで複数枚の単結晶半導体基板の所定の深さに脆化層を形成し、複数枚の単結晶半導体基板にファンデルワールス力を調整したベース基板を貼り合わせることでファンデルワールス力の差を利用して保持用トレイを選択的に分離し、剥離加熱処理を行い劈開面を形成して単結晶半導体基板をベース基板から分離することにより、絶縁層を介して単結晶半導体基板をベース基板に転載する。

(もっと読む)

半導体薄膜基板および半導体薄膜基板を用いた半導体装置の作製方法

【課題】一層の半導体層から膜厚の異なる半導体層を有する半導体薄膜基板を提供することを目的の一とする。または、半導体薄膜基板を適用した半導体装置を提供することを目的の一とする。

【解決手段】基板上に半導体層を形成し、半導体層を加工して第1の島状半導体層および第2の島状半導体層を形成し、第1の島状半導体層にレーザー照射を行うことにより第1の島状半導体層を溶融させ、第1の島状半導体層から第2の島状半導体層より膜厚が厚い第3の島状半導体層を形成する、半導体薄膜基板の作製方法である。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体装置の作製工程数を減少させること、半導体装置の歩留まりを向上させること、半導体装置の作製コストを低減することを課題とする。

【解決手段】基板上に、単結晶半導体層をチャネル形成領域に有する第1のトランジスタと、当該第1のトランジスタと絶縁層を介して分離され、酸化物半導体層をチャネル形成領域に有する第2のトランジスタと、当該単結晶半導体層及び酸化物半導体層を有するダイオードを有する半導体装置、及び、その作製方法に関する。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

誘電体分離型半導体装置の製造方法

【課題】耐圧を向上させることができ、かつ半導体基板が反るのを防ぐことができる誘電体分離型半導体装置の製造方法を得る。

【解決手段】p型シリコン基板10の主面の領域42に複数のトレンチ溝44を形成する。p型シリコン基板10の表面を酸化して、p型シリコン基板10の主面に誘電体層12を形成し、領域42に厚膜誘電体層38を形成する。p型シリコン基板10に誘電体層12を介してn−型半導体層14を貼り合せる。厚膜誘電体層38の上方においてn−型半導体層14の一部にn+型半導体領域18を形成する。n+型半導体領域18から離間してn+型半導体領域18を取り囲むようにn−型半導体層14の一部にp+型半導体領域20を形成する。n+型半導体領域18に接続された主電極26を形成する。p+型半導体領域20に接続された主電極28を形成する。p型シリコン基板10の裏面に裏面電極32を形成する。

(もっと読む)

SOI基板の作製方法

【課題】半導体層が効率良く平坦化されたSOI基板を提供することを課題の一とする。また、当該SOI基板を用いた半導体装置を提供することを課題の一とする。

【解決手段】ボンド基板に加速されたイオンを照射して該ボンド基板に脆化領域を形成し、ボンド基板またはベース基板の表面に絶縁層を形成し、絶縁層を介してボンド基板とベース基板を貼り合わせ、熱処理により、脆化領域においてボンド基板を分離して、ベース基板上に半導体層を形成し、半導体層の表面と、該半導体層と同じ半導体材料でなる半導体ターゲットとが対向するように配置し、半導体層の表面と半導体ターゲットとに、交互に希ガスイオンを照射することで、半導体層の表面の平坦化を図るSOI基板の作製方法である。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】平坦性の高い表面を有する単結晶半導体層を備えた半導体基板の作製方法を提供することを目的の一とする。平坦性の高い単結晶半導体層を備えた半導体基板を用いて信頼性の高い半導体装置を作製することを目的の一とする。

【解決手段】半導体基板の作製工程において、単結晶半導体基板に希ガスイオン照射工程、レーザー照射工程および水素イオン照射工程を行うことで、単結晶半導体基板の所定の深さに大きな結晶欠陥を含有した薄い脆化領域を形成し、剥離加熱工程を行うことで脆化領域より表面側の単結晶半導体層をベース基板に転載する。

(もっと読む)

半導体基板の作製方法及び半導体装置の作製方法

【課題】単結晶半導体基板に付着する異物の影響を低減し、歩留まりよく半導体基板を作製することを目的の一とする。安定な特性を有する半導体装置を歩留まりよく作製することを目的の一とする。

【解決手段】半導体基板の作製工程において、単結晶半導体基板に脆化領域を形成する際、単結晶半導体基板表面に対して複数の(少なくとも二つ以上の)異なる角度で斜め方向から水素イオンを照射することによって、単結晶半導体基板に付着する異物の影響を低減し、均一な単結晶半導体層を有する半導体基板を歩留まりよく作製することができる。

(もっと読む)

半導体装置の作製方法

【課題】動作性能および信頼性の高い半導体装置の提供を課題とする。

【解決手段】シリコン基板上に設けられた酸化シリコン膜と、単結晶シリコン基板の一部

よりなりTFTの活性層となる単結晶の島状シリコン層となる前の単結晶シリコン基板を

熱酸化して得られ、酸化シリコン膜に貼り合わせ界面にて貼り合わせて設けられた膜厚が

0.05μm〜0.5μmの酸化シリコン膜と、活性層を熱酸化して設けられた他の面の

酸化シリコン膜と、により取り囲まれた活性層と、活性層上に設けられたゲート電極と、

を有し、単結晶の島状シリコン層は、膜厚が0.05μm〜0.5μmの酸化シリコン膜

を介して水素が導入された単結晶シリコン基板を水素が導入された部分で分断して得られ

たものである半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】 本発明の半導体装置は、良好なカットオフ特性と高速動作とを両立して改善できる。

【解決手段】 本発明の半導体装置は、基板と、基板上に形成され、バンドギャップが生成されたグラフェンを有するチャネル領域と、チャネル領域の両側に形成され、チャネル領域のグラフェンに比して小さいバンドギャップが生成されたグラフェンを有するソース/ドレイン領域と、ソース/ドレイン領域のチャネルに接する部分の上に、夫々形成された第1および第2のゲート電極と、を備えることを特徴とする。

(もっと読む)

半導体装置の作製方法及び電気光学装置

【課題】TFTに適したSOI基板およびその作製方法を提供する。またSOI基板を用

いて信頼性の高い半導体装置及びその作製方法を提供する。

【解決手段】SIMOX、ELTRAN、Smart−Cutに代表される技術を用いて

SOI基板を作製するにあたって、主表面(結晶面)が{110}面である単結晶半導体

基板を用いる。その様なSOI基板は下地となる埋め込み絶縁層と単結晶シリコン層との

密着性が高く、信頼性の高い半導体装置を実現することが可能となる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、容量素子は、第2のトランジスタのソース電極またはドレイン電極と、ゲート絶縁層と、第2のトランジスタを覆う絶縁層上に設けられた容量素子用電極を含み、第2のトランジスタのゲート電極と、容量素子用電極とは、絶縁層を介して少なくとも一部が重畳して設けられる半導体装置を提供する。第2のトランジスタのゲート電極と、容量素子用電極とを、異なる層で形成することで、半導体装置の集積度を向上させることができる。

(もっと読む)

電界効果型トランジスタ及びその製造方法並びに画像表示装置

【課題】再現性良く、高収率でフレキシブルデバイスとしての電界効果型トランジスタを作製することができ、下地層そのものに堅牢性を与えることによって後工程による破壊や傷による表面形状の異常が生じない電界効果型トランジスタ及びその製造方法、並びに画像表示装置を提供する。

【解決手段】第1の基板10と、下地第一層21及び下地第二層22と、ゲート電極30と、ゲート絶縁層40と、ソース電極50、ドレイン電極60、及び半導体層70とがこの順で形成された電界効果型トランジスタ1であり、下地第二層22は、下地第一層21に接する面と反対側の面22aの表面粗さRms2が0.3nm以下である。

(もっと読む)

121 - 140 / 694

[ Back to top ]