Fターム[5F140AA22]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 狭チャンネル効果対策 (28)

Fターム[5F140AA22]に分類される特許

1 - 20 / 28

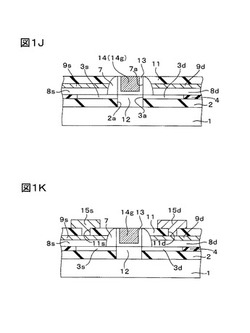

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】素子分離部2で囲まれた活性領域14に位置し、後の工程でコア用nMISのゲートGが形成される領域Ga1のみに、Nch用ゲートスタック構造NGを構成する積層膜を形成し、上記領域Ga1以外の領域NGa1には、Pch用ゲートスタック構造PGを構成する積層膜を形成する。これにより、コア用nMISのゲートGが形成される領域Ga1へ素子分離部2から引き寄せられる酸素原子の供給量を減少させる。

(もっと読む)

半導体装置及びその製造方法

【課題】調整用金属を含む高誘電率膜を有するゲート絶縁膜を備えたMISトランジスタを有する半導体装置において、MISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、MISトランジスタnTrを備えている。MISトランジスタは、半導体基板10における素子分離領域11に囲まれた活性領域10aと、活性領域及び素子分離領域上に形成され、高誘電率膜15aを有するゲート絶縁膜16aと、ゲート絶縁膜上に形成されたゲート電極19aとを備えている。ゲート絶縁膜における素子分離領域上に位置する部分のうち、少なくとも一部分には、窒化領域20x,20yが設けられている。窒化領域20x,20yに含まれる窒素の窒素濃度をn1,n2とし、ゲート絶縁膜における活性領域上に位置する部分に含まれる窒素の窒素濃度をnとしたとき、n1>n、且つ、n2>nの関係式が成り立っている。

(もっと読む)

半導体装置及びその製作方法

【課題】半導体記憶装置に適するトランジスタ構造及びその製作方法の提供。

【解決手段】デュアルチャネルトランジスタ50は、少なくとも、第一方向に沿って伸展する第一STI(シャロートレンチアイソレーション)と第二方向に沿って伸展する第二STIにより分離され、第一STIと第二STIが交差する半導体アイランド22と、第二方向に沿って伸展し、半導体アイランドの表面から内側に向かって凹んだゲートトレンチ26と、第二方向に沿って伸展し、ゲートトレンチ内に設けられたゲート30と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第一ソース/ドレイン領域と、第一ソース/ドレイン領域の間に設けられた第一U字型チャネル領域60と、第二方向に沿って設けられ、半導体アイランドの上面に設けられた第二ソース/ドレイン領域と、第二ソース/ドレイン領域の間に設けられた第二U字型チャネル領域62とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタの閾値電圧が高くなることを防止する。

【解決手段】半導体装置は、第1,第2のMISトランジスタTr1,Tr2を備えている。第1,第2のMISトランジスタは、第1,第2の活性領域10a,10b上に形成され、第1,第2の高誘電率膜13a,13bを有する第1,第2のゲート絶縁膜13A,14Bと、第1,第2のゲート絶縁膜上に形成された第1,第2のゲート電極18A,18Bとを備えている。第1のゲート絶縁膜13Aと第2のゲート絶縁膜14Bとは、第1の素子分離領域11L上において分離されている。第1の素子分離領域11Lを挟んで対向する第1の活性領域10aの一端と第2の活性領域10bの一端との距離をsとし、第1の活性領域10aの一端から第1の素子分離領域11L上に位置する第1のゲート絶縁膜13Aの一端までの突き出し量をd1としたとき、d1<0.5sの関係式が成り立っている。

(もっと読む)

半導体装置及びその製造方法

【課題】不純物の拡散によるナローチャネル効果の発生を抑制することを可能にする半導体装置を提供する。

【解決手段】半導体基体1と、半導体基体1に少なくとも一部が埋め込まれた、素子分離のための絶縁層2と、半導体基体1内に形成された不純物領域を含んで成る能動素子と、絶縁層2と半導体基体1との間に形成された、負の固定電荷を有する膜11とを含んで半導体装置を構成する。

(もっと読む)

最適化されたチャンネル領域を有するMOSトランジスタを具備する半導体素子

【課題】 MOSトランジスタを備える半導体素子を提供する。

【解決手段】 半導体素子は、半導体基板の所定領域に形成されて活性領域を区画する素子分離膜を有する。第1活性領域9a及び第2活性領域9bは(100)面の中心上面9t及び中心上面9tから素子分離膜14に向けて延びる傾斜エッジ面9eを有する。第1活性領域9a及び第2活性領域9bの中心上面9t及び傾斜エッジ面9eは第1半導体パターン15a及び第2半導体パターン15bで覆われる。第1半導体パターン15a及び第2半導体パターン15bは中心上面9tに平行な(100)面の平坦な上面15t及び平坦な上面に実質的に垂直な側壁15sを有する。第1半導体パターン15a及び第2半導体パターン15bの上部を通って側壁に交差する方向に第1ゲートパターン26a及び第2ゲートパターン26bが配置される。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】ナローチャネル特性の劣化を抑制する。

【解決手段】素子分離領域STIは、半導体基板100に形成されたトレンチ104内に設けられており、トレンチ104の側壁上に形成された下地絶縁膜105を有している。素子形成領域100a上にはゲート絶縁膜112が形成されており、ゲート絶縁膜112は高誘電率膜110を有している。高誘電率膜110の第1の部分110aは、素子形成領域100aにおける上面上に形成されており、高誘電率膜110の第2の部分110bは、素子形成領域における上部側面104a上に下地絶縁膜105を介して形成されている。第2の部分110bと下地絶縁膜105との間には、MISトランジスタの閾値電圧を変更する金属を含有する第1のキャップ膜106が設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】相対的に厚いゲート絶縁膜を有するMOSトランジスタと相対的に薄いゲート絶縁膜を有するMOSトランジスタを同時に形成する半導体装置およびその製造方法の提供。

【解決手段】相対的に薄いゲート絶縁膜25を有するMOSトランジスタが形成される領域のフィールド絶縁膜端23を相対的に厚いゲート絶縁膜24で覆うことにより、フィールド絶縁膜下部に形成された反転防止拡散層31から相対的に薄いゲート絶縁膜25を有するMOSトランジスタのチャネル領域33をオフセットさせることによって、フィールド絶縁膜の膜厚ばらつきや相対的に厚い第一のゲート絶縁膜24のエッチングばらつき、および反転防止拡散層によるチャネル端の濃度変動の影響を受けず、MOSトランジスタのチャネル幅を短く設計した際に生じる狭チャネル効果の影響を抑制することが可能となり、素子特性が安定した半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極中に含まれる不純物の拡散を防止することができ、さらに、ゲート絶縁膜の信頼性及びホットキャリア耐性を向上させることができる半導体装置及びその製造方法を得る。

【解決手段】N型シリコン基板1上にゲート酸化膜36およびP+型ゲート電極35を形成する。P+型ゲート電極35の両側にソース/ドレイン領域6を形成する。ゲート酸化膜36およびP+型ゲート電極35中には窒素がドープされ、窒素ドーピング領域30が形成される。

(もっと読む)

半導体装置の製造方法

【課題】トレンチ分離構造を有する半導体装置においてトランジスタのドレイン電流の減少などを防止する。

【解決手段】半導体基板10の主表面に活性領域11を分離するトレンチ埋込材21を備え、この埋込材の表面を、少なくとも半導体基板10に接する部分で半導体基板10の主表面より所定高さ落ち込むように形成する。

(もっと読む)

窪み付きゲート構造を有するメモリデバイス及びその製造方法

【課題】本発明は、IC(integrated circuit)の集積度が向上し、しかもショートチャネル効果を防止することができるMOS半導体デバイスを形成する方法を提供する。

【解決手段】DRAMアクセストランジスタのようなメモリデバイスであって、窪み付きゲート構造を有するメモリデバイスを形成する方法が開示されている。まず、絶縁用のフィールド酸化物領域(21)が半導体基板上に形成され、ついで、窒化シリコン層(18)にパターン形成が行われ、エッチングによりトランジスタトレンチ(22)が得られる。その後にデポジットされたポリシリコンであって、ゲート構造形成のためのポリシリコンを、隣接し隆起した窒化シリコン構造に対して研磨できるようにするため、このトランジスタトレンチに隣接するフィールド酸化物領域に窪みが設けられる。

(もっと読む)

半導体装置及び半導体装置の製造方法。

【課題】半導体装置の特性劣化を抑制し、半導体装置のサイズを縮小する技術の提供。

【解決手段】半導体装置は、半導体領域1A内に設けられる第1及び第2の拡散層2A,2Bと、拡散層2A,2B間に設けられる第3の拡散層2Cと、第1の拡散層2Aの周囲を取り囲んで、半導体領域1A表面のゲート絶縁膜3A上に設けられる第1のゲート電極4Aと、第2の拡散層2Bの周囲を取り囲んで、半導体領域1A表面のゲート絶縁膜上に設けられる第2のゲート電極4Bと、ゲート電極4A,4Bの側面上に設けられる第1及び第2の側壁絶縁膜12A,12Bとを具備し、第1及び第2のゲート電極4A,4Bは、側壁絶縁膜12A,12Bが直接接触する部分を有し、第3の拡散層2Cの周囲は、ゲート電極4A,4Bによって取り囲まれている。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネル領域における歪みを適正に増大させ、キャリア注入速度を向上させて、近時における更なる狭チャネル化にも対応したトランジスタ特性の大幅な向上を可能とする信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極101の側面に、自身は膨張性を有する応力膜からなる第1のサイドウォール111と、第1のサイドウォール111上にこれに比して応力の小さい膜からなる第2のサイドウォール112とが形成されており、半導体層、例えばSiC層104が第2のサイドウォール112により第1のサイドウォール111から離間する。

(もっと読む)

半導体装置およびその製造方法

【課題】逆ナローチャネル効果を抑制でき、トランジスタ特性の劣化を防止できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板中に埋め込まれた素子分離絶縁膜12と、前記半導体基板上に設けられたゲート絶縁膜13と、前記ゲート絶縁膜上に設けられゲート電極14と、前記ゲート電極を挟むように前記半導体基板中に隔離して設けられたソース領域Sまたはドレイン領域Dと、前記ソース領域またはドレイン領域の両端部上をチャネル長方向に沿って覆うように設けられた第1,第2ゲート電極延設部15-1,15-2とを具備し、前記ソース領域またはドレイン領域両端部は、チャネル幅方向に沿って前記素子分離絶縁膜から所定の距離d1,d2をもってオフセットする。

(もっと読む)

自己整合したソース/ドレイン領域を有するフィン型電界効果トランジスタ・デバイスおよびその形成方法

【課題】改良されたフィン電界効果トランジスタ(FinFET)デバイスと、その製造方法とを提供する。

【解決手段】1つの側面において、電界効果トランジスタ・デバイスを製造する方法は次のステップを含む。その上にシリコン層を有する基板が準備される。そのシリコン層においてフィン・リソグラフィー・ハードマスクがパターニングされる。フィン・リソグラフィー・ハードマスクの中央部分の上にダミー・ゲート構造が置かれる。ダミー・ゲート構造の周りにフィラー層が堆積させられる。フィン・リソグラフィー・ハードマスクの中央部分の上を中心として、フィラー層にトレンチを形成するためにダミー・ゲート構造が除去され、それはデバイスのフィン領域をデバイスのソース領域およびドレイン領域から区別する。フィン領域内のフィン・リソグラフィー・ハードマスクは、シリコン層に複数のフィンをエッチングするために使用される。フィンの上にゲート・スタックを形成するためにトレンチはゲート材料で満たされる。デバイスのソース領域およびドレイン領域を形成するためにフィラー層が除去され、ソース領域およびドレイン領域は無傷であってゲート・スタックと自己整合させられている。

(もっと読む)

半導体装置の製造方法

【課題】ソース・ドレインを構成するシリコンゲルマニウムの成膜方法を工夫することで、短チャネル効果の抑制と移動度の向上を両立させることを可能とする。

【解決手段】半導体基板11に絶縁ゲート型FETを形成する半導体装置の製造方法であって、絶縁ゲート型FETのソース・ドレイン19、20は、半導体基板11のソース・ドレインが形成される領域に凹部16を形成した後、シリコン原料ガスと、ゲルマニウム原料ガスと、エッチング成分ガスの塩化水素ガスと、搬送ガスの水素ガスとを成膜雰囲気に供給して、凹部の内面に沿って不純物を含まない第1SiGe層17を形成し、各ガスをその供給量を調整しながら成膜雰囲気に導入しつつ、不純物を含む不純物原料ガスを徐々に成膜に必要な所定量まで増加させながら成膜雰囲気に供給して、凹部の第1SiGe層17上に不純物を含む第2SiGe層18を形成してなることを特徴とする。

(もっと読む)

半導体装置

【課題】1つの整流又はショットキーバリアコンタクトを含む電界効果トランジスタのような金属半導体化合物/半導体の接合領域を含む半導体装置の提供。

【解決手段】所定のドーピングレベルの半導体基板2に形成された第1および第2電極6を有する半導体装置1であって、第1および第2電極6は半導体領域5により互いに分離され、第3電極3は半導体領域5の導電性を制御し、第1および第2電極6の少なくとも1つは半導体領域5と整流コンタクトを形成し、整流コンタクトはポテンシャルバリアを有する半導体装置を提供する。本発明によれば、少なくとも第1および第2電極の間の方向に対して、半導体領域5は、半導体基板2のドーピングレベルより高いドーピングレベルを有するように均一にドープされ、動作中に、少なくとも1つの整流コンタクトのポテンシャルバリアを低くする鏡像力メカニズムを誘起する。更に、そのような半導体装置の製造方法。

(もっと読む)

1 - 20 / 28

[ Back to top ]