Fターム[5F140AA30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 大電流化 (642) | 低オン抵抗化 (457)

Fターム[5F140AA30]に分類される特許

201 - 220 / 457

半導体装置

【課題】絶縁ゲート構造を有する横型の高耐圧半導体装置において、セル面積の増大を抑えつつ、素子全体の耐圧を向上させること。

【解決手段】平面レイアウトにおいて、トラック形状のゲート電極38は、直線状に延びるコレクタ電極40を囲む。トラック形状のエミッタ電極37は、ゲート電極38を囲む。トラック形状の第1分離トレンチ43aは、エミッタ電極37を囲む。第2分離トレンチ43bは、第1分離トレンチ43aを囲む。第1分離トレンチ43aと第2分離トレンチ43bの間の領域は、n型の分離シリコン領域44である。分離シリコン領域44は、エミッタ電極37と同電位になっている。ゲート電極38を通る切断線Q−R−Sにおける断面構成において、ゲート電極38の弧状部分に対応するR−S間のpベース領域の深さは、ゲート電極38の直線状部分に対応するQ−R間のpベース領域の深さよりも浅い。

(もっと読む)

半導体装置及びその製造方法

【課題】ホットキャリアの生成を可及的に抑制してインパクトイオンによる電流を減少させ、パンチスルーが少なく安定した閾値を得ることができ、オン抵抗の低い十分な耐圧を得ることを可能とする高耐圧トランジスタを実現する。

【解決手段】高耐圧トランジスタにおいて、チャネル領域14を、p型不純物を高濃度に有する高濃度領域14aと、n型不純物領域13a(オフセット不純物領域19)の端部と高濃度領域14aの端部との間の領域であって高濃度領域14aよりもp型不純物を低濃度に有する低濃度領域14bとから構成する。

(もっと読む)

横型半導体装置

【課題】 バイポーラで動作する横型半導体装置において、オン電圧を低くする技術を提供する。

【解決手段】 半導体装置10は、半導体層54の表面に設けられている第1主電極20と第2主電極2を備えている。半導体層54は、第1主電極20に接触しているn型の第1半導体領域24と、第2主電極2に接触しているp型の第2半導体領域58と、第1半導体領域24と第2半導体領域58の間に設けられているn型の第3半導体領域12を有している。第3半導体領域12は、第1半導体領域24と第2半導体領域58を結ぶ第1方向に沿って伸びている第1層8と第2層40を有している。第1層8と第2層40は、第1方向に直交する第2方向に並んでいる。第1層8は、不純物濃度が第1方向に均一である。第2層40は、第1層8よりも不純物濃度が濃く、不純物濃度が第1半導体領域24側から第2半導体領域58側に向けて増加している。

(もっと読む)

半導体装置

【課題】オン抵抗を低減できMOSFETを提供する。

【解決手段】半導体装置100は、半導体基板SBと、n-エピタキシャル層EPと、p型バックゲート領域BGと、n+ソース領域SRと、n型ドレイン領域DRと、ゲート電極GEと、n型高濃度領域HRとを備えている。n+ソース領域SRは、p型バックゲート領域BG内の主表面12に形成されている。n型ドレイン領域DRは、p型バックゲート領域BGを挟んでn+ソース領域SRと対向するように主表面12に形成されている。ゲート電極GEは、p型バックゲート領域BG上に形成されている。n型高濃度領域HRは、n-エピタキシャル層EPよりも高いn型不純物濃度を有し、p型バックゲート領域BGとn型ドレイン領域DRとの間に位置し、かつp型バックゲート領域BGとn+ソース領域SRとのpn接合部よりも主表面12から深い位置にピーク濃度を有している。

(もっと読む)

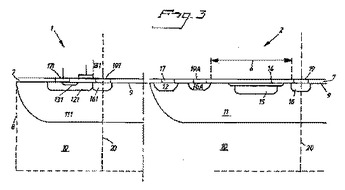

第1絶縁ゲート電界効果トランジスタが第2電界効果トランジスタと直列に接続された半導体デバイス

第1絶縁ゲート電界効果トランジスタ(1)が第2電界効果トランジスタFET(2)と直列に接続された半導体デバイスであって、前記第1絶縁ゲート電界効果トランジスタの厚くドープされたドレイン接点領域(191)へ電気的に接続されている厚くドープされたソース領域(19A)を前記第2電界効果トランジスタ(2)が有し、更に第2電界効果トランジスタ(2)のピンチ電圧Vpよりも前記第1絶縁ゲート電界効果トランジスタ(1)のブレークスルー電圧の方が高い前記半導体デバイス。  (もっと読む)

(もっと読む)

絶縁ゲート型半導体装置およびその製造方法

【課題】 絶縁ゲート型半導体素子が形成されるウェル領域は拡散領域であり、その底部ほど不純物濃度が薄くなり、抵抗が増加する問題がある。このため特に、アップドレイン構造の絶縁ゲート型半導体素子ではオン抵抗が増加する問題があった。

【解決手段】 p型ウェル領域を、2つのp型不純物領域を積層することにより構成する。それぞれのp型不純物領域は、表面にp型不純物を注入したn型半導体層を順次積層し、熱処理により同時に拡散してp型ウェル領域とする。これにより、所望の耐圧を確保するのに十分な不純物濃度が所望の深さまで略均一なp型ウェル領域を得ることができる。

(もっと読む)

半導体装置およびその製造方法

【目的】耐圧とオン抵抗のトレードオフを改善し、高耐圧で低オン抵抗のトレンチ横型パワーMOSFETなどの半導体装置およびその製造方法を提供する。

【解決手段】ピラー部30の側壁に局所的に厚い酸化膜10を形成し、さらにpリサーフ領域4と第2nドレイン領域8を形成することで、第2nドレイン領域8の不純物濃度を上げても高耐圧が得られると同時に低オン抵抗化を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 他の半導体素子とのオンチップ化が容易で高駆動能力を有する半導体装置を提供する。

【解決手段】 半導体基板1に設けられた第1導電型ウェル領域2に、トレンチ領域12を複数本設けられており、ソース電極10は、前記トレンチ領域12の間の基板表面に設けられた第2導電型ソース領域6とオーミック接合されている。また、第2導電型ソース領域6と隣接して第1導電型高濃度領域11が設けられており、第2導電型ソース領域6と共にソース電極10にバッティングコンタクトされ、基板電位が固定されるようになっている。第2導電型ドレイン領域5はトレンチ領域12の底部に設けられており、トレンチ領域12の内部に埋め込まれたドレイン電極9によって基板表面に取り出されている。ゲート電極4a、4b及びドレイン電極9に任意の電圧を印加することにより、第2導電型ソース領域6から第2導電型ドレイン領域5にキャリアが矢印8の方向流れ、半導体装置がオン状態となる。

(もっと読む)

半導体装置及びその製造方法

【課題】 トレンチによりゲート幅を広くしたMOSトランジスタからなる半導体装置の駆動能力を向上させる。

【解決手段】 ウェル領域2にはゲート幅方向にウェル領域2に凹凸構造(11a、11b)が形成されており、絶縁膜4を介して、凹部11aの内部及び凸部11bの上面部にゲート電極3が形成されている。ゲート電極3のゲート長方向の一方の側には上部ソース領域5aと下部ソース領域5bが形成されており、他方の側には上部ドレイン領域6a、下部ドレイン領域6bが形成されている。このように、ソース領域、ドレイン領域に下部ソース領域5b、下部ドレイン領域6bを形成することにより、ゲート長Lが短くなるにつれて生じるチャネル領域9の上方の電流集中を抑えチャネル領域9全体に均一に電流を流すことができるようになり、ウェル領域2に形成された凹凸構造によって実効的なゲート幅が広がる。このため、半導体装置1のオン抵抗が低下し、駆動能力が高まる。

(もっと読む)

半導体装置及びその製造方法

【課題】電力用半導体装置において十分な基板強度を確保しつつ低オン抵抗且つ高耐圧でスイッチング速度を向上できるようにする。

【解決手段】P型の半導体基板1に形成されたN型のリサーフ領域2と、半導体基板1の上部にリサーフ領域2と隣接したP型のベース領域3と、ベース領域3にリサーフ領域2と離隔したN型のエミッタ/ソース領域8と、ベース領域3にエミッタ/ソース領域8と隣接したP型のベース接続領域10と、エミッタ/ソース領域8の上からベース領域3の上及びリサーフ領域2の上に形成されたゲート絶縁膜6並びにゲート電極7と、リサーフ領域2にベース領域3と離隔したP型のコレクタ領域4とを有している。半導体基板1は、その抵抗値が半導体基板1に添加された不純物濃度で決まる抵抗値の2倍以上となるように結晶欠陥が導入されている。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】耐圧性が高い電界効果トランジスタおよびその製造方法を提供すること。

【解決手段】MOS構造を有し、窒化物系化合物半導体からなる電界効果トランジスタであって、基板と、前記基板上に形成された、リセス部を有する半導体動作層と、前記リセス部を含む前記半導体動作層上に形成された絶縁膜と、前記リセス部における前記絶縁膜上に形成されたゲート電極と、前記半導体動作層上に前記リセス部を挟んで形成され、前記半導体動作層に電気的に接続されたソース電極およびドレイン電極と、を備え、前記リセス部が前記半導体動作層に対して傾斜して立ち上がっている側壁部を有する。

(もっと読む)

MOS電界効果トランジスタ

【課題】ブレークダウン電圧を高くすること、及びオン抵抗を小さくすることの両方を実現する。

【解決手段】半導体基板上に形成され、ソースN+領域8及びボディコンタクト領域9、ゲート領域、ドリフト領域及びドレインN+領域6を備え、上記ドリフト領域がドレインN+領域6と上記ゲート領域の間に設けられるMOS電界効果トランジスタにおいて、上記ゲート領域は、ゲート電極10と、ゲート電極10から突き出た複数のトレンチ4を有し、上記ドリフト領域は、複数のトレンチ4と少なくとも1つ以上のドリフト部とが交互に配置されており、ゲート電極10は、内部に濃くドープされたポリシリコンを有し、複数のトレンチ4は、それぞれ内部に薄くドープされたポリシリコン電極5を有する。

(もっと読む)

半導体装置

【課題】オン抵抗を低減し、かつ耐圧を向上し、小型化を図る半導体装置の提供。

【解決手段】半導体装置200は、主表面12を有する半導体基板SBと、半導体基板SBに形成された絶縁ゲート型電界効果部を有する半導体素子とを備える。半導体素子は、エピタキシャル層EPとバックゲート領域BGとソース領域SRとドレイン領域DRとゲート電極GEと不純物領域IM1とを含む。バックゲート領域BGはエピタキシャル層EPとpn接合を構成し、第2導電型である。ソース領域SRはバックゲート領域BG内の主表面12に形成され、第1導電型である。ドレイン領域DRはバックゲート領域BGおよびエピタキシャル層EPを挟んでソース領域SRと対向するように主表面12に形成され、第1導電型である。不純物領域IM1はエピタキシャル層EPを挟んでバックゲート領域BGの下に位置し、かつエピタキシャル層EPとpn接合を構成し、第2導電型である。

(もっと読む)

炭化ケイ素半導体装置およびその製造方法

【課題】チャネル移動度のような電気的特性の優れた炭化ケイ素半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、面方位{0001}に対しオフ角が50°以上65°以下である、炭化ケイ素からなる基板2と、半導体層(図1のp型層4)と絶縁膜(図1の酸化膜8)とを備える。半導体層(p型層4)は基板2上に形成され、炭化ケイ素からなる。絶縁膜(酸化膜8)は、半導体層(p型層4)の表面に接触するように形成されている。半導体層と絶縁膜との界面(チャネル領域と酸化膜8との界面)から10nm以内の領域における窒素原子濃度の最大値が1×1021cm-3以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】高耐圧トランジスタを有する半導体装置において、チップサイズを大きくすることなく、高耐圧化と同時にオン電流の低減を図る。

【解決手段】N型ドレイン領域14から見てP型ボディ領域4側のN型ドリフト領域5内にトレンチオフセット領域2が形成されている。トレンチオフセット領域2のN型ソース領域13側の側面及び底面に接するように、N型ドリフト領域5の平均不純物濃度よりも低い不純物濃度を持つN型電界緩和領域7が設けられている。

(もっと読む)

二重拡散型ソースMOSFET(LDMOS)トランジスタの高ドープ領域及びその作製方法

トランジスタが、ソースと、ドレインと、ゲートとを含む。ソースは、pドープp型ボディと、p型ボディと重複するp+領域と、p+領域に近接してp型ボディと重複するn+領域と、第1のn+領域の深さに略等しい深さを有し、第1のn+領域と重複する、トランジスタのソース領域内にのみ設けられたnドープのソース高二重拡散(SHDD)領域とを含む。ドレインは、第2のn+領域と、第2のn+領域と重複するnドープの浅いドレインとを含む。ゲートは、ゲート酸化物と、ゲート酸化物上の導電材料とを含む。SHDD領域は、ゲート酸化物の下方で第1のn+領域より更に横方向に延びる。SHDD領域は、nドープの浅いドレインのドーパント濃度より高く、第1のn+領域のドーパント濃度より低いドーパント濃度を用いて注入される。 (もっと読む)

半導体装置及びその製造方法

【課題】 低コストで製造が可能な低オン抵抗且つ高耐圧な半導体装置及びその製造方法を提供する。

【解決手段】 P型の半導体基板1上に形成された、N型のウェル領域2と、ウェル領域2内に形成されたP型のボディ領域3と、ボディ領域3内に形成されたN型のソース領域6と、ウェル領域2内において、ボディ領域3とは離間して形成されたN型のドレイン領域8と、ボディ領域3の一部上層を含む領域に形成されたゲート絶縁膜12と、ゲート絶縁膜12上層に形成されたゲート電極9と、ウェル領域2内において、ボディ領域3の底面に接触すると共に、半導体基板1面と平行方向にドレイン領域8の下方領域に延在するP型の埋め込み拡散領域4と、を備える。

(もっと読む)

横型MOSFET

【課題】従来の横型MOSFET20は、オン抵抗低減のために配置された比較的高い不純物濃度を有するN型不純物領域44の近傍で空乏層aが延びにくく、ゲート電極39のドレイン側端部まで達せず、ドレイン側端部に集中する高電界でホットキャリアが発生し、Vtが変動するという不具合があった。

【解決手段】本発明の横型MOSFET1は、P+型ベース領域35とN++型ドレイン領域36の間のN−型半導体層33の表面層に、N−型半導体層33より高い不純物濃度を有するN+型高濃度領域5と、その表面層に、一端をP+型ベース領域35に接しつつN++型ドレイン領域36に向かって延在するN+型高濃度領域5よりも低い不純物濃度を有する複数のN−型低濃度領域6とを有する。

(もっと読む)

半導体装置

【課題】 トレンチ構造を有する横型半導体装置の駆動能力を向上させる。

【解決手段】 ウェルには、ゲート幅方向にウェルに凹凸を設けるためのトレンチ部が形成されており、絶縁膜を介して、トレンチ部の内部及び上面部にゲート電極が形成されている。ゲート電極のゲート長方向の一方の側にはソース領域が形成されており、他方の側にはドレイン領域が形成されている。ソース領域とドレイン領域は、何れも、トレンチ内部に充填された不純物を含む多結晶シリコンからの不純物拡散によって形成され、ゲート電極の底部近傍(トレンチ部の底部近傍)の深さまで形成されている。このように、ソース領域とドレイン領域を深く形成することで、ゲート電極部位で浅い部分に集中して流れていた電流がトレンチ部の全体に一様に流れるようになり、ウェルに形成された凹凸によって実効的なゲート幅が広がる。この結果、半導体装置のオン抵抗が低下し、駆動能力が高まる。

(もっと読む)

GaN系半導体装置

【課題】エレクトロマイグレーションの発生を抑制でき、GaN系半導体素子の低オン抵抗という利点を維持しつつ、信頼性の向上を図ったGaN系半導体装置を提供する。

【解決手段】GaN系半導体装置20は、オン状態で2つの電極間で能動層25を介して電流が流れるソース電極31およびドレイン電極32と、ゲート電極33と、裏面電極34とを備える。ソース電極31は、能動層25におけるソース電極31を形成する部分を、能動層25の表面側からP型のシリコン基板21に達する深さまで掘った溝27の内壁面に、その表面側からシリコン基板21と接触する位置まで延びている。ソース電極31には、シリコン基板21および能動層25の両方にオーミック接合する金属を用いている。

(もっと読む)

201 - 220 / 457

[ Back to top ]