Fターム[5F140AA30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 大電流化 (642) | 低オン抵抗化 (457)

Fターム[5F140AA30]に分類される特許

141 - 160 / 457

GaN系電界効果トランジスタの製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタの製造方法を提供する。

【解決手段】 GaN系電界効果トランジスタの製造方法は、基板101上にAlN層102、バッファ層103、チャネル層104、ドリフト層105および電子供給層106をエピタキシャル成長させる工程と、リセス部108を形成する工程と、アロイ工程におけるアニール時に電子供給層106を保護する保護膜113を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、オーミック接触を得るためのアニールを行なうアロイ工程と、保護膜113を除去し、ゲート絶縁膜を、リセス部108の内表面、電子供給層106、ソース電極109、ドレイン電極110および素子分離部分130上に形成する工程と、リセス部108のゲート絶縁膜上にゲート電極を形成する工程とを備える。

(もっと読む)

半導体装置

【課題】オン抵抗の増加を抑制する半導体装置を提供する。

【解決手段】本発明の半導体装置は、第1導電型の半導体基板1と、第2導電型の延長ドレイン層2と、第1導電型のコレクタ層4と、コレクタ電極5と、第1導電型ベース層8と、複数の第2導電型エミッタ層9と、第1導電型コンタクト層10と、エミッタ電極11と、ゲート酸化膜12と、ゲート電極13とを備え、ベース層8はエミッタ電極11からコレクタ電極5に向かう方向に対して垂直方向に離散的に形成されており、コンタクト層10のコレクタ電極5側界面は、複数のエミッタ層9に隣接する領域ではゲート電極13のエミッタ層9側界面の直下まで形成されており、コンタクト層10のコレクタ電極5側界面は、エミッタ層9の直下においてはゲート電極13のエミッタ層9側界面よりもエミッタ電極11側に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】フィン型電界効果トランジスタの寄生抵抗を低減し、駆動電流を増大させる。

【解決手段】半導体基板本体部101と、半導体基板本体部101の上に突成された、フィン108と、を有し、フィン108は、両端側の一対のソース/ドレイン領域106および一対のソース/ドレイン領域106に挟まれたチャネル領域107を有するものとして構成された、半導体基板と、

半導体基板本体部101の上に形成された、シリコン酸化物からなる、素子分離絶縁膜102と、

素子分離絶縁膜102の上に形成された、シリコン窒化物又はシリコン炭窒化物からなる、被膜109と、

チャネル領域107におけるフィン108の上に形成されたゲート絶縁膜と、

ゲート絶縁膜を介してフィン108におけるチャネル領域107を挟むように形成された、ゲート電極103と、

ソース/ドレイン領域106を覆うと共に被膜109と隙間なく当接する、応力印加層105と、を備える。

(もっと読む)

電気的にプログラムされたソース/ドレイン直列抵抗を有するMOSトランジスタ

【課題】高速度MOSFETを形成するための半導体デバイス技術が要請されている。

【解決手段】トランジスタゲートサイドウォールスペーサ(27)に埋め込まれた導電層(24)を形成することによって高速MOSトランジスタ(32)は、用意される。この埋め込まれた導電層(24)は、トランジスタ(32)のゲート電極(18)とソース/ドレイン領域(28)から電気的に絶縁している。埋め込まれた導電層(24)は、ソース/ドレイン伸長領域(30)を覆うように配置され、ソース/ドレイン領域(28)直列抵抗を低くすることでソース/ドレイン伸長領域内に電荷を蓄積する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ドリフト領域を自己整合的に決定することができ、オン抵抗の小さいDMOS

トランジスタを含む半導体装置の製造方法を提供することを目的とする。

【解決手段】

ドレイン領域24側のサイドウォール32が、ソース領域22側の前記サイドウォール

31に比べ水平方向の厚さが厚く、かつ、ドレイン領域24が形成されたP−型半導体層

2表面及びソース領域22が形成されたP−型半導体層2の表面が、ゲート酸化膜10底

部のP−型半導体層2表面及びサイドウォール31、32底部のP−型半導体層2表面よ

り低い位置に形成され、さらにシリサイド層35aがゲート電極11上面のドレイン領域

24側端まで形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】移動体通信装置用半導体装置(RFパワーモジュール)の電力付加効率を向上させる。

【解決手段】パワーMOSFETのゲート電極7とn+型ドレイン領域15との間に介在するオフセットドレイン領域を二重オフセット構造とし、ゲート電極7に最も近いn−型オフセットドレイン領域9の不純物濃度を相対的に低く、ゲート電極7から離間したn型オフセットドレイン領域13の不純物濃度を相対的に高くする。これにより、オン抵抗(Ron)と帰還容量(Cgd)を共に小さくすることができるので、増幅素子をシリコンパワーMOSFETで構成したRFパワーモジュールの小型化と電力付加効率の向上を図ることができる。

(もっと読む)

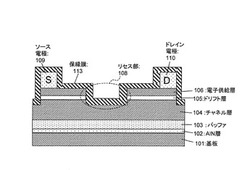

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ(MOSFET)100は、基板101上に、p−GaNからなるチャネル層104、電子供給層106、電子供給層よりもバンドギャップエネルギーが小さい表面層107を順次積層し、電子供給層および表面層の一部をチャネル層に到る深さまで除去してリセス部108を形成したものである。表面層上には、リセス部を挟んでソース電極109およびドレイン電極110が形成され、表面層上およびチャネル層表面を含むリセス部内表面上にゲート絶縁膜111が形成され、さらにリセス部においてゲート絶縁膜上にはゲート電極112が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ゲート絶縁膜形成工程のような大きな熱負荷を避けて、チャネルの最上面の不純物濃度を薄くした、深さ方向のドーピング・プロファイルを実現し、オン電流が向上する半導体装置の製造方法を提供することである。

【解決手段】 ゲート電極形成後にゲート電極をマスクにして角度10度以下でチャネル不純物をイオン注入し、この後、チャネル不純物の活性化を、基板表面から所定の深さのチャネル不純物濃度がゲート長方向に一定になるように、RTAを用いたアニールで行う、さらに、その後のエクステンション/ハロー注入、深いS/D注入の後の活性化を、拡散レスアニールで行う。

(もっと読む)

半導体装置及びその製造方法

【課題】 オン抵抗の小さいDMOSトランジスタを含む半導体装置の製造方法を提供することを目的とする。

【解決手段】

CMOSトランジスタ1は、ゲート電極9と、N+型のソース領域3と、N+型のドレイン領域4を備える。DMOSトランジスタ21は、ゲート電極29と、N+型のソース領域23と、N―型のドリフト領域30と、ドレイン領域24と、シリサイド層32aを備える。ゲート電極9のソース領域3側とドレイン領域4側の側部にはサイドウォール8Bが設けられ、ゲート電極29のソース領域23側とドレイン領域24側の側部にはサイドウォール28C、28Dが設けられている。ドレイン領域24側のサイドウォール28Cは、ソース領域23側のサイドウォール28D、及びサイドウォール2Bよりもチャネル方向に沿う厚さが厚い。さらに、シリサイド層32aがゲート電極9上面のドレイン領域24側端まで形成されている。

(もっと読む)

半導体素子及びその製造方法

【課題】本発明は、半導体素子及びその製造方法を提供する。

【解決手段】実施の形態による半導体素子は第2導電型(N型)のウェル110が形成された基板100、及びドレイン領域150を含み、前記基板100に形成されるLDMOS素子として、前記ドレイン領域150の一側に形成されるフィールドオキサイド130と、前記フィールドオキサイド130下側の基板に形成される第1導電型不純物層161、162、163と、前記第1導電型不純物層161、162、163とフィールドオキサイド130の間に形成される第2導電型不純物層171、172、173と、を含むLDMOS素子を含む。本実施の形態はLDMOS素子のブレークダウン電圧を増加させて素子の内圧を高めると共に、電流の移動距離を短縮させてオン抵抗を減少させることができる。

(もっと読む)

横型MOSトランジスタ

【課題】

オン抵抗の低減を図った横型MOSトランジスタを提供する。

【解決手段】

第1導電型の半導体層と、半導体層の第1領域に深さ方向に形成される第1酸化膜と、半導体層の第1領域とは離間した第2領域に深さ方向に形成される第2酸化膜と、半導体層内で第1酸化膜に隣接する領域に深さ方向に形成されるゲート電極と、半導体層内で第2酸化膜に隣接する領域に形成される制御電極と、半導体層の第1酸化膜と第2酸化膜で挟まれる領域の表面部のうちの第1酸化膜の近傍の領域に形成される第2導電型領域と、第2導電型領域の表面部のうちの第1酸化膜の近傍の領域に形成される第1導電型領域と、第1導電型領域及び第2導電型領域の上に形成されるソース電極と、半導体層の第1酸化膜と第2酸化膜で挟まれる領域の表面部のうちの第2酸化膜の近傍の領域に形成される第1導電型領域と、第1導電型領域の上に形成されるドレイン電極とを含む。

(もっと読む)

半導体素子及びその製造方法

【課題】LDMOS素子においてのオン抵抗を減少させることができる半導体素子及びその製造方法を提案する。

【解決手段】本実施例による半導体素子は、第1導電型のウェル110が形成された基板100と、及びゲート電極182を含んで、前記基板100に形成されるLDMOS素子として、前記ゲート電極182一側の基板100に形成されるソース領域132と、前記ゲート電極182他側の基板100に形成されるドレイン領域133と、前記ゲート電極182下側の基板100に形成される第1導電型の不純物層140を含むLDMOS素子と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】CMISのソース・ドレイン領域端部における転位の発生および拡散抵抗の上昇を防止する。

【解決手段】CMISにおけるソース・ドレイン領域12、14の形成時、シリコン基板1に不純物をイオン注入する前に、Pウエル層4には転位抑制元素としてアルゴンを打ち込み、かつNウエル層5には窒素を転位抑制元素として打ち込む。これにより転位の発生を抑制しつつ、かつ、Pウエル層4とNウエル層5それぞれに適した転移抑制元素を打ち分けることで拡散抵抗の上昇を抑制し、歩留まりを向上させ、素子の信頼性を高めることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】低い閾値電圧を有するFETおよび高い閾値電圧を有するFETのいずれも高性能な特性を有する半導体装置を提供する。

【解決手段】半導体装置100は、FET102と、FET102よりも高い閾値電圧を持つFET104を同一半導体基板上に備える。FET102は、ゲート絶縁膜114とゲート電極126を備える。FET104は、ゲート絶縁膜114とゲート電極121を備える。FET102のゲート電極126、FET104のゲート絶縁膜114、ゲート電極121はHf、Zr、Al、La、Pr、Y、Ta、Wからなる群から選択される少なくとも一つの金属を含む。FET104のゲート絶縁膜114とゲート電極121との界面における前記金属の濃度は、FET102のゲート絶縁膜114とゲート電極126との界面における前記金属の濃度よりも高い。

(もっと読む)

リサーフ構造を用いた電界効果トランジスタ

【課題】炭化珪素基板上に、高耐圧で低抵抗なMOS電界効果トランジスタを形成する。

【解決手段】第1の導電型を持つ炭化珪素半導体の活性層(1)と、該活性層の表面部分に形成された第2の導電型のソース領域(4)と、該ソース領域から間隔をおくように形成された第2の導電型のドリフト領域(2)と、該ドリフト領域の表面部分に形成された第1の導電型の電界緩和領域(6)と、第2の導電型のドレイン領域(3)と、ソース領域とドリフト領域とで挟まれた領域の上に形成されたゲート絶縁膜(11)及びゲート電極(12)と、を具備する。電界緩和領域(6)は、互いの投影方向においてゲート電極(12)と重なる部分を持ち、ドリフト領域上のゲート電極(12)の端点の位置(II)から電界緩和領域のドレイン側の端点(IV)までの長さは、電界緩和領域の該端点(IV)からドレイン領域の端点(I)までの長さよりも短い。

(もっと読む)

半導体装置及びその製造方法

【課題】静止耐圧の向上と低オン抵抗化とを両立できる半導体装置及びその製造方法を提供する。

【解決手段】P型の半導体基板111内に下から順にN- 型の第1ドレインオフセット領域112、N- 型の第2ドレインオフセット領域113、及びN- 型の第3ドレインオフセット領域114が形成されている。第2及び第3ドレインオフセット領域113及び114内にP- 型のボディ領域115が形成されている。第2ドレインオフセット領域113の不純物濃度は、第1及び第3ドレインオフセット領域112及び114よりも低い。ボディ領域115のカーバチャー部131は第2ドレインオフセット領域113内に位置する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐圧確保とターンオフタイム短縮の両立が可能なIGBT構造を有する半導体装置を提供する。

【解決手段】縦型IGBT構造とPMOSFET30とが半導体基体上に一体で形成されている半導体装置10を構成する。この半導体装置は、PMOSFET30のドレイン電極29と、IGBTのコレクタ11とが電気的に接続されている。また、PMOSFET30のソース領域(第2のベース領域14)とドリフト領域12とにまたがって形成されたドリフト領域の取り出し領域(NSD19)が、PMOSFET30のソース領域の取り出し領域(PSD20)と導電膜により接続されている。

(もっと読む)

窒化物半導体素子

【課題】本発明は、低オン抵抗でノーマリーオフ型の窒化物半導体素子を提供する。

【解決手段】本発明の一態様によれば、p型窒化物半導体の第1の半導体層と、第1の半導体層上に設けられたアンドープ窒化物半導体の第2の半導体層と、第2の半導体層上に選択的に設けられたアンドープまたはn型窒化物半導体の第3の半導体層と、第3の半導体層上に設けられた第1の主電極と、第3の半導体層上に設けられた第2の主電極と、第2の半導体層上に設けられた絶縁膜と、絶縁膜上に設けられた制御電極と、を備え、第3の半導体層のバンドギャップは、第2の半導体層のバンドギャップよりも大きく、制御電極は、第1の主電極と第2の主電極との間に位置することを特徴とする窒化物半導体素子が提供される。

(もっと読む)

半導体装置

【課題】起動回路と周辺回路とを併せて集積化し得る半導体装置を提供する。

【解決手段】領域411においては、素子分離領域により規定されるドレイン領域121にボディ領域が形成され、ボディ領域にN型のソース領域が形成される。ドレイン領域121とN型のソース領域との間に第1のゲート電極20が配置される。素子分離領域は開口部133が形成されたループ状部と、開口部133を介してドレイン領域121に接続された延在領域122を規定する部分とを備える。延在領域122に、N型のソース引出領域が形成される。内部回路412においては、ドレイン領域121にP型のボディ領域が形成され、P型のボディ領域にN型のソース領域が形成され、ドレイン領域121とN型のソース領域との間に第2のゲート電極331が形成される。

(もっと読む)

埋設導電層を備えた高電圧トランジスタ

【課題】埋設導通層を備えた低オン抵抗値の横方向高電圧FETを提供する。

【解決手段】P−型基板に形成されたN−ウエル内にP−型埋設層領域を設け、これをN−ウエル領域に形成された第1のP−型ドレイン拡散領域によってドレイン電極に接続すると共に、PMOSゲート領域の一端で表面から下方に延びる第2のP−型ドレイン拡散領域にも接続し、ソース電極に接続されるP−型ソース拡散領域でゲート領域の他端を定めるようにする。

(もっと読む)

141 - 160 / 457

[ Back to top ]