Fターム[5F140AA30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 大電流化 (642) | 低オン抵抗化 (457)

Fターム[5F140AA30]に分類される特許

61 - 80 / 457

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

半導体装置

【課題】低オン抵抗且つ高アバランシェ耐量の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第2導電型の第1のソースコンタクト領域21と第1導電型のバックゲートコンタクト領域22とを有する第1のソース部S1と、第2導電型の第2のソースコンタクト領域24を有し、第1導電型のバックゲートコンタクト領域を有さない第2のソース部S2と、第2導電型のドレインコンタクト領域15と、第1のソースコンタクト領域21側に形成された第2導電型の第1のドリフト領域16と、第2のソースコンタクト領域24側に形成された第2導電型の第2のドリフト領域17とを有するドレイン部Dと、を備え、第2のドリフト領域17の方が第1のドリフト領域16よりもチャネル長方向の長さが長い。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、チャネル抵抗を減少させてオン電流を増加させることが可能で、かつ各トランジスタを独立して、安定して動作させることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】Y方向に延在するように半導体基板13に設けられ、底面18c及び対向する第1及び第2の側面18a,18bを有するゲート電極用溝18と、ゲート絶縁膜21を介して、ゲート電極用溝18の下部を埋め込むように配置されたゲート電極22と、ゲート電極用溝18を埋め込むように配置され、ゲート電極22の上面22aを覆う埋め込み絶縁膜24と、第1の側面18aに配置されたゲート絶縁膜21の上部21Aを覆うように、半導体基板13に設けられた第1の不純物拡散領域28と、少なくとも第2の側面18bに配置されたゲート絶縁膜21を覆うように、半導体基板13に設けられた第2の不純物拡散領域29と、を有する。

(もっと読む)

高耐圧トランジスタ及びその製造方法

【課題】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法を提供する。

【解決手段】高い降伏電圧を有する高耐圧トランジスタ及びそれの製造方法において、半導体基板の所定部位が酸化された第1絶縁膜パターン、及び第1絶縁膜パターンを少なくとも部分的に取り囲む第2絶縁膜パターンを形成する。基板上に導電性物質を蒸着して、第1端部は第1絶縁膜パターン上に位置し、第2端部は第2絶縁膜パターン上に位置するゲート電極を形成した後、基板表面の所定部位に不純物を注入してソース/ドレイン領域を形成する。ゲート電極のエッジ部分に集中される電界を緩和して高い降伏電圧を有するトランジスタを製造することができ、熱酸化膜パターンとCVD酸化膜パターンをゲート酸化膜として使用することで、MOSトランジスタにおいて電流特性及びON抵抗特性を改善することができる。

(もっと読む)

窒化物半導体電界効果トランジスタ

【課題】通常の極性面上(すなわちc軸方向)に形成するエンハンスメント型の窒化物半導体電界効果トランジスタとして、高い密度のドレイン電流を実現することが可能にする。

【解決手段】窒化物半導体からなるチャネル層半導体6の上方の極性面方向に、チャネル層半導体6よりもバンドギャップの大きい窒化物半導体からなる障壁層半導体5が積層され、ゲート電極2の下方に存在する素子領域のうち少なくとも一部の素子領域を覆う第1領域21内に存在する障壁層半導体5の層厚が、第1領域21以外の素子領域を覆う第2領域22内に存在する障壁層半導体5の層厚よりも薄く形成されるか、または、第1領域21内には障壁層半導体5が存在しない状態で形成されるとともに、第2領域22内に存在する障壁層半導体5中に、障壁層半導体5よりもバンドギャップが小さい単一層の量子井戸7または多重層の多重量子井戸を挿入した量子井戸構造が形成される構造にする。

(もっと読む)

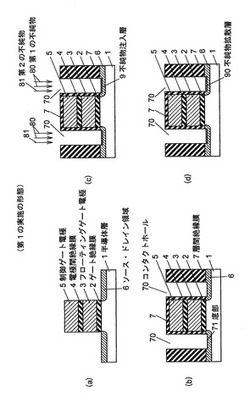

半導体装置およびその製造方法

【課題】ゲート電圧の閾値電圧がばらつくことを抑制することができると共に、チャネル抵抗を低減させることができる半導体装置を提供する。

【解決手段】ベース領域4、ソース領域6、ドレイン領域7の不純物濃度を均一とし、第1、第2トレンチ8a、8bをベース領域4よりも浅く形成する。このような半導体装置では、ベース領域4、ソース領域6、ドレイン領域7の不純物濃度が均一とされているため、ゲート電圧の閾値電圧がばらつくことを抑制することができ、また、ソース領域6およびドレイン領域7を深くすることによりチャネル領域を有効に活用でき、チャネル抵抗を低減することができる。さらに、第1、第2トレンチ8a、8bをベース領域4より浅く形成しているため、ベース領域4のうち第1、第2トレンチ8a、8bより深く形成されている部分にはチャネル領域が形成されず、ソース領域6から深さ方向に電流が流れることを抑制することができる。

(もっと読む)

MOSゲート型炭化珪素半導体装置の製造方法

【目的】チャネル移動度を大きくし、チャネル抵抗を低減できるMOSゲート型炭化珪素半導体装置の提供。

【構成】トレンチの側壁に接するゲート酸化膜とチャネル反転層表面との間に他導電型シリコン半導体層が形成されるMOSゲート型炭化珪素半導体装置であって、他導電型シリコン半導体層がアモルファスシリコン層で形成し、レーザー光を前記アモルファスシリコン層に対して前記MOSゲート型炭化珪素半導体装置のチャネル電流が流れる方向と交差しない方向へスキャンしてアモルファスシリコン層をポリシリコンに変換する。

(もっと読む)

半導体装置

【課題】コンタクトホールの位置合わせが容易で、コンタクト抵抗の低いフィン型の電界効果型トランジスタを有する半導体装置に提供する。

【解決手段】フィン型の電界効果型トランジスタであって、ソース/ドレイン領域503の少なくともその幅が最も大きい部分では半導体領域502の幅よりも大きく、かつソース/ドレイン領域503の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部510を有し、該傾斜部表面にシリサイド膜504が形成されていることを特徴とする半導体装置とする。

(もっと読む)

半導体装置

【課題】移動体通信装置用半導体装置(RFパワーモジュール)の電力付加効率を向上させる。

【解決手段】パワーMOSFETのゲート電極7とn+型ドレイン領域15との間に介在するオフセットドレイン領域を二重オフセット構造とし、ゲート電極7に最も近いn−型オフセットドレイン領域9の不純物濃度を相対的に低く、ゲート電極7から離間したn型オフセットドレイン領域13の不純物濃度を相対的に高くする。これにより、オン抵抗(Ron)と帰還容量(Cgd)を共に小さくすることができるので、増幅素子をシリコンパワーMOSFETで構成したRFパワーモジュールの小型化と電力付加効率の向上を図ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】3次元構造のパワーMOSトランジスタやIBGTの破壊耐量を改善する。

【解決手段】一つの実施形態の半導体装置には、N+基板1に溝21が設けられ、溝21に積層形成されるN層2、N−層3、P層4、及びN+層5が溝21を覆うように設けられる。N+層5に、N+基板1に対して垂直方向では一部がN+層5を貫通してP層4表面が露呈され、N+基板1に対して水平方向では一部がN+層5を貫通してP層4側面が露呈するように溝22が設けられ、溝22にP+層6が溝22を覆うように設けられる。N+基板1に対して垂直方向では、N+層5を貫通してP層4表面が露呈され、N+基板1に対して水平方向では、P層4を貫通して一端でN−層3側面が露呈し、他端でN+層5側面が露呈し、P+層6の間及び側面と離間して配置形成される溝23が設けられる。溝23に、トレンチゲート11が溝23を覆うように設けられる。

(もっと読む)

炭化ケイ素半導体デバイス

【課題】航空機の配電システムでの使用に際しても、十分に信頼できる炭化シリコンを使用したMOSFETを提供する。

【解決手段】炭化シリコンMOSFETのゲート絶縁膜16を、シリコンからなる第1の層と炭化シリコンからなる第2の層15に貼着することによって、第1の層と第2の層との間に境界面を形成した後、シリコンからなる第1の層の一部又は全部を酸化することにより境界面に炭素クラスターの存在しないゲート絶縁膜16を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】パワーデバイスの高耐圧とオン抵抗の低減とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板101内のソース領域107A、ドレイン領域107B、及びドレイン領域107Bに接したドリフト領域105と、ソース領域107A及びドレイン領域107B間のドリフト領域105内のSTI絶縁層I−2と、STI絶縁層I−2上、ドリフト領域105上、並びに、ソース領域107A及びドレイン領域107B間のチャネル領域上のゲート電極110とを備える。STI絶縁層I−2は、第1及び第2のトレンチの内面上の第1の酸化膜102及び窒化膜103と、第1及び第2のトレンチを満たす窒化膜103上の第2の酸化膜104とを備える。第2のトレンチは、第1のトレンチ内に形成され、第1のトレンチの底面よりも低い底面を有し、第1のトレンチの幅よりも狭い幅を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明の実施形態は、電気抵抗を低減させることができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、第1導電型のチャネル形成領域と、第2導電型の第1オフセット領域と、前記第1オフセット領域の表面に埋め込まれている第1絶縁膜領域と、前記第1オフセット領域と前記第1絶縁膜領域との間に設けられた第1ライナ層と、前記第1絶縁膜領域を挟んで前記チャネル形成領域とは反対側に形成され、前記第1オフセット領域よりも不純物濃度の高い第2導電型の第1半導体領域と、前記チャネル形成領域を挟んで前記第1半導体領域とは反対側に形成され、前記第1オフセット領域よりも不純物濃度の高い第2導電型の第2半導体領域と、前記チャネル形成領域上及び前記第1オフセット領域上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置

【課題】オフ時のリーク電流を低減し、パワースイッチング素子に適用可能なノーマリーオフ型の半導体装置を提供する。

【解決手段】基板101と、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成されたアンドープAlGaN層104と、アンドープGaN層103又はアンドープAlGaN層104の上に形成されたソース電極107及びドレイン電極108と、アンドープAlGaN層104の上に形成され、ソース電極107とドレイン電極108との間に配置されたp型GaN層105と、p型GaN層105の上に形成されたゲート電極106とを備え、アンドープGaN層103は、チャネルを含む活性領域113と、チャネルを含まない不活性領域112とを有し、p型GaN層105は、ソース電極107を囲むように配置されている。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧を向上した半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、第1半導体領域、第2半導体領域、第3半導体領域、第4半導体領域、ゲート領域、ゲート絶縁膜及び電界緩和領域を備える。第1導電形の第1半導体領域は、第1部分と第1方向に延出した第2部分とを有する。第1導電形の第2半導体領域は、第1部分上の第3部分と第2部分と隣接する第4部分とを有する。第2導電形の第3半導体領域は、第3部分上の第5部分と第4部分と隣接する第6部分とを有する。第1導電形の第4半導体領域は、第5部分上で第6部分と隣接する。ゲート領域は、第2半導体領域、第3半導体領域及び第4半導体領域を第2方向に貫通するトレンチ内に設けられる。ゲート絶縁膜は、トレンチ内壁とゲート領域との間に設けられる。第2導電形の電界緩和領域は、第3部分と第5部分との間に設けられ、第3半導体領域よりも不純物濃度が低い。

(もっと読む)

化合物半導体装置

【課題】ゲート電極の端部でのバイアス電界集中が緩和され、且つ動作時のオン抵抗の増大が抑制された化合物半導体装置を提供する。

【解決手段】キャリア供給層22、及びキャリア供給層22との界面近傍において二次元キャリアガス層23が形成されるキャリア走行層21を有する化合物半導体層20と、化合物半導体層20の主面200上に配置されたソース電極3及びドレイン電極4と、ソース電極3とドレイン電極4間で主面200上に配置されたゲート電極5と、ゲート電極5とドレイン電極4間で主面200上方に配置されたフィールドプレート6と、フィールドプレート直下の二次元キャリアガス層が形成される領域内に配置された、上方にフィールドプレート若しくはゲート電極が配置されていない二次元キャリアガス層が形成される領域よりも導電率が低い低導電性領域210とを備える。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】オン抵抗を低減した半導体装置の製造方法及び半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、半導体層の表面側に、第1のフィールド絶縁膜と前記第1のフィールド絶縁膜に対して離間し且つ前記第1のフィールド絶縁膜よりも浅い少なくとも1つの第2のフィールド絶縁膜とを同時に形成する工程を備えた。さらに、前記半導体層における前記第1のフィールド絶縁膜及び前記第2のフィールド絶縁膜が形成された領域に第1導電形のドリフト領域を形成する工程を備えた。さらに、前記半導体層における前記第1のフィールド絶縁膜側の表面に、前記ドリフト領域よりも第1導電形不純物濃度が高い第1導電形のドレイン領域を形成する工程を備えた。さらに、前記半導体層における前記第2のフィールド絶縁膜側の表面に、第1導電形のソース領域を形成する工程を備えた。

(もっと読む)

半導体装置およびこの半導体装置に用いられる半導体デバイス

【課題】オン抵抗を十分なレベルにまで低減させる。

【解決手段】半導体装置は、半導体デバイス1と、制御装置2とを備える。半導体デバイス1において、本体部3では、半導体層33と第2の半導体層34とが積層し、半導体層33と第2の半導体層34との間の界面の半導体層33側にチャネル領域36が形成される。ソース電極41およびドレイン電極42は、チャネル領域36に電気的に接続されるように本体部3の上に離隔して設けられている。ゲート電極43は、ソース電極41とドレイン電極42との間であって第2の半導体層34の上方に設けられている。制御装置2は、ゲート電極43へのゲート電圧を調節してチャネル領域36において電子91を移動させるとともに、チャネル領域36において電子91を移動させているときに、チャネル領域36のバンドギャップより大きいエネルギーの光を光源5が半導体層33に照射するように光源5を制御する。

(もっと読む)

双方向スイッチ及びその製造方法

【課題】トレンチゲート構造で共用ドレインを有する2つのMOS型トランジスタから構成される双方向スイッチのオン抵抗の低減を図る。

【解決手段】N型ウエル層2に複数のトレンチ3を形成する。次に前記複数のトレンチ3に挟まれたN型ウエル層2に1列おきにP型ボディ層6を形成する。複数のP型ボディ層6にはN+型第1ソース層7とN+型第2ソース層9を交互に形成する。N+型第1ソース層7を挟む1対のトレンチ3のそれぞれに第1ゲート電極5a、N+型第2ソース層9を挟む1対のトレンチ3のそれぞれに第2ゲート電極5bを形成する。第1ゲート電極5aが形成されたトレンチ3のP型ボディ層6側と反対側の側壁と第2ゲート電極5bが形成された同様の側壁に挟まれたN型ウエル層2を電界緩和層としてのN型ドレイン層11aとする。該N型ドレイン層11aを双方向スイッチのオン電流の流れる電流経路とする。

(もっと読む)

半導体装置

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

61 - 80 / 457

[ Back to top ]