Fターム[5F140AA30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 大電流化 (642) | 低オン抵抗化 (457)

Fターム[5F140AA30]に分類される特許

161 - 180 / 457

埋設導電層を備えた高電圧トランジスタ

【課題】埋設導通層を備えた低オン抵抗値の横方向高電圧FETを提供する。

【解決手段】P−型基板に形成されたN−ウエル内にP−型埋設層領域を設け、これをN−ウエル領域に形成された第1のP−型ドレイン拡散領域によってドレイン電極に接続すると共に、PMOSゲート領域の一端で表面から下方に延びる第2のP−型ドレイン拡散領域にも接続し、ソース電極に接続されるP−型ソース拡散領域でゲート領域の他端を定めるようにする。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方にはトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、ソース電極層を基板水平方向に流れる電流の経路において、素子領域内で抵抗の偏りが発生する問題もあった。

【解決手段】電極構造を2層とし、2層目のゲート電極層(ゲートパッド部)の下方にトランジスタセルおよび1層目のソース電極層を配置する。2層目のゲート電極層は一部が1層目のゲート電極層と重畳し、これを介してゲート電極と接続する。ゲートパッド部下方にセルおよび1層目のソース電極層を配置できるので、ゲートパッド部下方の無効領域を従来と比較して大幅に低減できる。またソース電極層内を基板の水平方向に流れる電流について、全てのセルがソースパッド部から最短距離の電流経路となる。

(もっと読む)

半導体装置およびその製造方法

【課題】電界効果トランジスタを含む半導体装置のオン抵抗を低減できるとともに、オフ耐圧を高く保つ。

【解決手段】電界効果トランジスタ(142)は、基板(102)表面に形成されたp型低濃度領域110と、p型低濃度領域110表面に設けられたn型ドレイン側拡散領域112およびn型ソース側拡散領域114と、素子分離絶縁膜132および素子分離絶縁膜134とを含む。ここで、素子分離絶縁膜132が素子分離絶縁膜134よりも膜厚が厚く形成され、n型ソース側拡散領域114において、n型ドレイン側拡散領域112よりも、不純物の濃度が最も高いピーク濃度部分が深い位置に形成されている。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方に保護ダイオードが配置されるためトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、素子領域の端部のセルではソースパッド部からゲートパッド部を迂回するように電流経路が形成される領域があった。

【解決手段】電極構造を2層とし、ゲートパッド部の少なくとも一部に保護ダイオードとの非重畳領域を形成する。2層目のゲート電極層は一部が1層目のゲート電極層と重畳し、これを介して保護ダイオードおよびゲート電極と接続する。非重畳領域下方にセルおよび1層目のソース電極層を配置できるので、ゲートパッド部下方の無効領域を従来と比較して大幅に低減でき、ソース電極層内を基板の水平方向に流れる電流について、全てのセルがソースパッド部から最短距離の電流経路となる。

(もっと読む)

半導体電子デバイスおよび半導体電子デバイスの製造方法

【課題】耐圧性が高く反りが小さくオン抵抗が低い半導体電子デバイスおよびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された、該基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、前記バッファ層上に形成された、窒化物系化合物半導体からなる半導体動作層と、窒化物系化合物半導体からなり、前記バッファ層直下から前記電子走行層内部までのいずれかの位置に形成され、凹凸形状の境界面を有する下層領域と上層領域とを有し、該下層領域から該上層領域へ延伸する貫通転位が該境界面において屈曲している転位低減層と、を備える。

(もっと読む)

絶縁ゲート型半導体装置

【課題】絶縁ゲート型半導体装置において、ゲートパッド部の下方に保護ダイオードが配置されるためトランジスタセルが配置できず、チップ上の無効領域となっていた。またソース電極層はゲートパッド部を除いて配置され、素子領域の端部のセルではソースパッド部からゲートパッド部を迂回するように電流経路が形成される領域があった。

【解決手段】電極構造を2層とし、ゲートパッド部の少なくとも一部に保護ダイオードとの非重畳領域を形成する。非重畳領域下方にセルおよび1層目のソース電極層を配置でき、ソース電極層内の抵抗の偏りを小さくできる。更に、ゲートパッド部から保護ダイオードまでの距離が、ソースパッド部から保護ダイオードまでの距離より小さくなる位置に保護ダイオードを配置する。これにより効率的にトランジスタ動作を行える素子領域を大きく確保でき、且つ配線部下方の第1ソース電極層抵抗を低減できる。

(もっと読む)

半導体装置

【課題】ノーマリーオフ動作を実現でき且つ低オン抵抗な絶縁ゲート構造の半導体装置を提供する。

【解決手段】本発明の半導体装置は、第1の窒化物半導体を含む第1の半導体層1と、第1の半導体層1上に設けられ第1の窒化物半導体よりもバンドギャップが広い第2の窒化物半導体を含む第2の半導体層2と、第2の半導体層2に接続された第1の主電極3と、第2の半導体層2に接続された第2の主電極4と、第1の主電極3と第2の主電極4との間の第2の半導体層2表面に接して設けられたフローティング電極5と、フローティング電極5上に設けられたゲート絶縁膜7と、ゲート絶縁膜7上に設けられた制御電極8と、フローティング電極5と第1の主電極3との間およびフローティング電極5と第2の主電極4との間の第2の半導体層2表面上に設けられたフィールド絶縁膜6とを備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】高駆動能力をもった厚いゲート膜を有する高耐圧MOSトランジスタを有する半導体装置を提供する。

【解決手段】高耐圧を有するLOCOSオフセットMOS型トランジスタにおいて、第2導電型高濃度ソース領域4と第2導電型高濃度ドレイン領域5を形成する際に、ポリシリコンゲート電極をマスクにしてゲート酸化膜を除去しても、チャネル形成領域7上のゲート酸化膜6はエッチングされないように、ソース側にもソースフィールド酸化膜14を設け、第2導電型高濃度ソースフィールド領域13の距離を最適化したことで、高駆動能力をもった厚いゲート膜を有する高耐圧MOSトランジスタを得ることが出来る。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生抵抗の低減に対して有利な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板11と、前記半導体基板上にゲート絶縁膜12を介して設けられるゲート電極13と、前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるエクステンション領域LDDと、前記エクステンション領域の両側を挟むように前記半導体基板中に設けられ、前記半導体基板とは異なる格子定数有し、前記半導体基板に歪みを付与する歪み付与層22と、前記エクステンション領域の両側の前記半導体基板中に前記ゲート電極を挟むように隔離して設けられるソース/ドレインS/Dと、前記ソース/ドレイン上に設けられるシリサイド層SS/Dとを具備し、前記歪み付与層と前記半導体基板との界面Si-Siは、少なくとも前記シリサイド層の底面の一部に一致する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、基板上に形成されたi型または所定の導電型を有する半導体層と、エピタキシャル成長によって半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によってドレイン電極側のコンタクト層と半導体層との間にゲート電極と重畳するように形成された、所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、エピタキシャル成長によって半導体層上の電界緩和層に隣接する領域に形成された、i型または所定の導電型を有する媒介層と、媒介層上に形成したゲート絶縁膜と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】簡易な手順で、位置あわせ精度の高い横型電界効果トランジスタを含む半導体装置を得る。

【解決手段】高耐圧トランジスタ128は、チャネル領域170上に形成されたゲート電極110と、チャネル領域170の両側方にそれぞれ形成された第1導電型のソース領域116aおよびドレイン領域116bと、ソース領域116aとドレイン領域116bとの間に設けられ、ゲート電極110のゲート幅方向に沿って、第1導電型の不純物拡散領域と第2導電型の不純物拡散領域とがそれぞれ一定幅で交互に配置された超接合構造のドリフト領域172と、を含む。ゲート電極110は、平面視で、ドリフト領域172の第2導電型の不純物拡散領域上を覆う櫛歯を有する櫛形構造に形成された構成を有する。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化物系化合物半導体からなる電界効果トランジスタであって、基板上に形成された所定の導電型を有する半導体層と、エピタキシャル成長によって前記半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、前記所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によって前記ドレイン電極側のコンタクト層と前記半導体層との間にゲート絶縁膜を介してゲート電極と重畳するように形成された、前記所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、を備える。

(もっと読む)

絶縁ゲート型半導体装置およびその製造方法

【課題】 絶縁ゲート型半導体素子が形成されるウェル領域は拡散領域であり、その底部ほど不純物濃度が薄くなり、抵抗が増加する問題がある。このため特に、アップドレイン構造の絶縁ゲート型半導体素子ではオン抵抗が増加する問題があった。

【解決手段】 p型ウェル領域を、2つのp型不純物領域を積層することにより構成する。それぞれのp型不純物領域は、p型不純物を、異なる注入エネルギーでn型半導体層内部と表面に多段注入し、熱処理により同時に拡散してp型ウェル領域とする。これにより、表面からある程度の深さ(5μm程度)までの不純物プロファイルが略平坦なp型ウェル領域を得ることができ、その表面に形成されるチャネル層の特性変動も抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】サイズを縮小するとともに、オン抵抗を低くしながらオフ耐圧を高く保つことができる半導体装置と、その製造方法を提供する。

【解決手段】半導体基板1の領域には、ゲート電極4を挟んで一方にソース電極7およびLDD領域5bが形成され、他方にドレイン電極6およびLDD層5aが形成されている。半導体基板1の表面から所定の深さD1にわたり形成されたLDD層5aには、LDD層5aの表面を除いてLDD層5aに取り囲まれるとともに、LDD層5aの表面から深さD3にわたりp型拡散層10が形成されている。LDD層5aには、p型拡散層10の直下の領域においてLDD層5aの底からさらに深い領域に向かって突出するように深さD2にわたり突出部55が形成されている。

(もっと読む)

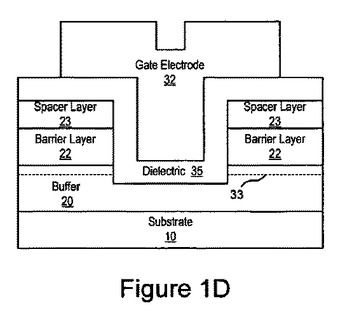

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】横型絶縁ゲートトランジスタ素子を備え、オン抵抗の増加を抑制しつつ体格を小型化することのできる半導体装置及びその製造方法を提供する。

【解決手段】半導体層に構成されたLDMOS素子と、半導体層の主表面上に形成された絶縁膜を同一表面から貫通するコンタクプラグとしての、ソース領域とベースコンタクト領域とに接続された第1コンタクトプラグと、を備えた半導体装置であって、ベースコンタクト領域が、半導体層の主表面に略垂直な方向においてソース領域よりも主表面に対して下方で、半導体層の主表面に沿う方向においてソース領域と少なくとも一部が重なる位置に形成されている。そして、第1コンタクトプラグが、絶縁膜及びソース領域を貫通しつつベースコンタクト領域まで延設されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】横型二重拡散MOSトランジスタのオン抵抗を上昇させることなく、オン状態でのソース-ドレイン領域間の耐圧を向上できる半導体装置および半導体装置の製造方法を提供する。

【解決手段】p型半導体基板上7に形成された横型二重拡散MOSトランジスタを構成において、ソース領域となる高濃度n型拡散層9に接するように、低濃度p型ウエル層11の電極となる高濃度p型拡散層10を形成する。上記高濃度p型拡散層10は、ソースコンタクト部4sの内側に位置する基部10a(十字形の交差部分)と、上記基部10aからソースコンタクト部4sの外側に延びた複数の延伸部10bとを有する。

(もっと読む)

半導体装置

【課題】 一対の主電極の間に設けられたゲート電極を有する半導体装置において、高い耐圧を確保しながらオン抵抗を低くする技術を提供する。

【解決手段】 半導体装置100は、一対の主電極2,22間に設けられたゲート電極10を備えている。ゲート部10は絶縁ゲート電極部10aとショットキー電極部10bを有している。半導体装置100は、主電極2に接続するコンタクト領域18と、コンタクト領域18に隣接するチャネル半導体領域8と、チャネル半導体領域8の裏面に接しているp型半導体領域20と、チャネル半導体領域8とp型半導体領域20の両者に隣接するドリフト半導体領域12を備えている。絶縁ゲート電極部10aは、ゲート絶縁膜4を介してコンタクト領域18の表面に対向している。ショットキー電極部10bは、ドリフト半導体領域12の表面に直接的に接触している。

(もっと読む)

半導体装置およびその製造方法

【課題】 高OFF耐圧および低ON抵抗を実現し、かつ小形化が可能な半導体装置およびその製造方法を提供する。

【解決手段】 ゲート電極4Aをドレイン側N-拡散層2b上まで設けることによって、ゲート電極4Aに電圧が印加されるON状態において、ドレイン側N-拡散層2bにキャリアを誘起することができるので、前提技術に比べて、ON抵抗を低下させることができる。これによって、第1ゲート絶縁膜6A上の部分と、ドレインN+拡散層5との離隔距離であるドレインオフセット長DL2を小さくすることなく、ON抵抗を低下させることができる。したがって、ドレインオフセット長DL2を前提技術のドレインオフセット長DL1と同程度に維持することができるので、ゲート電極4Aに電圧が印加されないOFF状態では、前提技術とほぼ同じOFF耐圧を得ることができる。

(もっと読む)

双方向スイッチ、及び半導体装置

【課題】オン抵抗を低減することのできる安定したスレッショールド電圧の双方向スイッチ、及び半導体装置を提供すること

【解決手段】本発明にかかる双方向スイッチは、P半導体基板1上に形成され、第1及び第2MOSスイッチM1、M2のドレインとなるNウェル領域2と、Nウェル領域2に設けられた第1トレンチ3内にゲート絶縁膜6を介して形成された第1ゲート電極71aと、Nウェル領域2に第1トレンチ3と離間して設けられた第2トレンチ3内にゲート絶縁膜6を介して形成された第2ゲート電極72aと、第1トレンチ3の側壁においてNウェル領域2の表面にPオフセット領域5を介して形成された第1N+ソース領域9と、第2トレンチ3の側壁においてNウェル領域2の表面にPオフセット領域5を介して形成された第2N+ソース領域10と、を備え、第1トレンチ3と第2トレンチ3との間の領域には、Nウェル領域2が形成されているものである。

(もっと読む)

161 - 180 / 457

[ Back to top ]