半導体電子デバイスおよび半導体電子デバイスの製造方法

【課題】耐圧性が高く反りが小さくオン抵抗が低い半導体電子デバイスおよびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された、該基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、前記バッファ層上に形成された、窒化物系化合物半導体からなる半導体動作層と、窒化物系化合物半導体からなり、前記バッファ層直下から前記電子走行層内部までのいずれかの位置に形成され、凹凸形状の境界面を有する下層領域と上層領域とを有し、該下層領域から該上層領域へ延伸する貫通転位が該境界面において屈曲している転位低減層と、を備える。

【解決手段】基板と、前記基板上に形成された、該基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、前記バッファ層上に形成された、窒化物系化合物半導体からなる半導体動作層と、窒化物系化合物半導体からなり、前記バッファ層直下から前記電子走行層内部までのいずれかの位置に形成され、凹凸形状の境界面を有する下層領域と上層領域とを有し、該下層領域から該上層領域へ延伸する貫通転位が該境界面において屈曲している転位低減層と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、窒化物系化合物半導体を用いた半導体電子デバイスおよび半導体電子デバイスの製造方法に関するものである。

【背景技術】

【0002】

化学式AlxInyGa1-x-yAsuPvN1-u-v(ただし、0≦x≦1、0≦y≦1、x+y≦1、0≦u≦1、0≦v≦1、u+v<1)で表される窒化物系化合物半導体、たとえばGaN系化合物半導体を用いた電界効果トランジスタ等の電子デバイスは、400℃近い高温環境下においても動作する固体デバイスとして注目されている。GaN系化合物半導体は、SiやGaAsとは異なり、大口径の単結晶基板を作製することが困難である。そのため、GaN系化合物半導体を用いた電子デバイスは、たとえばシリコンカーバイト(SiC)、サファイア、酸化亜鉛(ZnO)またはシリコン(Si)からなる基板を用いて作製されている。特に、Siからなる基板は大口径のものが安価で入手できるため、電子デバイス用の基板としては非常に有効である。

【0003】

しかしながら、SiとGaNとでは格子定数および熱膨張率に非常に大きな差があるため、Si基板上にGaN層を直接エピタキシャル成長させると、GaN層に大きな引っ張り歪みが内在することとなり、GaN層をエピタキシャル成長させたエピタキシャル基板全体に凹形状の反りが発生したり結晶性が悪化したりする原因となる。さらに、内在する歪みが大きいとGaN層にクラックが発生する。そこで、通常はSi基板とGaN層との間に歪緩和層としてのバッファ層を設ける。このようなバッファ層としてはGaN層とAlN層との積層構造が効果的である(特許文献1、2参照)。

【0004】

特許文献1に記載のGaN系電界効果トランジスタの作製方法については、たとえば直径4インチ(101.6mm)のSi単結晶からなる基板上に、MOCVD法などのエピタキシャル結晶成長法で、まず1000〜1100℃程度の基板温度でAlN層を形成し、ついで同程度の温度でGaN層とAlN層とが積層された複合層を形成してバッファ層とする。その後、バッファ層上に電子走行層、電子供給層およびコンタクト層を順次積層して半導体動作層を形成し、さらにソース電極、ドレイン電極およびゲート電極を形成した後に、各デバイスに分離する。このように、GaN層とAlN層との複合層を形成してバッファ層とすることにより、クラックがなく結晶性が良好なGaN層をSi基板上にエピタキシャル成長させることができる。さらに、エピタキシャル基板全体の反りも改善される。なお、バッファ層はGaN層とAlN層との複合層にかぎらず、互いに組成の異なるAlGaN層の複合層としても、両者に適切な量の歪みがあれば同様な効果を得られる。

【0005】

【特許文献1】特開2003−59948号公報

【特許文献2】特開2007−88426号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

ところで、GaN系化合物半導体のエピタキシャル層を有する電子デバイスを利用して電源デバイスを実現するためには、電子デバイスのオン抵抗の低抵抗化が重要である。

【0007】

半導体結晶中に転位が存在すると、電子移動度が低下するため、オン抵抗の低減のためには、特に半導体動作層において転位密度をできるだけ低減する必要がある。ここで、基板とエピタキシャル層との間の歪みにより基板近傍で発生し、上方に向かって延伸する貫通転位は、上記のような複合層を有するバッファ層の内部で消滅して低減されるものの、半導体動作層まで延伸するものも存在する。したがって、電子デバイスのオン抵抗をさらに低減するために、半導体動作層における転位密度をさらに低減する技術が求められていた。

【0008】

本発明は、上記に鑑みてなされたものであって、反りが小さくオン抵抗が低い半導体電子デバイスを提供することを目的とする。

【課題を解決するための手段】

【0009】

上述した課題を解決し、目的を達成するために、本発明に係る半導体電子デバイスは、基板と、前記基板上に形成された、該基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、前記バッファ層上に形成された窒化物系化合物半導体からなる半導体動作層と、窒化物系化合物半導体からなり、前記バッファ層直下から前記半導体動作層内部までのいずれかの位置に形成され、凹凸形状の境界面を有する下層領域と上層領域とを有し、該下層領域から該上層領域へ延伸する貫通転位が該境界面において屈曲している転位低減層と、を備えたことを特徴とする。

【0010】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、該転位低減層と前記基板との間に前記第一半導体層および/または前記第二半導体層が少なくとも1つ介在する位置に形成されることを特徴とする。

【0011】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記半導体動作層の直下に形成されることを特徴とする。

【0012】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記半導体動作層の内部に形成されることを特徴とする。

【0013】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなることを特徴とする。

【0014】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、層厚が100nm以上、3000nm以下であることを特徴とする。

【0015】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記下層領域の底部に窒化シリコンまたは酸化シリコンからなる島状の成長核を有することを特徴とする。

【0016】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記基板は、シリコン、シリコンカーバイト、および酸化亜鉛のいずれかからなることを特徴とする。

【0017】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記下層領域よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる少なくとも一つの反り低減層を有していることを特徴とする。

【0018】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記基板の直上に形成された、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層をさらに備えたことを特徴とする。

【0019】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記バッファ層は、前記各第一半導体層の層厚が積層方向に向かって増加するように形成されていることを特徴とする。

【0020】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記第一半導体層は、層厚が200nm以上、3000nm以下であることを特徴とする。

【0021】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記第二半導体層は、層厚が0.5nm以上、200nm以下であることを特徴とする。

【0022】

また、本発明に係る半導体電子デバイスの製造方法は、基板上に、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層を形成するバッファ層形成工程と、前記バッファ層上に窒化物系化合物半導体からなる半導体動作層を形成する半導体動作層形成工程と、を含み、前記バッファ層形成工程または前記半導体動作層形成工程は、前記バッファ層直下から前記半導体動作層内部までのいずれかの位置に、窒化物系化合物半導体からなり、最表面が凹凸形状を有する下層領域を形成し、該形成した下層領域上に最表面が平滑な上層領域を形成する転位低減層形成工程をさらに含むことを特徴とする。

【0023】

また、本発明に係る半導体電子デバイスの製造方法は、上記の発明において、前記転位低減層形成工程において、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる島状の成長核を形成し、該形成した成長核を覆うように前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる下層領域を形成することを特徴とする。

【0024】

また、本発明に係る半導体電子デバイスの製造方法は、上記の発明において、前記成長核を400℃以上、600℃以下の基板温度で形成することを特徴とする。

【0025】

また、本発明に係る半導体電子デバイスの製造方法は、上記の発明において、前記転位低減層形成工程において、窒化シリコンまたは酸化シリコンからなる島状の成長核を形成し、該形成した成長核を覆うように前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる下層領域を形成することを特徴とする。

【0026】

また、本発明に係る半導体電子デバイスの製造方法は、上記の発明において、前記基板の直上に、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層を形成する介在層形成工程をさらに含むことを特徴とする。

【発明の効果】

【0027】

本発明によれば、バッファ層により反りを抑制でき、さらには転位低減層によって半導体動作層における貫通転位密度を低減できるので、反りが小さくオン抵抗が低い半導体電子デバイスを実現できるという効果を奏する。

【発明を実施するための最良の形態】

【0028】

以下に、図面を参照して本発明に係る半導体電子デバイスの実施の形態を詳細に説明する。なお、この実施の形態によりこの発明が限定されるものではない。なお、各図面において、同一の構成要素には同一の符号を付している。

【0029】

(実施の形態1)

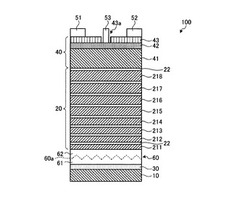

図1は、本発明の実施の形態1に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ100は、高電子移動度トランジスタ(HEMT)であって、主表面が(111)面のSi単結晶からなる基板10と、基板10上に形成された介在層30と、介在層30上に形成されたバッファ層20と、バッファ層20上に形成された半導体動作層40と、半導体動作層40上に形成されたソース電極51とドレイン電極52とゲート電極53とを備え、さらにバッファ層20直下の位置に形成された転位低減層60を備えている。なお、この電界効果トランジスタ100の構造は、転位低減層60を備える点以外は、本発明者らによる特願2008−140649に係る明細書に実施の形態1として記載された電界効果トランジスタとほぼ同様の構造を有する。

【0030】

すなわち、介在層30は、アンドープのAlNからなる。半導体動作層40は、アンドープのGaNからなる電子走行層41と、Siドープのn型AlGaNからなる電子供給層42と、n+型のGaNからなるコンタクト層43とが順次積層したものである。また、ソース電極51とドレイン電極52とはいずれもTi/Alの積層構造を有し、コンタクト層43上に形成されている。また、ゲート電極53は、Pt/Auの積層構造を有し、コンタクト層43に形成された開口部43aを介して電子供給層42上に形成されている。

【0031】

また、バッファ層20は、アンドープのGaNからなる第一半導体層211、・・・、218と、アンドープのAlNからなる第二半導体層22、・・・、22とが交互に積層している。隣接する第一半導体層と第二半導体層との組を複合層とすると、バッファ層20は複合層を8層有している。なお、GaNからなる第一半導体層211をSiからなる基板10上に直接形成すると、GaとSiが合金を形成してしまうが、介在層30の存在により合金形成が防止されている。

【0032】

一方、転位低減層60は、全体がアンドープのGaNからなる。また、この転位低減層60は、凹凸形状の境界面60aを有する下層領域61と上層領域62とを有している。

【0033】

Siからなる基板10は、格子定数が0.384nmであり、熱膨張係数が3.59×10−6/Kである。一方、GaNからなる第一半導体層211、・・・、218および転位低減層60は、格子定数が0.3189nmであって基板10よりも小さく、膨張係数が5.59×10−6/Kであって基板10よりも大きい。一方、AlNからなる介在層30および第二半導体層22、・・・、22は、格子定数が0.3112nmであって第一半導体層211、・・・、218よりも小さく、熱膨張係数が4.2×10−6/Kであって基板10よりも大きい。

【0034】

また、介在層30の層厚はたとえば40nmである。また、第一半導体層211、・・・、218は、積層方向に向かって層厚が指数関数的に増加するように形成されている。具体的には、基板10から1層目である第一半導体層211は層厚が300nmであり、積層方向に向かって層厚が厚くなり、第一半導体層212〜218は層厚がそれぞれ約352.7nm、422.8nm、520.1nm、663.2nm、891.9nm、1306nm、2237nmになっている。一方、第二半導体層22、・・・、22は、層厚がいずれも同一の60nmである。したがって、バッファ層20の層厚は、7.18μmとなる。また、転位低減層60の厚さは1500nm、半導体動作層40の層厚は1.35μmであり、バッファ層20と合わせたエピタキシャル層の総層厚は10.05μmである。

【0035】

この電界効果トランジスタ100は、上述したように、たとえば直径4インチの基板10上に、MOCVD法などのエピタキシャル結晶成長法で、介在層30、転位低減層60、バッファ層20、半導体動作層40を順次形成し、さらにソース電極51、ドレイン電極52およびゲート電極53を形成した後に、各デバイスに分離して作製される。

【0036】

ここで、この電界効果トランジスタ100は、上記構成を備えることによって、反りが小さく、オン抵抗が低いデバイスとなっている。

【0037】

以下、具体的に説明する。なお、以下では、はじめにこの電界効果トランジスタ100のオン抵抗が低くなることについて説明し、つぎに反りが小さくなることについて説明する。

【0038】

はじめに、この電界効果トランジスタ100のオン抵抗が低くなることについて説明する。この電界効果トランジスタ100は、転位低減層60によって電子走行層41における貫通転位密度が低減されることによって、オン抵抗が低くなっている。

【0039】

図2は、転位低減層60の作用について説明する説明図である。図2に示すように、基板10近傍において発生した貫通転位D1、D2は、転位低減層60の下層領域61を積層方向に向かって延びるが、凹凸形状の境界面60aの傾斜面において屈曲し、上層領域62をさらに延びていき、転位低減層60の直上に位置するバッファ層20へと延びる。

【0040】

ここで、貫通転位D3、D4を、互いに逆向きのバーガースベクトルを有する貫通転位とする。これらの貫通転位D3、D4も、下層領域61を上方に向かって延び、境界面60aの傾斜面において屈曲するが、上層領域62内の点P1において出会う。これらの貫通転位D3、D4は、互いに逆向きのバーガースベクトルを有するため、点P1において消滅しバッファ層20までは到達しない。または、点P1で消滅しなくとも、そこでバーガースベクトルの大きさは小さくなるので、さらにその上方に延びる途中で消滅しやすくなる。

【0041】

すなわち、この転位低減層60は、凹凸形状の境界面60aによって貫通転位を屈曲させ、貫通転位同士が出会う確率を高めることによって、互いに逆向きのバーガースベクトルを有する貫通転位同士の打ち消しあいによる消滅、またはその大きさの低減の確率を高めている。その結果、バッファ層20に到達し、さらには半導体動作層40にまで到達する貫通転位が低減され、半導体動作層40、特に電子走行層41における貫通転位密度が低減される。その結果、この電界効果トランジスタ100はオン抵抗が低くなる。

【0042】

この転位低減層60は、たとえば次のように形成される。図3〜6は、転位低減層60の形成方法の一例を説明する説明図である。はじめに、基板温度を400〜600℃として、図3に示すように、介在層30上にアンドープのGaNからなるアモルファス層61aを約400nm程度までの厚さで形成する。つぎに、基板温度を850〜950℃に昇温することによって、アモルファス層61aから図4に示すような島状の成長核61bを形成する。この成長核61bは介在層30の表面に対して傾斜した複数のファセット面を有する島状構造を有する。次に、成長核61bを覆うようにアンドープのGaNからなる下層領域61を約1000nm程度までの厚さで形成する。この下層領域61の最表面は、成長核61bの形状を反映して凹凸形状を有するようになる。つぎに、図6に示すように、基板温度を950〜1050℃に昇温し、下層領域61上にアンドープのGaNからなる上層領域62を形成し、転位低減層60とする。この上層領域62の形成は横方向への結晶成長を促すような条件でおこわなれるため、上層領域62の最表面は平滑になる。この際、貫通転位は成長面に対して垂直に延伸するため、貫通転位D5、D6は下層領域61の最表面、すなわち境界面60aにおいて曲げられる。ここで、貫通転位D5、D6は互いに逆向きのバーガースベクトルを有するものであり、これらが点P2で出会うことで消滅する。

【0043】

なお、下層領域61と上層領域62とは同じ組成を有する半導体材料からなり、その境界面60aにおいても結晶構造等が連続している。しかしながら、たとえばこの転位低減層60の断面を電子顕微鏡等で観察すると、多くの貫通転位が屈曲している境界面が存在する様子が観察されるので、境界面60aの位置および形状は容易に特定できる。

【0044】

つぎに、この電界効果トランジスタ100の耐圧性が高く、反りが小さくなることについて説明する。なお、以下では、基板10が凸状に反る場合をプラスの方向に反るとし、凹状に反る場合をマイナスの方向に反ると規定する。

【0045】

この電界効果トランジスタ100の製造の際には、介在層30、バッファ層20、半導体動作層40は1000〜1100℃程度の基板温度で形成される。ここで、基板10上に介在層30を形成すると、介在層30は基板10よりも格子定数が小さいので、反りはマイナスの方向に発生する。つぎに、介在層30上に転位低減層60を介して第1層目の第一半導体層211を形成すると、第一半導体層211は介在層30よりも格子定数が大きいので、第一半導体層211の層厚が薄いうちは反りがプラスの方向に発生する。しかし、第一半導体層211の層厚がある厚さ以上となると、第一半導体層211が基板10よりも格子定数が小さいことによって、プラスの方向の反りを打ち消すように反りがマイナスの方向に発生するようになる。以下では、半導体層がエピタキシャル基板に対して発生させる反りの方向が反転する際の、その半導体層の層厚を臨界厚さと呼ぶ。すなわち、臨界厚さとは、半導体層の層厚の変化に対して反りが極大点となる層厚を意味する。

【0046】

つぎに、第一半導体層211上に第二半導体層22を形成すると、第二半導体層22は第一半導体層211よりも格子定数が小さいので、反りはマイナスの方向に発生する。

【0047】

つぎに、第二半導体層22上に第一半導体層212を形成すると、第一半導体層211の場合と同様に、第一半導体層212の層厚が薄いうちは反りがプラスの方向に発生し、ある臨界厚さ以上となると、反りがマイナスの方向に発生するようになる。しかしながら、第一半導体層212の臨界厚さは、第一半導体層211の臨界厚さよりも厚くなる。この理由は、第一半導体層212の場合は、その下方に形成されている介在層30、転位低減層60、第一半導体層211、第二半導体層22の各半導体層(下地層)の影響を受けるためであると考えられる。

【0048】

ここで、第一半導体層212の層厚と第一半導体層211の層厚が同じ場合は、第一半導体層212において発生するマイナスの方向への反りは小さくなる。しかしながら、本実施の形態1では、上述したように、第一半導体層212は、第一半導体層211よりも厚く形成されている。その結果、第一半導体層212の臨界厚さが第一半導体層211の臨界厚さよりも厚くなっても、第一半導体層212においてマイナスの方向に発生する反りは大きく維持される。

【0049】

同様に、第二半導体層22を挟んで第一半導体層213、214、・・・と形成していくにしたがって、下地層の総層厚が厚くなるので、臨界厚さは厚くなっていく。これに対して、この電界効果トランジスタ100においては、第一半導体層213、214、・・・、218は、積層方向に向かって層厚が増加し、かつ各第一半導体層213、214、・・・、218の層厚は、その積層位置における臨界厚さよりも厚く形成されている。その結果、各第一半導体層211、・・・、218においてマイナスの方向に発生する反りが大きく維持されるため、プラスの方向に発生する反りは打ち消され、きわめて小さくなる。

【0050】

最後に、半導体動作層40を形成し、エピタキシャル成長を終了するが、半導体動作層40においても反りはトータルとしてプラスの方向に発生する。その後、基板温度を1000〜1100℃から常温に戻すが、バッファ層20、転位低減層60、介在層30、半導体動作層40のいずれも、基板10よりも熱膨張係数が大きいので、基板温度の低下につれて反りがマイナスの方向に発生し、最終的な反り量は小さい値となる。さらには、これによって反りを抑制しながらエピタキシャル層の総層厚を厚くできるので、耐圧性を高くできる。

【0051】

以上説明したように、この電界効果トランジスタ100は、反りが小さいと同時に、基板10上のエピタキシャル層の総層厚が厚いため耐圧性が高いものとなる。さらに、各第一半導体層211、・・・、218において反りが打ち消しあっているため、内在する歪みがきわめて低減されるという効果も奏する。

【0052】

なお、本実施の形態1において、最も薄い第一半導体層211の層厚は300nmであるが、200nm以上であればマイナスの方向の反りを発生させることができる。また、400nm以上であれば、発生するマイナスの方向の反りの量を十分に大きくすることができるのでさらに好ましい。また、各第一半導体層211、・・・、218の層厚が3000nm以下であれば、成長時間が十分に短いので、生産性が高く好ましい。

【0053】

また、第二半導体層22の層厚は、0.5nm以上200nm以下であれば、第一半導体層211、・・・、218に内在する歪みを十分に抑制できるので好ましい。

【0054】

また、第一半導体層211、・・・、218、第二半導体層22、・・・、22、介在層30の層厚は、上記実施の形態1の値に限られず、これらの組成、基板10との格子定数および熱膨張率差、デバイスに要求される耐圧、許容される反り量などに応じて適宜設定することができる。

【0055】

また、転位低減層60の層厚は、十分な転位低減効果を得るために充分に凹凸形状を形成し、かつ、平坦化させるためには100nm以上が好ましく、生産性を高めるには3000nm以下であることが好ましい。

【0056】

(変形例1〜4)

上記実施の形態1に係る電界効果トランジスタ100では、転位低減層60がバッファ層20直下の位置に形成されているが、転位低減層60の位置はこれに限定されず、バッファ層20直下から電子走行層41内部までのいずれかの位置に形成されていれば、その転位低減の効果を発揮することができる。以下、実施の形態1の変形例1〜4として、転位低減層60を様々な位置に形成した半導体電子デバイスについて説明する。

【0057】

(変形例1)

図7は、変形例1に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ200は、図1に示す電界効果トランジスタ100においてバッファ層20をバッファ層201に置き換えた構造を有している。このバッファ層201は、バッファ層20と同様の構成の第一半導体層211、・・・、218と第二半導体層22、・・・、22とが交互に積層した構造を有しているが、凹凸形状の境界面60aを有する転位低減層60が、バッファ層201内の第一半導体層216の直下の位置に形成されている。その結果、この電界効果トランジスタ200も、電界効果トランジスタ100と同様の作用により、反りが小さく、オン抵抗が低く、さらには耐圧性が高いデバイスとなる。また、この電界効果トランジスタ200は、転位低減層60が、基板10との間に少なくとも1つの第一半導体層が介在する位置に形成されている。このような構成の場合、基板10近傍で発生した貫通転位が、この少なくとも1つの第一半導体層内で一旦減少するため、転位低減層60において貫通転位をより消滅させ易くなるので、よりオン抵抗が低くなり好ましい。なお、さらなる変形例として、転位低減層60が、転位低減層60と基板10との間に第一半導体層および/または第二半導体層が少なくとも1つ介在する位置に形成されるような構成にすれば、変形例1と同様の効果を奏する電界効果トランジスタとなる。

【0058】

(変形例2)

図8は、変形例2に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ300は、図1に示す電界効果トランジスタ100においてバッファ層20をバッファ層202に置き換えた構造を有している。このバッファ層202は、バッファ層20と同様の構造を有しているが、バッファ層20の第一半導体層216に対応するものが第一半導体層216aと第一半導体層216bに分離しており、凹凸形状の境界面60aを有する転位低減層60がこの第一半導体層216aと第一半導体層216bとの間の位置に形成されている。その結果、この電界効果トランジスタ300も、電界効果トランジスタ100、200と同様の作用により、反りが小さく、オン抵抗が低く、さらには耐圧性が高いデバイスとなる。また、この電界効果トランジスタ300も、転位低減層60が、基板10との間に少なくとも1つの第一半導体層が介在する位置に形成されているので、転位低減層60において貫通転位をより消滅させ易くなるので、よりオン抵抗が低くなり好ましい。

【0059】

(変形例3)

図9は、変形例3に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ400は、図1に示す電界効果トランジスタ100において、転位低減層60を半導体動作層40の直下に形成した構成を有する。その結果、この電界効果トランジスタ400も、反りが小さく、耐圧性が高いとともに、転位低減層60により半導体動作層40の直前で一層効果的に貫通転移を消滅させることができるので、オン抵抗が一層低いデバイスとなる。

【0060】

(変形例4)

図10は、変形例4に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ500は、図1に示す電界効果トランジスタ100において半導体動作層40を半導体動作層401に置き換えた構造を有している。この半導体動作層401は、半導体動作層40と同様の構造を有しているが、半導体動作層40の電子走行層41に対応するものが電子走行層41aと電子走行層41bに分離している。そして、凹凸形状の境界面60aを有する転位低減層60が、半導体動作層401の内部である電子走行層41aと電子走行層41bとの間の位置に形成されている。なお、実際に電子が走行するのは電子走行層41bであるが、その層厚は電子の走行に影響を及ぼさないような層厚とされている。その結果、この電界効果トランジスタ500も、反りが小さく、耐圧性が高いとともに、転位低減層60により電子走行層41bの直前で一層効果的に貫通転移を消滅させることができるので、さらにオン抵抗が低いデバイスとなる。

【0061】

(実施例1〜3、比較例1)

つぎに、本発明の実施例1〜3として、実施の形態1、およびその変形例1、3に従う電界効果トランジスタを作製し、その積層方向の位置における転位密度を透過型電子顕微鏡(TEM)により測定した。一方、比較例1として、実施の形態1の構造において転位低減層の代わりに、均一に成長させたアンドープのGaN層を転位低減層と同じ1500nmの層厚で形成した電界効果トランジスタを作製し、その積層方向の位置における転位密度をTEMにより測定した。

【0062】

図11は、実施例1〜3、比較例1の電界効果トランジスタにおける、基板表面から測定した厚さの位置における螺旋転位の転位密度を示した図である。また、図12は、実施例1〜3、比較例1の電界効果トランジスタにおける、基板表面から測定した厚さの位置における刃状転位の転位密度を示した図である。図11、12に示すように、比較例1については、厚さが1μm程度に薄く基板に近い位置では各転位密度が大きく、厚さが厚くなるに従い各転位密度が減少している。また、実施例1においては、基板に近い位置に転位低減層を形成しているので、厚さが1μm程度において各転位密度は大幅に減少しており、厚さが厚くなっても低密度になっている。また、実施例2においては、厚さが1μm程度の位置では比較例1と同様に各転位密度が大きいが、転位低減層より上の位置の厚さで各転位密度が大きく減少しており、厚さが厚くなっても低密度になっている。また、実施例3においては、バッファ層に対応する位置の厚さまでは比較例1と同様の傾向を示しているが、転位低減層より上の位置の厚さで各転位密度が大きく減少しており、半導体動作層の位置の厚さで各転位密度がきわめて低くなっている。

【0063】

また、図13は、実施例1〜3、比較例1について、半導体動作層中である厚さが9.5μmの位置における螺旋転位および刃状転位の転位密度を示した図である。図13に示すように、実施例1〜3では、比較例1よりも各転位密度が低く、特に転位低減層の位置が半導体動作層に近くなるにつれて各転位密度がより低くなることが確認された。

【0064】

(実施の形態2)

つぎに、本発明の実施の形態2について説明する。図14は、本実施の形態2に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ600は、図1に示す電界効果トランジスタ100において、転位低減層60を転位低減層70に置き換えた構造を有している。この転位低減層70は、下層領域71と、反り低減層72と、第一上層領域73と、反り低減層74と、第二上層領域75とが順次積層した構造を有する。下層領域71、第一上層領域73、第二上層領域75はそれぞれアンドープのGaNからなる。また、反り低減層72、74は、それぞれアンドープのAlNからなる。

【0065】

この電界効果トランジスタ600の転位低減層70においては、下層領域71と、それよりも上部の領域である反り低減層72から第二上層領域75との間の境界面70aが凹凸状を有しているので、下方から延びてきた貫通転位が境界面70aの傾斜面において屈曲するため、電界効果トランジスタ100と同様に電子走行層41における貫通転位密度が低減され、オン抵抗が低くなる。

【0066】

また、このように、この転位低減層70は、GaNからなる下層領域71、第一上層領域73、第二上層領域75と、AlNからなる反り低減層72、74とが交互に積層しているので、バッファ層20と同様の作用により、転位低減層70の層厚が厚くなってもその反りは抑制される。なお、このような反り低減層の数は2つに限らず、1つまたは複数であればよい。

【0067】

また、この転位低減層70は、電界効果トランジスタ100における転位低減層60と同様の方法を用いて、適宜成長材料を変更して形成することができる。なお、反り低減層72から第二上層領域75については、横方向への結晶成長を促すような条件で形成するので、境界面70c、70dの凹凸形状は、境界面70a、70bの凹凸形状よりも傾斜が緩やかになっている。

【0068】

(実施の形態3)

つぎに、本発明の実施の形態3について説明する。図15は、本実施の形態3に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ700は、図1に示す電界効果トランジスタ100において、転位低減層60を転位低減層80に置き換えた構造を有している。この転位低減層80は、凹凸形状の境界面80aを有する下層領域81と上層領域82とを有する。下層領域81は、窒化シリコンまたは酸化シリコンからなる5nm程度までの厚さの島状の成長核81aを底部に有し、この成長核81aを覆うように形成されたアンドープのGaNからなる。また、上層領域82はアンドープのGaNからなる。

【0069】

この電界効果トランジスタ700の転位低減層80においては、境界面80aの凹凸形状が窒化シリコンまたは酸化シリコンからなる島状の成長核81aにより形成されている。窒化シリコンまたは酸化シリコンは、その成長の初期において島状の成長核81aを形成しやすいので、この電界効果トランジスタ700は、反りが小さくオン抵抗が低く耐圧性が高く、かつ製造性が高いものとなる。なお、この島状の成長核81aは、たとえば各種CVD法等の気相成長法を用いて形成できる。

【0070】

なお、上記各実施の形態においては、Siからなる基板を用いたが、SiC、ZnOからなる基板を用いてもよい。また、転位低減層の各領域または反り低減層、介在層、第一および第二半導体層の材質についても、窒化物系化合物半導体であり、格子定数および熱膨張率が基板も含めて所定の関係を満たすものであれば特に限定されない。たとえば、上記各実施の形態において、第二半導体層はAlNからなるものであったが、AlxGa1-xN(ただし、0<x<1)であってもよい。

【0071】

また、上記各実施の形態においては、半導体電子デバイスがHEMT型の電界効果トランジスタであったが、本発明はこれに限定されず、絶縁ゲート型(MIS型、MOS型)、ショットキーゲート型(MES型)等、種々の電界効果トランジスタに対して適用可能である。また、本発明は、電界効果トランジスタ以外にも、ショットキーダイオード等、各種ダイオードに対しては適用可能である。たとえば、実施の形態1の電界効果トランジスタ100において、ソース電極51、ドレイン電極52およびゲート電極53のかわりにカソード電極およびアノード電極を形成した構造とすれば、本発明を適用したダイオードを実現できる。なお、本発明を種々の半導体電子デバイスに適用する際に、転位低減層を半導体動作層の内部に形成する場合には、図10に示す変形例4と同様に、そのデバイスの動作特性に影響を及ぼさないような位置に転位低減層を形成する。

【図面の簡単な説明】

【0072】

【図1】実施の形態1に係る電界効果トランジスタの模式的な断面図である。

【図2】転位低減層の作用について説明する説明図である。

【図3】転位低減層の形成方法の一例を説明する説明図である。

【図4】転位低減層の形成方法の一例を説明する説明図である。

【図5】転位低減層の形成方法の一例を説明する説明図である。

【図6】転位低減層の形成方法の一例を説明する説明図である。

【図7】実施の形態1の変形例1に係る電界効果トランジスタの模式的な断面図である。

【図8】実施の形態1の変形例2に係る電界効果トランジスタの模式的な断面図である。

【図9】実施の形態1の変形例3に係る電界効果トランジスタの模式的な断面図である。

【図10】実施の形態1の変形例4に係る電界効果トランジスタの模式的な断面図である。

【図11】実施例1〜3、比較例1の電界効果トランジスタにおける、基板表面から測定した厚さの位置における螺旋転位の転位密度を示した図である。

【図12】実施例1〜3、比較例1の電界効果トランジスタにおける、基板表面から測定した厚さの位置における刃状転位の転位密度を示した図である。

【図13】実施例1〜3、比較例1について、半導体動作層中である厚さが9.5μmの位置における螺旋転位および刃状転位の転位密度を示した図である。

【図14】実施の形態2に係る電界効果トランジスタの模式的な断面図である。

【図15】実施の形態3に係る電界効果トランジスタの模式的な断面図である。

【符号の説明】

【0073】

10 基板

20、201、202 バッファ層

22 第二半導体層

30 介在層

40、401 半導体動作層

41、41a、41b 電子走行層

42 電子供給層

43 コンタクト層

43a 開口部

51 ソース電極

52 ドレイン電極

53 ゲート電極

60〜80 転位低減層

60a、70a〜70d、80a 境界面

61〜81 下層領域

61a アモルファス層

61b、81a 成長核

62、82 上層領域

72、74 反り低減層

73 第一上層領域

75 第二上層領域

100〜700 電界効果トランジスタ

211〜218、216a、216b 第一半導体層

D1〜D6 貫通転位

P1、P2 点

【技術分野】

【0001】

本発明は、窒化物系化合物半導体を用いた半導体電子デバイスおよび半導体電子デバイスの製造方法に関するものである。

【背景技術】

【0002】

化学式AlxInyGa1-x-yAsuPvN1-u-v(ただし、0≦x≦1、0≦y≦1、x+y≦1、0≦u≦1、0≦v≦1、u+v<1)で表される窒化物系化合物半導体、たとえばGaN系化合物半導体を用いた電界効果トランジスタ等の電子デバイスは、400℃近い高温環境下においても動作する固体デバイスとして注目されている。GaN系化合物半導体は、SiやGaAsとは異なり、大口径の単結晶基板を作製することが困難である。そのため、GaN系化合物半導体を用いた電子デバイスは、たとえばシリコンカーバイト(SiC)、サファイア、酸化亜鉛(ZnO)またはシリコン(Si)からなる基板を用いて作製されている。特に、Siからなる基板は大口径のものが安価で入手できるため、電子デバイス用の基板としては非常に有効である。

【0003】

しかしながら、SiとGaNとでは格子定数および熱膨張率に非常に大きな差があるため、Si基板上にGaN層を直接エピタキシャル成長させると、GaN層に大きな引っ張り歪みが内在することとなり、GaN層をエピタキシャル成長させたエピタキシャル基板全体に凹形状の反りが発生したり結晶性が悪化したりする原因となる。さらに、内在する歪みが大きいとGaN層にクラックが発生する。そこで、通常はSi基板とGaN層との間に歪緩和層としてのバッファ層を設ける。このようなバッファ層としてはGaN層とAlN層との積層構造が効果的である(特許文献1、2参照)。

【0004】

特許文献1に記載のGaN系電界効果トランジスタの作製方法については、たとえば直径4インチ(101.6mm)のSi単結晶からなる基板上に、MOCVD法などのエピタキシャル結晶成長法で、まず1000〜1100℃程度の基板温度でAlN層を形成し、ついで同程度の温度でGaN層とAlN層とが積層された複合層を形成してバッファ層とする。その後、バッファ層上に電子走行層、電子供給層およびコンタクト層を順次積層して半導体動作層を形成し、さらにソース電極、ドレイン電極およびゲート電極を形成した後に、各デバイスに分離する。このように、GaN層とAlN層との複合層を形成してバッファ層とすることにより、クラックがなく結晶性が良好なGaN層をSi基板上にエピタキシャル成長させることができる。さらに、エピタキシャル基板全体の反りも改善される。なお、バッファ層はGaN層とAlN層との複合層にかぎらず、互いに組成の異なるAlGaN層の複合層としても、両者に適切な量の歪みがあれば同様な効果を得られる。

【0005】

【特許文献1】特開2003−59948号公報

【特許文献2】特開2007−88426号公報

【発明の開示】

【発明が解決しようとする課題】

【0006】

ところで、GaN系化合物半導体のエピタキシャル層を有する電子デバイスを利用して電源デバイスを実現するためには、電子デバイスのオン抵抗の低抵抗化が重要である。

【0007】

半導体結晶中に転位が存在すると、電子移動度が低下するため、オン抵抗の低減のためには、特に半導体動作層において転位密度をできるだけ低減する必要がある。ここで、基板とエピタキシャル層との間の歪みにより基板近傍で発生し、上方に向かって延伸する貫通転位は、上記のような複合層を有するバッファ層の内部で消滅して低減されるものの、半導体動作層まで延伸するものも存在する。したがって、電子デバイスのオン抵抗をさらに低減するために、半導体動作層における転位密度をさらに低減する技術が求められていた。

【0008】

本発明は、上記に鑑みてなされたものであって、反りが小さくオン抵抗が低い半導体電子デバイスを提供することを目的とする。

【課題を解決するための手段】

【0009】

上述した課題を解決し、目的を達成するために、本発明に係る半導体電子デバイスは、基板と、前記基板上に形成された、該基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、前記バッファ層上に形成された窒化物系化合物半導体からなる半導体動作層と、窒化物系化合物半導体からなり、前記バッファ層直下から前記半導体動作層内部までのいずれかの位置に形成され、凹凸形状の境界面を有する下層領域と上層領域とを有し、該下層領域から該上層領域へ延伸する貫通転位が該境界面において屈曲している転位低減層と、を備えたことを特徴とする。

【0010】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、該転位低減層と前記基板との間に前記第一半導体層および/または前記第二半導体層が少なくとも1つ介在する位置に形成されることを特徴とする。

【0011】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記半導体動作層の直下に形成されることを特徴とする。

【0012】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記半導体動作層の内部に形成されることを特徴とする。

【0013】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなることを特徴とする。

【0014】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、層厚が100nm以上、3000nm以下であることを特徴とする。

【0015】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記下層領域の底部に窒化シリコンまたは酸化シリコンからなる島状の成長核を有することを特徴とする。

【0016】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記基板は、シリコン、シリコンカーバイト、および酸化亜鉛のいずれかからなることを特徴とする。

【0017】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記転位低減層は、前記下層領域よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる少なくとも一つの反り低減層を有していることを特徴とする。

【0018】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記基板の直上に形成された、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層をさらに備えたことを特徴とする。

【0019】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記バッファ層は、前記各第一半導体層の層厚が積層方向に向かって増加するように形成されていることを特徴とする。

【0020】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記第一半導体層は、層厚が200nm以上、3000nm以下であることを特徴とする。

【0021】

また、本発明に係る半導体電子デバイスは、上記の発明において、前記第二半導体層は、層厚が0.5nm以上、200nm以下であることを特徴とする。

【0022】

また、本発明に係る半導体電子デバイスの製造方法は、基板上に、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層を形成するバッファ層形成工程と、前記バッファ層上に窒化物系化合物半導体からなる半導体動作層を形成する半導体動作層形成工程と、を含み、前記バッファ層形成工程または前記半導体動作層形成工程は、前記バッファ層直下から前記半導体動作層内部までのいずれかの位置に、窒化物系化合物半導体からなり、最表面が凹凸形状を有する下層領域を形成し、該形成した下層領域上に最表面が平滑な上層領域を形成する転位低減層形成工程をさらに含むことを特徴とする。

【0023】

また、本発明に係る半導体電子デバイスの製造方法は、上記の発明において、前記転位低減層形成工程において、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる島状の成長核を形成し、該形成した成長核を覆うように前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる下層領域を形成することを特徴とする。

【0024】

また、本発明に係る半導体電子デバイスの製造方法は、上記の発明において、前記成長核を400℃以上、600℃以下の基板温度で形成することを特徴とする。

【0025】

また、本発明に係る半導体電子デバイスの製造方法は、上記の発明において、前記転位低減層形成工程において、窒化シリコンまたは酸化シリコンからなる島状の成長核を形成し、該形成した成長核を覆うように前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる下層領域を形成することを特徴とする。

【0026】

また、本発明に係る半導体電子デバイスの製造方法は、上記の発明において、前記基板の直上に、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層を形成する介在層形成工程をさらに含むことを特徴とする。

【発明の効果】

【0027】

本発明によれば、バッファ層により反りを抑制でき、さらには転位低減層によって半導体動作層における貫通転位密度を低減できるので、反りが小さくオン抵抗が低い半導体電子デバイスを実現できるという効果を奏する。

【発明を実施するための最良の形態】

【0028】

以下に、図面を参照して本発明に係る半導体電子デバイスの実施の形態を詳細に説明する。なお、この実施の形態によりこの発明が限定されるものではない。なお、各図面において、同一の構成要素には同一の符号を付している。

【0029】

(実施の形態1)

図1は、本発明の実施の形態1に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ100は、高電子移動度トランジスタ(HEMT)であって、主表面が(111)面のSi単結晶からなる基板10と、基板10上に形成された介在層30と、介在層30上に形成されたバッファ層20と、バッファ層20上に形成された半導体動作層40と、半導体動作層40上に形成されたソース電極51とドレイン電極52とゲート電極53とを備え、さらにバッファ層20直下の位置に形成された転位低減層60を備えている。なお、この電界効果トランジスタ100の構造は、転位低減層60を備える点以外は、本発明者らによる特願2008−140649に係る明細書に実施の形態1として記載された電界効果トランジスタとほぼ同様の構造を有する。

【0030】

すなわち、介在層30は、アンドープのAlNからなる。半導体動作層40は、アンドープのGaNからなる電子走行層41と、Siドープのn型AlGaNからなる電子供給層42と、n+型のGaNからなるコンタクト層43とが順次積層したものである。また、ソース電極51とドレイン電極52とはいずれもTi/Alの積層構造を有し、コンタクト層43上に形成されている。また、ゲート電極53は、Pt/Auの積層構造を有し、コンタクト層43に形成された開口部43aを介して電子供給層42上に形成されている。

【0031】

また、バッファ層20は、アンドープのGaNからなる第一半導体層211、・・・、218と、アンドープのAlNからなる第二半導体層22、・・・、22とが交互に積層している。隣接する第一半導体層と第二半導体層との組を複合層とすると、バッファ層20は複合層を8層有している。なお、GaNからなる第一半導体層211をSiからなる基板10上に直接形成すると、GaとSiが合金を形成してしまうが、介在層30の存在により合金形成が防止されている。

【0032】

一方、転位低減層60は、全体がアンドープのGaNからなる。また、この転位低減層60は、凹凸形状の境界面60aを有する下層領域61と上層領域62とを有している。

【0033】

Siからなる基板10は、格子定数が0.384nmであり、熱膨張係数が3.59×10−6/Kである。一方、GaNからなる第一半導体層211、・・・、218および転位低減層60は、格子定数が0.3189nmであって基板10よりも小さく、膨張係数が5.59×10−6/Kであって基板10よりも大きい。一方、AlNからなる介在層30および第二半導体層22、・・・、22は、格子定数が0.3112nmであって第一半導体層211、・・・、218よりも小さく、熱膨張係数が4.2×10−6/Kであって基板10よりも大きい。

【0034】

また、介在層30の層厚はたとえば40nmである。また、第一半導体層211、・・・、218は、積層方向に向かって層厚が指数関数的に増加するように形成されている。具体的には、基板10から1層目である第一半導体層211は層厚が300nmであり、積層方向に向かって層厚が厚くなり、第一半導体層212〜218は層厚がそれぞれ約352.7nm、422.8nm、520.1nm、663.2nm、891.9nm、1306nm、2237nmになっている。一方、第二半導体層22、・・・、22は、層厚がいずれも同一の60nmである。したがって、バッファ層20の層厚は、7.18μmとなる。また、転位低減層60の厚さは1500nm、半導体動作層40の層厚は1.35μmであり、バッファ層20と合わせたエピタキシャル層の総層厚は10.05μmである。

【0035】

この電界効果トランジスタ100は、上述したように、たとえば直径4インチの基板10上に、MOCVD法などのエピタキシャル結晶成長法で、介在層30、転位低減層60、バッファ層20、半導体動作層40を順次形成し、さらにソース電極51、ドレイン電極52およびゲート電極53を形成した後に、各デバイスに分離して作製される。

【0036】

ここで、この電界効果トランジスタ100は、上記構成を備えることによって、反りが小さく、オン抵抗が低いデバイスとなっている。

【0037】

以下、具体的に説明する。なお、以下では、はじめにこの電界効果トランジスタ100のオン抵抗が低くなることについて説明し、つぎに反りが小さくなることについて説明する。

【0038】

はじめに、この電界効果トランジスタ100のオン抵抗が低くなることについて説明する。この電界効果トランジスタ100は、転位低減層60によって電子走行層41における貫通転位密度が低減されることによって、オン抵抗が低くなっている。

【0039】

図2は、転位低減層60の作用について説明する説明図である。図2に示すように、基板10近傍において発生した貫通転位D1、D2は、転位低減層60の下層領域61を積層方向に向かって延びるが、凹凸形状の境界面60aの傾斜面において屈曲し、上層領域62をさらに延びていき、転位低減層60の直上に位置するバッファ層20へと延びる。

【0040】

ここで、貫通転位D3、D4を、互いに逆向きのバーガースベクトルを有する貫通転位とする。これらの貫通転位D3、D4も、下層領域61を上方に向かって延び、境界面60aの傾斜面において屈曲するが、上層領域62内の点P1において出会う。これらの貫通転位D3、D4は、互いに逆向きのバーガースベクトルを有するため、点P1において消滅しバッファ層20までは到達しない。または、点P1で消滅しなくとも、そこでバーガースベクトルの大きさは小さくなるので、さらにその上方に延びる途中で消滅しやすくなる。

【0041】

すなわち、この転位低減層60は、凹凸形状の境界面60aによって貫通転位を屈曲させ、貫通転位同士が出会う確率を高めることによって、互いに逆向きのバーガースベクトルを有する貫通転位同士の打ち消しあいによる消滅、またはその大きさの低減の確率を高めている。その結果、バッファ層20に到達し、さらには半導体動作層40にまで到達する貫通転位が低減され、半導体動作層40、特に電子走行層41における貫通転位密度が低減される。その結果、この電界効果トランジスタ100はオン抵抗が低くなる。

【0042】

この転位低減層60は、たとえば次のように形成される。図3〜6は、転位低減層60の形成方法の一例を説明する説明図である。はじめに、基板温度を400〜600℃として、図3に示すように、介在層30上にアンドープのGaNからなるアモルファス層61aを約400nm程度までの厚さで形成する。つぎに、基板温度を850〜950℃に昇温することによって、アモルファス層61aから図4に示すような島状の成長核61bを形成する。この成長核61bは介在層30の表面に対して傾斜した複数のファセット面を有する島状構造を有する。次に、成長核61bを覆うようにアンドープのGaNからなる下層領域61を約1000nm程度までの厚さで形成する。この下層領域61の最表面は、成長核61bの形状を反映して凹凸形状を有するようになる。つぎに、図6に示すように、基板温度を950〜1050℃に昇温し、下層領域61上にアンドープのGaNからなる上層領域62を形成し、転位低減層60とする。この上層領域62の形成は横方向への結晶成長を促すような条件でおこわなれるため、上層領域62の最表面は平滑になる。この際、貫通転位は成長面に対して垂直に延伸するため、貫通転位D5、D6は下層領域61の最表面、すなわち境界面60aにおいて曲げられる。ここで、貫通転位D5、D6は互いに逆向きのバーガースベクトルを有するものであり、これらが点P2で出会うことで消滅する。

【0043】

なお、下層領域61と上層領域62とは同じ組成を有する半導体材料からなり、その境界面60aにおいても結晶構造等が連続している。しかしながら、たとえばこの転位低減層60の断面を電子顕微鏡等で観察すると、多くの貫通転位が屈曲している境界面が存在する様子が観察されるので、境界面60aの位置および形状は容易に特定できる。

【0044】

つぎに、この電界効果トランジスタ100の耐圧性が高く、反りが小さくなることについて説明する。なお、以下では、基板10が凸状に反る場合をプラスの方向に反るとし、凹状に反る場合をマイナスの方向に反ると規定する。

【0045】

この電界効果トランジスタ100の製造の際には、介在層30、バッファ層20、半導体動作層40は1000〜1100℃程度の基板温度で形成される。ここで、基板10上に介在層30を形成すると、介在層30は基板10よりも格子定数が小さいので、反りはマイナスの方向に発生する。つぎに、介在層30上に転位低減層60を介して第1層目の第一半導体層211を形成すると、第一半導体層211は介在層30よりも格子定数が大きいので、第一半導体層211の層厚が薄いうちは反りがプラスの方向に発生する。しかし、第一半導体層211の層厚がある厚さ以上となると、第一半導体層211が基板10よりも格子定数が小さいことによって、プラスの方向の反りを打ち消すように反りがマイナスの方向に発生するようになる。以下では、半導体層がエピタキシャル基板に対して発生させる反りの方向が反転する際の、その半導体層の層厚を臨界厚さと呼ぶ。すなわち、臨界厚さとは、半導体層の層厚の変化に対して反りが極大点となる層厚を意味する。

【0046】

つぎに、第一半導体層211上に第二半導体層22を形成すると、第二半導体層22は第一半導体層211よりも格子定数が小さいので、反りはマイナスの方向に発生する。

【0047】

つぎに、第二半導体層22上に第一半導体層212を形成すると、第一半導体層211の場合と同様に、第一半導体層212の層厚が薄いうちは反りがプラスの方向に発生し、ある臨界厚さ以上となると、反りがマイナスの方向に発生するようになる。しかしながら、第一半導体層212の臨界厚さは、第一半導体層211の臨界厚さよりも厚くなる。この理由は、第一半導体層212の場合は、その下方に形成されている介在層30、転位低減層60、第一半導体層211、第二半導体層22の各半導体層(下地層)の影響を受けるためであると考えられる。

【0048】

ここで、第一半導体層212の層厚と第一半導体層211の層厚が同じ場合は、第一半導体層212において発生するマイナスの方向への反りは小さくなる。しかしながら、本実施の形態1では、上述したように、第一半導体層212は、第一半導体層211よりも厚く形成されている。その結果、第一半導体層212の臨界厚さが第一半導体層211の臨界厚さよりも厚くなっても、第一半導体層212においてマイナスの方向に発生する反りは大きく維持される。

【0049】

同様に、第二半導体層22を挟んで第一半導体層213、214、・・・と形成していくにしたがって、下地層の総層厚が厚くなるので、臨界厚さは厚くなっていく。これに対して、この電界効果トランジスタ100においては、第一半導体層213、214、・・・、218は、積層方向に向かって層厚が増加し、かつ各第一半導体層213、214、・・・、218の層厚は、その積層位置における臨界厚さよりも厚く形成されている。その結果、各第一半導体層211、・・・、218においてマイナスの方向に発生する反りが大きく維持されるため、プラスの方向に発生する反りは打ち消され、きわめて小さくなる。

【0050】

最後に、半導体動作層40を形成し、エピタキシャル成長を終了するが、半導体動作層40においても反りはトータルとしてプラスの方向に発生する。その後、基板温度を1000〜1100℃から常温に戻すが、バッファ層20、転位低減層60、介在層30、半導体動作層40のいずれも、基板10よりも熱膨張係数が大きいので、基板温度の低下につれて反りがマイナスの方向に発生し、最終的な反り量は小さい値となる。さらには、これによって反りを抑制しながらエピタキシャル層の総層厚を厚くできるので、耐圧性を高くできる。

【0051】

以上説明したように、この電界効果トランジスタ100は、反りが小さいと同時に、基板10上のエピタキシャル層の総層厚が厚いため耐圧性が高いものとなる。さらに、各第一半導体層211、・・・、218において反りが打ち消しあっているため、内在する歪みがきわめて低減されるという効果も奏する。

【0052】

なお、本実施の形態1において、最も薄い第一半導体層211の層厚は300nmであるが、200nm以上であればマイナスの方向の反りを発生させることができる。また、400nm以上であれば、発生するマイナスの方向の反りの量を十分に大きくすることができるのでさらに好ましい。また、各第一半導体層211、・・・、218の層厚が3000nm以下であれば、成長時間が十分に短いので、生産性が高く好ましい。

【0053】

また、第二半導体層22の層厚は、0.5nm以上200nm以下であれば、第一半導体層211、・・・、218に内在する歪みを十分に抑制できるので好ましい。

【0054】

また、第一半導体層211、・・・、218、第二半導体層22、・・・、22、介在層30の層厚は、上記実施の形態1の値に限られず、これらの組成、基板10との格子定数および熱膨張率差、デバイスに要求される耐圧、許容される反り量などに応じて適宜設定することができる。

【0055】

また、転位低減層60の層厚は、十分な転位低減効果を得るために充分に凹凸形状を形成し、かつ、平坦化させるためには100nm以上が好ましく、生産性を高めるには3000nm以下であることが好ましい。

【0056】

(変形例1〜4)

上記実施の形態1に係る電界効果トランジスタ100では、転位低減層60がバッファ層20直下の位置に形成されているが、転位低減層60の位置はこれに限定されず、バッファ層20直下から電子走行層41内部までのいずれかの位置に形成されていれば、その転位低減の効果を発揮することができる。以下、実施の形態1の変形例1〜4として、転位低減層60を様々な位置に形成した半導体電子デバイスについて説明する。

【0057】

(変形例1)

図7は、変形例1に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ200は、図1に示す電界効果トランジスタ100においてバッファ層20をバッファ層201に置き換えた構造を有している。このバッファ層201は、バッファ層20と同様の構成の第一半導体層211、・・・、218と第二半導体層22、・・・、22とが交互に積層した構造を有しているが、凹凸形状の境界面60aを有する転位低減層60が、バッファ層201内の第一半導体層216の直下の位置に形成されている。その結果、この電界効果トランジスタ200も、電界効果トランジスタ100と同様の作用により、反りが小さく、オン抵抗が低く、さらには耐圧性が高いデバイスとなる。また、この電界効果トランジスタ200は、転位低減層60が、基板10との間に少なくとも1つの第一半導体層が介在する位置に形成されている。このような構成の場合、基板10近傍で発生した貫通転位が、この少なくとも1つの第一半導体層内で一旦減少するため、転位低減層60において貫通転位をより消滅させ易くなるので、よりオン抵抗が低くなり好ましい。なお、さらなる変形例として、転位低減層60が、転位低減層60と基板10との間に第一半導体層および/または第二半導体層が少なくとも1つ介在する位置に形成されるような構成にすれば、変形例1と同様の効果を奏する電界効果トランジスタとなる。

【0058】

(変形例2)

図8は、変形例2に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ300は、図1に示す電界効果トランジスタ100においてバッファ層20をバッファ層202に置き換えた構造を有している。このバッファ層202は、バッファ層20と同様の構造を有しているが、バッファ層20の第一半導体層216に対応するものが第一半導体層216aと第一半導体層216bに分離しており、凹凸形状の境界面60aを有する転位低減層60がこの第一半導体層216aと第一半導体層216bとの間の位置に形成されている。その結果、この電界効果トランジスタ300も、電界効果トランジスタ100、200と同様の作用により、反りが小さく、オン抵抗が低く、さらには耐圧性が高いデバイスとなる。また、この電界効果トランジスタ300も、転位低減層60が、基板10との間に少なくとも1つの第一半導体層が介在する位置に形成されているので、転位低減層60において貫通転位をより消滅させ易くなるので、よりオン抵抗が低くなり好ましい。

【0059】

(変形例3)

図9は、変形例3に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ400は、図1に示す電界効果トランジスタ100において、転位低減層60を半導体動作層40の直下に形成した構成を有する。その結果、この電界効果トランジスタ400も、反りが小さく、耐圧性が高いとともに、転位低減層60により半導体動作層40の直前で一層効果的に貫通転移を消滅させることができるので、オン抵抗が一層低いデバイスとなる。

【0060】

(変形例4)

図10は、変形例4に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ500は、図1に示す電界効果トランジスタ100において半導体動作層40を半導体動作層401に置き換えた構造を有している。この半導体動作層401は、半導体動作層40と同様の構造を有しているが、半導体動作層40の電子走行層41に対応するものが電子走行層41aと電子走行層41bに分離している。そして、凹凸形状の境界面60aを有する転位低減層60が、半導体動作層401の内部である電子走行層41aと電子走行層41bとの間の位置に形成されている。なお、実際に電子が走行するのは電子走行層41bであるが、その層厚は電子の走行に影響を及ぼさないような層厚とされている。その結果、この電界効果トランジスタ500も、反りが小さく、耐圧性が高いとともに、転位低減層60により電子走行層41bの直前で一層効果的に貫通転移を消滅させることができるので、さらにオン抵抗が低いデバイスとなる。

【0061】

(実施例1〜3、比較例1)

つぎに、本発明の実施例1〜3として、実施の形態1、およびその変形例1、3に従う電界効果トランジスタを作製し、その積層方向の位置における転位密度を透過型電子顕微鏡(TEM)により測定した。一方、比較例1として、実施の形態1の構造において転位低減層の代わりに、均一に成長させたアンドープのGaN層を転位低減層と同じ1500nmの層厚で形成した電界効果トランジスタを作製し、その積層方向の位置における転位密度をTEMにより測定した。

【0062】

図11は、実施例1〜3、比較例1の電界効果トランジスタにおける、基板表面から測定した厚さの位置における螺旋転位の転位密度を示した図である。また、図12は、実施例1〜3、比較例1の電界効果トランジスタにおける、基板表面から測定した厚さの位置における刃状転位の転位密度を示した図である。図11、12に示すように、比較例1については、厚さが1μm程度に薄く基板に近い位置では各転位密度が大きく、厚さが厚くなるに従い各転位密度が減少している。また、実施例1においては、基板に近い位置に転位低減層を形成しているので、厚さが1μm程度において各転位密度は大幅に減少しており、厚さが厚くなっても低密度になっている。また、実施例2においては、厚さが1μm程度の位置では比較例1と同様に各転位密度が大きいが、転位低減層より上の位置の厚さで各転位密度が大きく減少しており、厚さが厚くなっても低密度になっている。また、実施例3においては、バッファ層に対応する位置の厚さまでは比較例1と同様の傾向を示しているが、転位低減層より上の位置の厚さで各転位密度が大きく減少しており、半導体動作層の位置の厚さで各転位密度がきわめて低くなっている。

【0063】

また、図13は、実施例1〜3、比較例1について、半導体動作層中である厚さが9.5μmの位置における螺旋転位および刃状転位の転位密度を示した図である。図13に示すように、実施例1〜3では、比較例1よりも各転位密度が低く、特に転位低減層の位置が半導体動作層に近くなるにつれて各転位密度がより低くなることが確認された。

【0064】

(実施の形態2)

つぎに、本発明の実施の形態2について説明する。図14は、本実施の形態2に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ600は、図1に示す電界効果トランジスタ100において、転位低減層60を転位低減層70に置き換えた構造を有している。この転位低減層70は、下層領域71と、反り低減層72と、第一上層領域73と、反り低減層74と、第二上層領域75とが順次積層した構造を有する。下層領域71、第一上層領域73、第二上層領域75はそれぞれアンドープのGaNからなる。また、反り低減層72、74は、それぞれアンドープのAlNからなる。

【0065】

この電界効果トランジスタ600の転位低減層70においては、下層領域71と、それよりも上部の領域である反り低減層72から第二上層領域75との間の境界面70aが凹凸状を有しているので、下方から延びてきた貫通転位が境界面70aの傾斜面において屈曲するため、電界効果トランジスタ100と同様に電子走行層41における貫通転位密度が低減され、オン抵抗が低くなる。

【0066】

また、このように、この転位低減層70は、GaNからなる下層領域71、第一上層領域73、第二上層領域75と、AlNからなる反り低減層72、74とが交互に積層しているので、バッファ層20と同様の作用により、転位低減層70の層厚が厚くなってもその反りは抑制される。なお、このような反り低減層の数は2つに限らず、1つまたは複数であればよい。

【0067】

また、この転位低減層70は、電界効果トランジスタ100における転位低減層60と同様の方法を用いて、適宜成長材料を変更して形成することができる。なお、反り低減層72から第二上層領域75については、横方向への結晶成長を促すような条件で形成するので、境界面70c、70dの凹凸形状は、境界面70a、70bの凹凸形状よりも傾斜が緩やかになっている。

【0068】

(実施の形態3)

つぎに、本発明の実施の形態3について説明する。図15は、本実施の形態3に係る電界効果トランジスタの模式的な断面図である。この電界効果トランジスタ700は、図1に示す電界効果トランジスタ100において、転位低減層60を転位低減層80に置き換えた構造を有している。この転位低減層80は、凹凸形状の境界面80aを有する下層領域81と上層領域82とを有する。下層領域81は、窒化シリコンまたは酸化シリコンからなる5nm程度までの厚さの島状の成長核81aを底部に有し、この成長核81aを覆うように形成されたアンドープのGaNからなる。また、上層領域82はアンドープのGaNからなる。

【0069】

この電界効果トランジスタ700の転位低減層80においては、境界面80aの凹凸形状が窒化シリコンまたは酸化シリコンからなる島状の成長核81aにより形成されている。窒化シリコンまたは酸化シリコンは、その成長の初期において島状の成長核81aを形成しやすいので、この電界効果トランジスタ700は、反りが小さくオン抵抗が低く耐圧性が高く、かつ製造性が高いものとなる。なお、この島状の成長核81aは、たとえば各種CVD法等の気相成長法を用いて形成できる。

【0070】

なお、上記各実施の形態においては、Siからなる基板を用いたが、SiC、ZnOからなる基板を用いてもよい。また、転位低減層の各領域または反り低減層、介在層、第一および第二半導体層の材質についても、窒化物系化合物半導体であり、格子定数および熱膨張率が基板も含めて所定の関係を満たすものであれば特に限定されない。たとえば、上記各実施の形態において、第二半導体層はAlNからなるものであったが、AlxGa1-xN(ただし、0<x<1)であってもよい。

【0071】

また、上記各実施の形態においては、半導体電子デバイスがHEMT型の電界効果トランジスタであったが、本発明はこれに限定されず、絶縁ゲート型(MIS型、MOS型)、ショットキーゲート型(MES型)等、種々の電界効果トランジスタに対して適用可能である。また、本発明は、電界効果トランジスタ以外にも、ショットキーダイオード等、各種ダイオードに対しては適用可能である。たとえば、実施の形態1の電界効果トランジスタ100において、ソース電極51、ドレイン電極52およびゲート電極53のかわりにカソード電極およびアノード電極を形成した構造とすれば、本発明を適用したダイオードを実現できる。なお、本発明を種々の半導体電子デバイスに適用する際に、転位低減層を半導体動作層の内部に形成する場合には、図10に示す変形例4と同様に、そのデバイスの動作特性に影響を及ぼさないような位置に転位低減層を形成する。

【図面の簡単な説明】

【0072】

【図1】実施の形態1に係る電界効果トランジスタの模式的な断面図である。

【図2】転位低減層の作用について説明する説明図である。

【図3】転位低減層の形成方法の一例を説明する説明図である。

【図4】転位低減層の形成方法の一例を説明する説明図である。

【図5】転位低減層の形成方法の一例を説明する説明図である。

【図6】転位低減層の形成方法の一例を説明する説明図である。

【図7】実施の形態1の変形例1に係る電界効果トランジスタの模式的な断面図である。

【図8】実施の形態1の変形例2に係る電界効果トランジスタの模式的な断面図である。

【図9】実施の形態1の変形例3に係る電界効果トランジスタの模式的な断面図である。

【図10】実施の形態1の変形例4に係る電界効果トランジスタの模式的な断面図である。

【図11】実施例1〜3、比較例1の電界効果トランジスタにおける、基板表面から測定した厚さの位置における螺旋転位の転位密度を示した図である。

【図12】実施例1〜3、比較例1の電界効果トランジスタにおける、基板表面から測定した厚さの位置における刃状転位の転位密度を示した図である。

【図13】実施例1〜3、比較例1について、半導体動作層中である厚さが9.5μmの位置における螺旋転位および刃状転位の転位密度を示した図である。

【図14】実施の形態2に係る電界効果トランジスタの模式的な断面図である。

【図15】実施の形態3に係る電界効果トランジスタの模式的な断面図である。

【符号の説明】

【0073】

10 基板

20、201、202 バッファ層

22 第二半導体層

30 介在層

40、401 半導体動作層

41、41a、41b 電子走行層

42 電子供給層

43 コンタクト層

43a 開口部

51 ソース電極

52 ドレイン電極

53 ゲート電極

60〜80 転位低減層

60a、70a〜70d、80a 境界面

61〜81 下層領域

61a アモルファス層

61b、81a 成長核

62、82 上層領域

72、74 反り低減層

73 第一上層領域

75 第二上層領域

100〜700 電界効果トランジスタ

211〜218、216a、216b 第一半導体層

D1〜D6 貫通転位

P1、P2 点

【特許請求の範囲】

【請求項1】

基板と、

前記基板上に形成された、該基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、

前記バッファ層上に形成された窒化物系化合物半導体からなる半導体動作層と、

窒化物系化合物半導体からなり、前記バッファ層直下から前記半導体動作層内部までのいずれかの位置に形成され、凹凸形状の境界面を有する下層領域と上層領域とを有し、該下層領域から該上層領域へ延伸する貫通転位が該境界面において屈曲している転位低減層と、

を備えたことを特徴とする半導体電子デバイス。

【請求項2】

前記転位低減層は、該転位低減層と前記基板との間に前記第一半導体層および/または前記第二半導体層が少なくとも1つ介在する位置に形成されることを特徴とする請求項1に記載の半導体電子デバイス。

【請求項3】

前記転位低減層は、前記半導体動作層の直下に形成されることを特徴とする請求項1に記載の半導体電子デバイス。

【請求項4】

前記転位低減層は、前記半導体動作層の内部に形成されることを特徴とする請求項1に記載の半導体電子デバイス。

【請求項5】

前記転位低減層は、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなることを特徴とする請求項1〜4のいずれか一つに記載の半導体電子デバイス。

【請求項6】

前記転位低減層は、層厚が100nm以上、3000nm以下であることを特徴とする請求項1〜5のいずれか一つに記載の半導体電子デバイス。

【請求項7】

前記転位低減層は、前記下層領域の底部に窒化シリコンまたは酸化シリコンからなる島状の成長核を有することを特徴とする請求項1〜6のいずれか一つに記載の半導体電子デバイス。

【請求項8】

前記基板は、シリコン、シリコンカーバイト、および酸化亜鉛のいずれかからなることを特徴とする請求項1〜7のいずれか一つに記載の半導体電子デバイス。

【請求項9】

前記転位低減層は、前記下層領域よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる少なくとも一つの反り低減層を有していることを特徴とする請求項1〜8のいずれか一つに記載の半導体電子デバイス。

【請求項10】

前記基板の直上に形成された、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層をさらに備えたことを特徴とする請求項1〜9のいずれか一つに記載の半導体電子デバイス。

【請求項11】

前記バッファ層は、前記各第一半導体層の層厚が積層方向に向かって増加するように形成されていることを特徴とする請求項1〜10のいずれか一つに記載の半導体電子デバイス。

【請求項12】

前記第一半導体層は、層厚が200nm以上、3000nm以下であることを特徴とする請求項1〜11のいずれか一つに記載の半導体電子デバイス。

【請求項13】

前記第二半導体層は、層厚が0.5nm以上、200nm以下であることを特徴とする請求項1〜12のいずれか一つに記載の半導体電子デバイス。

【請求項14】

基板上に、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層を形成するバッファ層形成工程と、

前記バッファ層上に窒化物系化合物半導体からなる半導体動作層を形成する半導体動作層形成工程と、

を含み、前記バッファ層形成工程または前記半導体動作層形成工程は、前記バッファ層直下から前記半導体動作層内部までのいずれかの位置に、窒化物系化合物半導体からなり、最表面が凹凸形状を有する下層領域を形成し、該形成した下層領域上に最表面が平滑な上層領域を形成する転位低減層形成工程をさらに含むことを特徴とする半導体電子デバイスの製造方法。

【請求項15】

前記転位低減層形成工程において、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる島状の成長核を形成し、該形成した成長核を覆うように前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる下層領域を形成することを特徴とする請求項14に記載の半導体電子デバイスの製造方法。

【請求項16】

前記成長核を400℃以上、600℃以下の基板温度で形成することを特徴とする請求項15に記載の半導体電子デバイスの製造方法。

【請求項17】

前記転位低減層形成工程において、窒化シリコンまたは酸化シリコンからなる島状の成長核を形成し、該形成した成長核を覆うように前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる下層領域を形成することを特徴とする請求項14に記載の半導体電子デバイスの製造方法。

【請求項18】

前記基板の直上に、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層を形成する介在層形成工程をさらに含むことを特徴とする請求項14〜17のいずれか一つに記載の半導体電子デバイスの製造方法。

【請求項1】

基板と、

前記基板上に形成された、該基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層と、

前記バッファ層上に形成された窒化物系化合物半導体からなる半導体動作層と、

窒化物系化合物半導体からなり、前記バッファ層直下から前記半導体動作層内部までのいずれかの位置に形成され、凹凸形状の境界面を有する下層領域と上層領域とを有し、該下層領域から該上層領域へ延伸する貫通転位が該境界面において屈曲している転位低減層と、

を備えたことを特徴とする半導体電子デバイス。

【請求項2】

前記転位低減層は、該転位低減層と前記基板との間に前記第一半導体層および/または前記第二半導体層が少なくとも1つ介在する位置に形成されることを特徴とする請求項1に記載の半導体電子デバイス。

【請求項3】

前記転位低減層は、前記半導体動作層の直下に形成されることを特徴とする請求項1に記載の半導体電子デバイス。

【請求項4】

前記転位低減層は、前記半導体動作層の内部に形成されることを特徴とする請求項1に記載の半導体電子デバイス。

【請求項5】

前記転位低減層は、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなることを特徴とする請求項1〜4のいずれか一つに記載の半導体電子デバイス。

【請求項6】

前記転位低減層は、層厚が100nm以上、3000nm以下であることを特徴とする請求項1〜5のいずれか一つに記載の半導体電子デバイス。

【請求項7】

前記転位低減層は、前記下層領域の底部に窒化シリコンまたは酸化シリコンからなる島状の成長核を有することを特徴とする請求項1〜6のいずれか一つに記載の半導体電子デバイス。

【請求項8】

前記基板は、シリコン、シリコンカーバイト、および酸化亜鉛のいずれかからなることを特徴とする請求項1〜7のいずれか一つに記載の半導体電子デバイス。

【請求項9】

前記転位低減層は、前記下層領域よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる少なくとも一つの反り低減層を有していることを特徴とする請求項1〜8のいずれか一つに記載の半導体電子デバイス。

【請求項10】

前記基板の直上に形成された、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層をさらに備えたことを特徴とする請求項1〜9のいずれか一つに記載の半導体電子デバイス。

【請求項11】

前記バッファ層は、前記各第一半導体層の層厚が積層方向に向かって増加するように形成されていることを特徴とする請求項1〜10のいずれか一つに記載の半導体電子デバイス。

【請求項12】

前記第一半導体層は、層厚が200nm以上、3000nm以下であることを特徴とする請求項1〜11のいずれか一つに記載の半導体電子デバイス。

【請求項13】

前記第二半導体層は、層厚が0.5nm以上、200nm以下であることを特徴とする請求項1〜12のいずれか一つに記載の半導体電子デバイス。

【請求項14】

基板上に、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる第一半導体層と該第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる第二半導体層とが交互に積層した2層以上の複合層を有するバッファ層を形成するバッファ層形成工程と、

前記バッファ層上に窒化物系化合物半導体からなる半導体動作層を形成する半導体動作層形成工程と、

を含み、前記バッファ層形成工程または前記半導体動作層形成工程は、前記バッファ層直下から前記半導体動作層内部までのいずれかの位置に、窒化物系化合物半導体からなり、最表面が凹凸形状を有する下層領域を形成し、該形成した下層領域上に最表面が平滑な上層領域を形成する転位低減層形成工程をさらに含むことを特徴とする半導体電子デバイスの製造方法。

【請求項15】

前記転位低減層形成工程において、前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる島状の成長核を形成し、該形成した成長核を覆うように前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる下層領域を形成することを特徴とする請求項14に記載の半導体電子デバイスの製造方法。

【請求項16】

前記成長核を400℃以上、600℃以下の基板温度で形成することを特徴とする請求項15に記載の半導体電子デバイスの製造方法。

【請求項17】

前記転位低減層形成工程において、窒化シリコンまたは酸化シリコンからなる島状の成長核を形成し、該形成した成長核を覆うように前記基板よりも格子定数が小さく熱膨張係数が大きい窒化物系化合物半導体からなる下層領域を形成することを特徴とする請求項14に記載の半導体電子デバイスの製造方法。

【請求項18】

前記基板の直上に、前記第一半導体層よりも格子定数が小さく前記基板よりも熱膨張係数が大きい窒化物系化合物半導体からなる介在層を形成する介在層形成工程をさらに含むことを特徴とする請求項14〜17のいずれか一つに記載の半導体電子デバイスの製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2010−87192(P2010−87192A)

【公開日】平成22年4月15日(2010.4.15)

【国際特許分類】

【出願番号】特願2008−254009(P2008−254009)

【出願日】平成20年9月30日(2008.9.30)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

【公開日】平成22年4月15日(2010.4.15)

【国際特許分類】

【出願日】平成20年9月30日(2008.9.30)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

[ Back to top ]