Fターム[5F140BA20]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 基板材料 (9,253) | 結晶軸、面方位の選択 (523)

Fターム[5F140BA20]に分類される特許

1 - 20 / 523

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】ソース領域110は、溝部300側面の第2面32に面し、一部が面31と面32の交線と平行な方向に延在する。ドリフト領域140は、溝部300のうち面32と反対の面33に面し、一部が面31および面33の交線と平行な方向に延在して設けられ、ソース領域110よりも低濃度に形成される。ドレイン領域120は、ドリフト領域140を介し溝部300の反対側に位置し、ドリフト領域140と接するように設けられ、ドリフト領域140よりも高濃度に形成される。第1ゲート絶縁層200は、溝部300の側面のうち面32と面33に交わる方向の面である面34と接するとともに、面31上のうち少なくともチャネル領域130と接する。ゲート電極400は、第1ゲート絶縁層200上に設けられ。溝部300はドリフト領域140よりも深い。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

電界効果トランジスタの製造方法および電界効果トランジスタ

【課題】ドーピング密度を増やすことなく、高濃度キャリア走行部を形成でき、高い移動度と低いオン抵抗を実現できる電界効果トランジスタの製造方法および電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタ1は、窒素ドープn型SiCドリフト層12のキャリア走行部14を挟むように形成されたソース13とドレイン15とを備える。ソース13とドレイン15は、エッチングによってキャリア走行部14に隣接して形成された段部16,17を有する。キャリア走行部14は、段部16,17の段差面16A,17Aに紫外光を照射することによって段部16,17から延びるように形成された積層欠陥部18を有する。積層欠陥部18は、3C‐SiCの結晶構造を持ち、量子井戸構造のようにふるまうことからキャリアがここに多数閉じ込められる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】結晶欠陥の発生を抑え、デバイスのリーク電流の発生、耐圧低下、しきい値電圧の継時変化、およびショートチャネル効果を抑制することが可能な半導体装置を提供すること。

【解決手段】単結晶AlNからなる基板を準備するステップと、前記単結晶AlNからなる基板の表面を酸素プラズマによって酸化し、単結晶AlNからなる基板上に酸化アルミニウムまたはアルミニウムオキシナイトライドからなる絶縁膜を形成するステップとを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

半導体装置

【課題】短チャネル効果の抑制およびオフリーク電流の抑制が可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置は、半導体基板において素子分離領域によって仕切られた素子領域と、前記素子領域を横切る所定の方向に沿って前記素子領域の表層に設けられたゲートトレンチにより分離されて前記素子領域の表層に形成されたソース領域およびドレイン領域とを備える。また、実施形態の半導体装置は、少なくとも一部が前記ゲートトレンチ内にゲート絶縁膜を介して埋め込まれて前記ソース領域およびドレイン領域よりも深い位置まで形成されたゲート電極を備える。ドレイン領域における前記ゲート絶縁膜と接触する界面は、前記ゲート電極側に突出した凸部を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETの隣接するフィン同士のショートを回避しつつ、エピタキシャル層の表面積を広く確保する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板の表面に形成され、(110)面である側面を有するフィンとを備える。さらに、前記装置は、前記フィンの側面に形成されたゲート絶縁膜と、前記フィンの側面および上面に、前記ゲート絶縁膜を介して形成されたゲート電極とを備える。さらに、前記装置は、前記フィンの側面に、フィン高さ方向に沿って順に形成された複数のエピタキシャル層を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

炭化ケイ素半導体装置の製造方法

【課題】炭化ケイ素(000−1)面にウェット雰囲気で酸化されたゲート絶縁膜の上に、ポリシリコンを不活性ガスを使用した減圧CVD法で成膜しても、界面準位密度の増加を抑制し、MOS界面特性の劣化を防止して、炭化ケイ素半導体装置の品質を高める。

【解決手段】炭化ケイ素半導体の(000−1)面から0°ないし8°傾いた面からなる半導体領域上に接するようにゲート絶縁膜を形成し、減圧CVD法を用いて、ゲート絶縁膜上に接するようにポリシリコンのゲート導電膜を成膜する際、不活性ガスを供給しながら安定化させる目標炉内温度を450℃以上550℃以下にするとともに、原料ガスを注入しながらポリシリコンのゲート導電膜の生成を行う工程、さらには、このゲート導電膜の生成終了後、原料ガスを不活性ガスに置換する工程を含め、炉内温度を一貫してこの目標炉内温度に維持した。

(もっと読む)

半導体装置、電気光学装置、電力変換装置及び電子機器

【課題】素子特性の低下を抑制することが可能な半導体装置を提供する。

【解決手段】シリコン基板11と、シリコン基板11の表面に形成された炭化シリコン膜12と、炭化シリコン膜12の表面に形成された、開口部13hを有するマスク材13と、開口部13hにおいて露出した炭化シリコン膜12を基点としてエピタキシャル成長された、炭化シリコン膜12及びマスク材13を覆う単結晶炭化シリコン膜14と、単結晶炭化シリコン膜14の表面に形成された半導体素子20と、を含み、マスク材13の上には、単結晶炭化シリコン膜14が会合して形成された会合部12Sbが存在しており、半導体素子20はボディコンタクト領域21を有しており、ボディコンタクト領域21は、シリコン基板11の表面と直交する方向から見て会合部12Sbと重なる位置に配置されている。

(もっと読む)

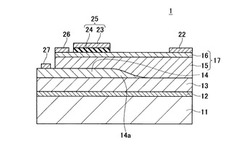

GaN系半導体装置

【課題】p型のGaN系半導体装置を提供する。

【解決手段】第1導電型のキャリアガスが発生した第1チャネル層106と、第1チャネル層106上に、第1チャネル層106よりバンドギャップが大きいGaN系半導体で形成されたバリア層110と、バリア層110上に、バリア層110よりバンドギャップが小さいGaN系半導体で形成され、第2導電型のキャリアガスが発生した第2チャネル層112と、第2チャネル層112にオーミック接続する第1ソース電極118と、第2チャネル層にオーミック接続する第1ドレイン電極120と、第1ソース電極118及び第1ドレイン電極120の間に形成された第1ゲート電極122と、を備え、第2導電型のキャリアガスのキャリア濃度が、第1ゲート電極122の下の領域で、第1ソース電極118及び第1ドレイン電極120の間の他の領域より低く、かつ、第1ゲート電極122により制御されるGaN系半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

電界効果トランジスタ

【課題】チャネルへの電子供給能力が改善されたIII−V族FETを提供する。

【解決手段】基板2の上には、ナローバンドギャップ材料のチャネル層4が形成される。チャネル層4の上のソース領域には、ワイドバンドギャップ材料のコンタクト層6が形成される。ソースコンタクト層6は、1×1019cm−3以上の濃度でドーピングされる。FET1は、ソースコンタクト層6によってアンドープのチャネル層4に直接キャリアが注入されるように構成される。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置

【課題】ゲート絶縁膜を形成する際に、界面準位を低減しつつ、EOTのさらなる低減が実現可能な金属酸化物高誘電体エピタキシャル膜の製造方法、および基板処理装置を提供すること。

【解決手段】単結晶領域102を有する基板101上に、金属膜であって、該金属膜の酸化物の誘電率が酸化シリコン膜よりも高く、かつ金属膜の酸化物が単結晶領域102とエピタキシャル関係を有する金属膜103を、単結晶領域102と金属膜103とが界面反応しない基板温度で形成する(図1(b))。金属膜103が形成された基板101を、上記界面反応しない基板温度で、単結晶領域102と金属膜103とが界面反応しない酸素分圧の酸素ガス雰囲気に暴露する(図1(c))。酸素ガス雰囲気に暴露された基板103を、上記酸素分圧の酸素ガス雰囲気に保持し、金属膜の酸化物である金属酸化物高誘電体膜が結晶化する基板温度で熱処理する(図1(d)。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

1 - 20 / 523

[ Back to top ]