Fターム[5F102FA00]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241)

Fターム[5F102FA00]の下位に属するFターム

高耐圧化 (602)

大電流化 (294)

ソース・ドレイン抵抗、コンタクト抵抗の低減 (386)

温度特性改善 (18)

チャネル表面準位による空乏層の防止 (41)

サージ入力対策(保護回路) (79)

インピーダンス整合 (12)

周辺素子からの影響防止、素子分離 (94)

試験、測定(製造中を含む) (43)

実装構造の改良 (50)

Fターム[5F102FA00]に分類される特許

1 - 20 / 622

高周波増幅器

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

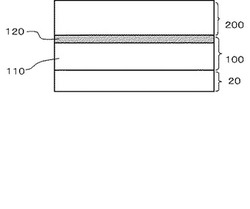

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供する。

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】閾値電圧のばらつきを低減できる炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置10は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを含む。炭化珪素層4は、チャネル層7と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、ゲート領域16Rとを含む。ゲート領域16Rはチャネル層7に対して、第1の導電型と異なる第2の導電型を有するようにエピタキシャル成長されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】第1の極性を有する第1の化合物半導体層と共にこれと逆極性(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置を得る。

【解決手段】第1の極性を有する電子走行層2bと、電子走行層2bの上方に形成された第2の極性を有するp型キャップ層2eと、p型キャップ層2e上に形成された第1の極性を有するn型キャップ層2fとを有しており、n型キャップ層2fは、厚みの異なる部位2fa,2fbを有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】薄いキャップ層を用いるも、応答速度が速く、ピンチオフ不良等のデバイス特性の劣化を抑止して安定なノーマリオフ動作を実現する信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】Si基板1上に化合物半導体積層構造2が形成され、化合物半導体積層構造2は、電子走行層2aと、電子走行層2aの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたキャップ層2dとを有しており、キャップ層2dは、電子走行層2a及び電子供給層2cと分極が同方向である第1の結晶2d1と、電子走行層2a及び電子供給層2cと分極が逆方向である第2の結晶2d2とが混在する。

(もっと読む)

窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法

【課題】シリコン基板上に形成したクラックおよび転位が少ない高品位の窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法を提供する。

【解決手段】実施態様によれば、下地層と、第1積層中間層と、機能層と、を備えた窒化物半導体素子が提供される。前記下地層は、基板の上に形成されたAlNバッファ層を含む。前記第1積層中間層は、前記下地層の上に設けられた第1AlN中間層と、前記第1AlN中間層の上に設けられた第1AlGaN中間層と、前記第1AlGaN中間層の上に設けられた第1GaN中間層と、を含む。前記機能層は、前記第1積層中間層の上に設けられている。前記第1AlGaN中間層は、前記第1AlN中間層に接する第1ステップ層を含む。前記第1ステップ層におけるAl組成比は、前記第1AlN中間層から前記第1ステップ層に向かう積層方向において、ステップ状に減少している。

(もっと読む)

窒化物半導体電子デバイス、窒化物半導体電子デバイスを作製する方法

【課題】チャネルリークを低減可能な窒化物半導体電子デバイスが提供される。

【解決手段】

【0097】ヘテロ接合トランジスタ11によれば、電流ブロック層27はp導電性を有する。ドープ半導体層17が開口部16の側面16aに設けられると共にドープ半導体層17が電流ブロック層27とチャネル層19との間に設けられるので、チャネル層19が、エッチングの際に開口部16の側面16aに形成されている可能性があるドナー性欠陥を含む半導体に直接に接触することがない。また、ドープ半導体層17は、電流ブロック層27とチャネル層19との間に設けられると共にチャネル層19はキャリア供給層21とドープ半導体層17との間に設けられるので、ドープ半導体層17の追加により、チャネル層19及びキャリア供給層21の配列は変更されることがない。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波特性の悪化を防ぎ、耐湿性を向上させる。

【解決手段】半導体基板1の主表面上の素子領域内に、ドレイン電極2が設けられている。一端がドレイン電極2に接続されたドレイン配線5が主表面上に設けられている。主表面上の素子領域外に、ドレイン配線5とは離間したドレイン電極パッド12が設けられている。Auメッキ層9が主表面上に設けられ、主表面との間に空隙10が形成されている。空隙10はドレイン配線5の一端とドレイン電極2を内包する。硬化されたポリイミド膜14が空隙10の開口部11を閉塞し、ドレイン電極パッド12を覆うことなく、ドレイン配線5の他端を覆っている。空隙10の内面に撥液膜15が設けられている。硬化されたポリイミド膜14に設けられた開口16を介してAuメッキ層18により、ドレイン配線5の他端とドレイン電極パッド12が接続されている。ドレイン配線5の他端はポリイミド膜14から出ていない。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】材料の熱膨張係数の差に起因するクラック等を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1上方に形成されたGaN系化合物半導体積層構造3と、基板1とGaN系化合物半導体積層構造3との間に設けられたAlN系の応力緩和層2と、が設けられている。応力緩和層2のGaN系化合物半導体積層構造3と接する面に、深さが5nm以上の窪み2aが2×1010cm-2以上の個数密度で形成されている。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

窒化物系半導体装置

【課題】ダイオード部とトランジスタ部の面積比率を自由に設定することが可能な窒化物系半導体装置を提供することを目的とする。

【解決手段】第1HEMT部30及び第2HEMT部31から成るトランジスタ部1と、第1電極24と電気的に短絡された第1ショットキー電極28及び第1ゲート電極26と電気的に第2ショットキー電極29から成るダイオード部2と、を備えて構成されている。また、第1電極24と第2電極25との間の領域に第1電極24に沿って、第1ゲート電極26及び第1ショットキー電極28が交互に形成され、かつ、第2電極25に沿って、第2ゲート電極27及び第2ショットキー電極29が交互に形成されている。さらに、第1ゲート電極26と第2ゲート電極27とは、対向して形成されており、第1ショットキー電極28と第2ショットキー電極29とは対向して形成されている。

(もっと読む)

炭化珪素半導体装置

【課題】オン抵抗が低く高速動作が可能でありノーマリオフ特性を有し、かつ一の基板を用いて構成された炭化珪素半導体装置を提供する。

【解決手段】第1、第2、第4および第5不純物領域11、12、21、22は第1導電型を有し、第3不純物領域13は第2導電型を有する。第1〜第3不純物領域11〜13は第1導電型の第1層34に達する。第4および第5不純物領域21、22は第2層35上に設けられている。第1〜第5電極S1、D1、G1、S2、D2は第1〜第5不純物領域のそれぞれの上に設けられている。第1および第5電極S1、D2の間と、第3および第4電極G1、S2の間とは電気的に接続されている。第4および第5不純物領域21、22の間を覆うゲート絶縁膜I2上に第6電極G2が設けられている。

(もっと読む)

トランジスタ用半導体基板、トランジスタ及びトランジスタ用半導体基板の製造方法

【課題】リーク電流が小さく、かつ、ノーマリオフ動作をするデバイスに適した半導体基板を提供する。

【解決手段】ベース基板と、ベース基板上に設けられた、IIIa族元素を含む窒化物の第1結晶からなる第1エピタキシャル結晶層と、第1エピタキシャル結晶層上に設けられ、第1結晶よりも大きなバンドギャップを有し、かつ、IIIa族元素及びIIIa族元素の一部を置換したIIIb族元素を含む窒化物の第2結晶からなる第2エピタキシャル結晶層とを備える半導体基板を提供する。上記の半導体基板において、第2エピタキシャル結晶層は、第1エピタキシャル結晶層に格子整合又は疑格子整合してもよい。

(もっと読む)

パワー素子およびその製造方法

【課題】本発明は、ノーマリーオフ動作が可能なパワー素子およびその製造方法を提供する。

【解決手段】本発明のパワー素子は、第1窒化物層を形成した後ゲート電極下部に第2窒化物層をさらに形成することによってゲート電極に対応する部分には2次元の電子ガス層が形成されないため、ノーマリーオフ動作が可能である。これによって、本発明の一実施形態に係るパワー素子は、ゲートの電圧に応じて2次元の電子ガス層の生成を調整することができ、ノーマリーオフ動作が可能であるため、消費電力を減少させ得る。また、ゲート電極に対応する第2窒化物層を形成するため、第1窒化物層を形成した後ゲート電極に対応する部分のみを再成長させたり、ゲート電極に対応する部分を除いた残り部分をエッチングする方法を用いることによって、リセス工程を省略することができることから素子の再現性を確保することが化膿であり、工程を単純化させることができる。

(もっと読む)

化合物半導体装置、およびその製造方法

【課題】

高周波信号遮断後の回復が早く、素子分離特性のよい化合物半導体エピタキシャル基板を提供する。

【解決手段】

半導体エピタキシャル基板は、単結晶基板と、単結晶基板上にエピタキシャル成長されたAlN層と、AlN層の上にエピタキシャル成長された窒化物半導体層とを有し、単結晶基板とAlN層間界面より、AlN層と窒化物半導体層間界面の方が凹凸が大きい、ことを特徴とする。

(もっと読む)

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

トランジスタ素子

【課題】n型不純物としてTeを用いたノンアロイ層を有していても、ベース電流、コレクタ電流のリーク電流が少ないトランジスタ素子を提供する。

【解決手段】基板11と、基板11上に設けられた高電子移動度トランジスタ構造層28と、高電子移動度トランジスタ構造層28上に設けられたヘテロバイポーラトランジスタ構造層29とを備えたトランジスタ素子10において、ヘテロバイポーラトランジスタ構造層29のノンアロイ層26,27は、n型不純物としてTeがドーピングされており、n型不純物濃度が1.0×1019cm-3以上2.0×1019cm-3以下にされているものである。

(もっと読む)

1 - 20 / 622

[ Back to top ]