Fターム[5F102FA08]の内容

接合型電界効果トランジスタ (42,929) | 目的、効果 (2,241) | 周辺素子からの影響防止、素子分離 (94)

Fターム[5F102FA08]に分類される特許

1 - 20 / 94

HEMT装置を製造するCMOSコンパチブルな方法とそのHEMT装置

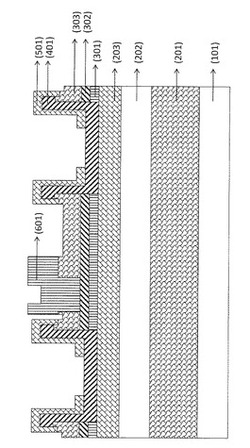

【課題】Si−CMOSプロセス時術とコンパチブルなHEMT装置の製造法を提供する。

【解決手段】基板101を提供するステップと、III族窒化物層のスタックを基板上に形成するステップと、窒化シリコンからなり、スタックの上方層に対して上に位置すると共に当接する第1パッシベーション層301を形成し、第1パッシベーション層が、現場でスタックに堆積されるステップと、第1パッシベーション層に対して上に位置すると共に当接する誘電体層を形成するステップと、窒化シリコンからなり、誘電体層に対して上に位置すると共に当接する第2パッシベーション層303を形成し、第2パッシベーション層が、LPCVD、MOCVD又は同等の手法によって450℃より高い温度で堆積されるステップと、ソースドレイン・オーミック接触とゲート電極601を形成するステップとを備える。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

化合物半導体装置及び化合物半導体装置の製造方法

【課題】トレンチを用いて素子分離され、且つ、隣接素子の動作による影響が抑制された化合物半導体装置及び化合物半導体装置の製造方法を提供する。

【解決手段】半導体基板10と、キャリア走行層21とキャリア供給層22を有し、半導体基板上に配置された窒化物半導体層20と、上端部がキャリア走行層とキャリア供給層との界面よりも上方に位置する空洞40を内部に有する、窒化物半導体層の周囲を囲んで配置された素子分離絶縁膜30とを備える。

(もっと読む)

直列接続式の高電子移動度トランジスターデバイス及びその製造方法

【課題】等価回路により電圧の累積効果を達成することが可能であって、ハイブレークダウン電圧の特性を有する高電子移動度トランジスターデバイスを提供する。

【解決手段】本発明は、製造プロセスで高電子移動度トランジスターを定義し、内部接続の方法で前記高電子移動度トランジスターを直列接続させた直列接続式の高電子移動度トランジスターデバイス及びその製造方法。

(もっと読む)

半導体装置の製造方法および半導体基板

【課題】所望のレジストパターンが形成可能な、インジウムおよび/またはアルミニウムを含む第1の層からなるフィールド領域を有する半導体装置の製造方法を提供する。

【解決手段】インジウムおよび/またはアルミニウムを含む第1の層からなるフィールド領域と、第1の層および第1の層とは異なる半導体層からなるメサ領域と、を備える半導体基板を用いた半導体装置の製造方法であって、フィールド領域表面に、半導体基板表面から半導体基板上に形成する電子ビーム露光用レジストへのインジウムおよびアルミニウムを含む成分の拡散を抑制する被覆層を形成する工程と、フィールド領域表面に被覆層が形成された半導体基板上に電子ビーム露光用レジストを塗布し、メサ領域の一部に電子ビームを露光し、現像することでメサ領域に開口部を有するレジストパターンを形成する工程と、メサ領域に開口部を有するレジストパターンを用いて半導体基板を修飾する工程とを有する製造方法。

(もっと読む)

熱スペーサを有する半導体デバイス

【課題】放熱スペースが短縮された、複数のユニットセルを有する高出力高周波半導体デバイスを提供する

【解決手段】ユニットセルは各々、制御電極24と、第1及び第2の被制御電極20,22とを有する。熱スペーサ(すなわち、電気的に不活性な領域)40が、これらのユニットセルのうち少なくとも1つを第1の活性部分及び第2の活性部分50に分割し、第2の活性部分は、この熱スペーサにより第1の部分から離隔される。ユニットセルの制御電極ならびに第1及び第2の被制御電極は、第1の熱スペーサを横切っている。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−SiO2の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

ハイパワーGaNベースFET用のレイアウトデザイン

【課題】FETを提供する。

【解決手段】FETは、基板と、基板上に配置されたバッファ層と、バッファ層上に配置されたチャネル層と、チャネル層上に配置された障壁層とを含む。ソース、ゲート及びドレイン電極は障壁層上に配置されて長手方向に延伸する。チャネル及び障壁層の一部分は長手方向に延伸するメサ部を形成し、ソース及びドレイン電極がメサ部の縁を超えて延伸する。ゲート電極はメサ部の縁側壁に沿って延伸する。導電性ソース相互接続部は障壁層上に配置されソース電極に電気的に接続された第一の端部を有する。第一の誘電体層はバッファ層及びソース相互接続部上に配置される。ゲートビアは第一の誘電体層に形成される。導電性ゲートノードがバッファ層に沿って延伸して前記メサ部の側壁に沿って延伸するゲート電極の一部分に電気的に接続する。ゲートパッドはメサ部に隣接する第一の誘電体層上に配置される。

(もっと読む)

半導体基板、半導体基板の製造方法、電子デバイス、および電子デバイスの製造方法

【課題】半導体基板におけるリーク電流を低減する。

【解決手段】ベース基板110と、ベース基板上110に形成され、第1の伝導型の多数キャリアを含む第1チャネル層208を有する第1半導体部200と、第1半導体部200の上方に形成され、第1半導体部200の不純物準位よりも深い準位の不純物準位を形成する不純物を有する分離層300と、分離層300の上方に形成され、第1チャネル層が含む第1の伝導型の多数キャリアと反対の伝導型の多数キャリアを含む第2チャネル層408を有する第2半導体部400とを備える半導体基板。

(もっと読む)

半導体デバイスおよび方法

半導体装置およびその製造方法

【課題】ゲート電極の内部に腐食が進行することを抑制する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置100は、化合物半導体基板101と、化合物半導体基板101上の一部に形成された接続部119と接続部119上に形成されかつ接続部119より幅広の本体部117とを有しており、かつアルミニウムを含むゲート電極118と、ゲート電極118の表面上に設けられた保護絶縁層(シリコン窒化膜120)と、シリコン窒化膜120が被覆していないゲート電極118の表面に設けられており、アルミニウムよりも酸化されにくい不動態膜124と、を備える。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素基板を用いた接合型FETにおいて、ゲート・ソース間のpn接合領域において生じるリーク電流を低減する。

【解決手段】炭化珪素基板を用いたトレンチ型接合FETにおいて、トレンチ5の側壁および底面に窒素を導入することにより、トレンチ5の表面にn型層8およびn+型層9を形成する。これによりp+型ゲート領域4とn+型ソース領域3との接合領域であるpn接合領域はダメージの多いトレンチ5の側壁ではなく半導体基板21の主面において露出し、また、その露出する領域は狭まるため、pn接合領域におけるリーク電流を低減することができる。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】工程増を最小限とした簡便な手法で、基板に反りを生ぜしめることなく、また基板上方の化合物半導体層の結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い装置構成を得る。

【解決手段】SiC基板1上の素子分離領域に相当する部位にマスク2を形成し、マスク2を覆うようにSiC基板1上に緩衝層3を第1の温度で形成し、第1の温度より高い第2の温度で加熱処理して緩衝層3のうちSiC基板1上の部位を結晶化し、緩衝層3の上方に化合物半導体層10を形成して、化合物半導体層10のマスク2の上方に相当する部位を素子分離領域とする。

(もっと読む)

コンプリメンタリー接合電界効果トランジスタを備えた炭化珪素半導体装置およびその製造方法

【課題】平坦面に対してデバイス形成できる絶縁分離構造を有し、かつ、高周波でのノイズ伝播や高温時でのリーク電流の発生を抑制できるCJFETを備えたSiC半導体装置を提供する。

【解決手段】絶縁分離層3にてn-型SiC層2やp-型SiC層4を絶縁分離する。これにより、平坦面に対してデバイス形成を行うことができる。このため、製造工程の簡略化を図ることが可能となる。また、PN分離ではなく、半絶縁性のイントリンシック層にて構成された絶縁分離層3によって絶縁分離構造を構成しているため、絶縁分離層3によって高周波ノイズを吸収することによる高周波でのノイズ伝播の抑制を行えると共に、高温時でのリーク電流の発生の抑制を行うことが可能となる。

(もっと読む)

ゲルマニウムベースの量子井戸デバイス

量子井戸トランジスタは、ゲルマニウムの量子井戸チャネル領域を有する。シリコンを含有したエッチング停止領域が、チャネル近くへのゲート誘電体の配置を容易にする。III−V族材料のバリア層がチャネルに歪みを付与する。チャネル領域の上及び下の傾斜シリコンゲルマニウム層によって性能が向上される。複数のゲート誘電体材料によって、high−k値のゲート誘電体の使用が可能になる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

高移動度チャネル(High−MobilityChannels)を有する装置のソース/ドレイン工学

【課題】高移動度チャネルを有する装置のソース/ドレイン工学を提供する。

【解決手段】集積回路構造は、基板及び基板の上方のチャネルを備える。チャネルは、III族元素とV族元素から構成される第一III-V族化合物半導体材料からなる。ゲート構造はチャネルの上方に設置される。ソース/ドレイン領域はチャネルに隣接し、本質的に、シリコン、ゲルマニウム、及び、それらの組み合わせからなる群から選択されるドープされたIV族半導体材料から形成されるIV族領域を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好な高周波特性及び電流コラプスの低減を両立することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成された表面保護膜10と、化合物半導体積層構造2上方に形成されたソース電極4、ドレイン電極5及びゲート電極6と、が設けられている。ゲート電極6には、その下面が化合物半導体積層構造2に接する接合部6aと、接合部6aよりもドレイン電極5側において、その下面が表面保護膜10の上面に接する乗り上がり部6bと、乗り上がり部6bよりもドレイン電極5側に位置し、その下面と表面保護膜10の上面との間に表面保護膜10よりも誘電率が低い領域が介在する離間部6cと、が設けられている。

(もっと読む)

化合物半導体素子

【課題】リーク電流の発生を抑制でき、良好なピンチオフ特性を有する化合物半導体素子を提供すること。

【解決手段】化合物半導体素子において、素子表面から基板1の厚さ方向にバッファ層2まで達する第1の素子分離部9を形成する。また、平面視において、第1の素子分離部9を囲むように位置する第2の素子分離部10を形成する。このようにして、電極7とバッファ層2との距離を大きくして、バッファ層2にかかる電界を緩和し、リーク電流を抑制する。

(もっと読む)

1 - 20 / 94

[ Back to top ]