Fターム[5F102HC01]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | エピタキシャル成長(分子線エピ、MOCVD等) (1,679)

Fターム[5F102HC01]の下位に属するFターム

選択エピ成長(溝部をエピで埋めるものを含む) (129)

単結晶と多結晶との同時形成 (4)

Fターム[5F102HC01]に分類される特許

1 - 20 / 1,546

パワートランジスタ装置のための多層構造を作製する方法、ヘテロ接合電界効果トランジスタ装置のための多層構造を作製する方法、および窒化物系ヘテロ接合電界効果トランジスタ装置

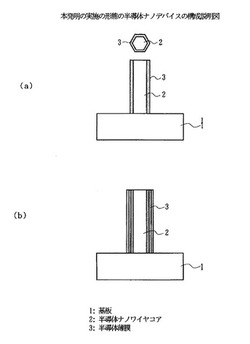

半導体ナノデバイス

【課題】 半導体ナノデバイスに関し、基板上における臨界膜厚を超えた厚さの歪のある半導体薄膜を形成してデバイス領域とする。

【解決手段】 長径が1μm未満の半導体ナノワイヤコアと、前記半導体ナノワイヤコアの側壁に形成され、前記半導体ナノワイヤコアの構成材料との歪εが1%以上異なる半導体材料からなり、且つ、膜厚t〔nm〕と歪ε〔%〕とが、

−0.720+0.0988ε−1.2<t≦−0.705+0.227ε−1.2

の関係を満たす少なくとも一層の半導体薄膜との接合界面或いは前記半導体薄膜同士の接合界面を機能領域とする。

(もっと読む)

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

トランジスタ装置および電子デバイス

【課題】1本の棒状素子が破壊しても、他の棒状素子が正常に動作し、正常動作を続けるトランジスタ装置を提供する。

【解決手段】トランジスタ装置は、基板5と、この基板5上に配置された2本の棒状素子1とを有する。このため、一方の棒状素子1が破壊しても、他方の棒状素子1が正常に動作し、トランジスタ装置は、正常動作を続ける。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

集積型半導体装置

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】

サファイア単結晶基板10の一方主面10A上に配置された第1素子機能部26と、一方主面上10Aに配置された第1アンテナ部23と、他方主面10Bに配置された第2素子機能部36と、他方主面10B上に配置された第2アンテナ部33とを備え、第1素子機能部26が第1アンテナ部23に送信用電気信号を送り、第1アンテナ部23が送信用電気信号に応じた電波を発信し、第2アンテナ部33がサファイア単結晶基板10を透過した電波を受信することで、高い周波数の信号を基板の上下面で高精度に処理することができる。

(もっと読む)

紫外線透過ゲート電極を有する電界効果トランジスタ

【課題】基板の自由度があり、待機時(光非照射時)の電力消費が小さく、また光照射時のS/Nが大きい受光素子を提供することである。

【解決手段】紫外線が透過する材料をFETの電極として用い、また、電子走行領域をAlGaNとGaNとのヘテロ界面等のGaN系膜同士のヘテロ界面とする。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法、及びエピタキシャルウエハ

【課題】AlNからなる半導体表面上に設けられると共に向上されたトランジスタ特性を有するIII族窒化物半導体電子デバイスを提供する。

【解決手段】5×107cm−2以下の転位密度を有しAlNからなる半導体表面21a上に、第1のエピタキシャル半導体層13はコヒーレントに設けられる。第2のエピタキシャル半導体層15は、第1のエピタキシャル半導体層13にヘテロ接合23aを成すように第1のエピタキシャル半導体層13上に設けられる。第1のエピタキシャル半導体層13がこの半導体表面21aへのコヒーレントな成長により、第1のエピタキシャル半導体層13は、半導体表面21aの格子定数に合わせて歪んであり、緩和していない。AlNに対してコヒーレントに設けられた第1のエピタキシャル半導体層13により、III族窒化物半導体電子デバイス11のトランジスタ特性が向上可能である。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

窒化物半導体構造の製造方法

【課題】平坦な表面を有し、結晶性の高い窒化物半導体下地層を、反りを抑えて、大きな成長速度で成長させることができる窒化物半導体構造の製造方法を提供する。

【解決手段】第3の窒化物半導体下地層を形成する工程において、第3の窒化物半導体下地層の成長時に単位時間当たりに供給されるV族原料ガスのモル量と単位時間当たりに供給されるIII族原料ガスのモル量との比であるV/III比を700以下とし、第3の窒化物半導体下地層の成長時の圧力を26.6kPa以上とし、第3の窒化物半導体下地層の成長速度を2.5μm/時以上とする、窒化物半導体構造の製造方法である。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】GaNを用いた窒化物半導体装置において、電流が流れる経路に、再結晶成長などによる界面が存在することがない状態で、十分な耐圧が得られるようにする。

【解決手段】GaNからなるチャネル層(第2半導体層)101と、チャネル層101の一方の面であるN極性面に形成された第1障壁層(第1半導体層)102と、チャネル層101の他方の面であるIII族極性面に形成された第2障壁層(第3半導体層)103とを備える。第1障壁層102および第2障壁層103は、例えば、AlGaNから構成されている。また、ドレイン電極(第1電極)104が、第1障壁層102の上に形成され、ゲート電極105が、ドレイン電極104に対向して第2障壁層103の上に形成されている。ソース電極(第2電極)106は、ゲート電極105と離間して第2障壁層103の上に形成されている。

(もっと読む)

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ、下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ、第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ、第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

窒化物半導体素子の製造方法

【課題】窒化珪素層を形成した場合でも、窒化物半導体層の転移密度を低減することができるとともに、窒化物半導体層の表面モフォロジーを優れたものとすることができる窒化物半導体素子の製造方法を提供する。

【解決手段】斜めファセットを有する第2の窒化物半導体層を有機金属気相成長法により形成する工程において、有機金属気相成長装置の成長室に供給されるIII族元素ガスに対するV族元素ガスのモル流量比が240以下である窒化物半導体素子の製造方法である。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】ノーマリーオフ特性を具現すると共にゲートリーク電流を抑制する窒化物半導体素子及びその製造方法を提供する。

【解決手段】第1の窒化物層31とその材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、その上にオミック接触されたソース電極50と、これから離間して窒化物半導体30層上にオミック接触されたドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に、これらから離間して形成されたP型窒化物層40と、この上に形成されたN型窒化物層140と、ソース側の側壁が、P型窒化物層40及びN型窒化物層140のソース側の側壁と整列するようにN型窒化物層140上に接触させたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】耐圧を高めた窒化物半導体素子及び製造方法を提供する。

【解決手段】第1の窒化物層31と該第1の窒化物層31の材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、該接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、窒化物半導体層30上にオーミック接触されるソース電極50とドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に形成され、ソース電極50から所定距離だけ離間された第1の側壁からドレイン側へ長く形成された多数のP型窒化物半導体セグメント80と、ソース電極50とドレイン電極60との間でソース電極50に近く形成され、多数のP型窒化物半導体セグメント80間の窒化物半導体層30上及びP型窒化物半導体セグメント80上に接触されるゲート電極70とを含む。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】閾値電圧のばらつきを低減できる炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置10は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを含む。炭化珪素層4は、チャネル層7と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、ゲート領域16Rとを含む。ゲート領域16Rはチャネル層7に対して、第1の導電型と異なる第2の導電型を有するようにエピタキシャル成長されている。

(もっと読む)

1 - 20 / 1,546

[ Back to top ]