Fターム[5F045AB09]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 3−5族 (4,971)

Fターム[5F045AB09]の下位に属するFターム

GaAs (282)

GaP (83)

InP (118)

InSb (19)

GaN (1,807)

ホウ素化合物 (33)

3元混晶 (1,276)

4元混晶 (505)

5元以上の混晶 (40)

Fターム[5F045AB09]に分類される特許

1 - 20 / 808

赤色発光半導体素子とその製造方法

半導体結晶膜の気相成長装置

半導体装置の製造方法

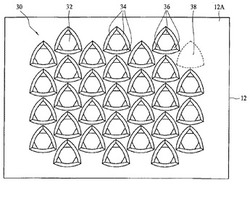

【課題】 半導体装置において、欠陥を減少させ、静電気放電に対する保護能力を高める。

【解決手段】 上面12Aおよび上面12Aに配置された複数のバンプ30を備えた基板1であって、バンプ30の各々が、上面12Aに対して実質的に平行な頂面32および頂面32と上面12Aとの間の複数の壁面34を有するものである基板12、および基板12上に配置されたエピタキシャル層であって、基板12の上面12Aおよびバンプ30の壁面34に実質的に同じ結晶方位を有するエピタキシャル層を備える。また、別の態様において、エピタキシャル層は、基板12上に配置され、実質的に単一の結晶方位を有し、実質的に空隙なく、基板12の上面12Aおよびバンプ30の壁面34を被覆するものであってよい。

(もっと読む)

光半導体素子及びその製造方法

【課題】高い光利得を得ながら閾値電流値を低減することができる光半導体素子及びその製造方法を提供する。

【解決手段】基板の上方に形成された複数の量子ドット層12と、複数の量子ドット層12間に位置する中間層と、が設けられている。量子ドット層12に含まれる量子ドット12aの組成が、InxGa1-xAsySb1-y(0<x≦1、0<y≦1)で表わされる。中間層には、組成がInaGa1-aAsbP1-b(0<a<1、0<b<1)で表わされ、厚さが10nm以上40nm以下のInGaAsP層13、15と、InGaAsP層13、15の底面から10nm以上40nm未満の高さに位置し、厚さが0.3nm以上2nm以下のInP層14と、が含まれている。

(もっと読む)

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

有機金属化学気相成長法による、高品質のN面GaN、InNおよびAlNならびにそれらの合金のヘテロエピタキシャル成長の方法

【課題】好適な有機金属化学気相成長法による、高品質のN面GaN、InNおよびAlNならびにそれらの合金のヘテロエピタキシャル成長の方法を提供する。

【解決手段】N面III族窒化物膜を成長させるための方法であって、(a)ミラー指数結晶面に対して誤配向角を伴う成長表面を有する基板を提供すること、(b)前記成長表面上または前記成長表面の上方で層を形成することであって、前記層は、前記層上で形成される1つ以上の後続の層に対するN極性配向を設定すること、および、(c)前記層上でN面III族窒化物膜を成長させることであって、前記N面III族窒化物膜は、前記層によって設定されるN極性配向を有することを含む。

(もっと読む)

III/V半導体

【課題】SiあるいはGaP技術をベースとする集積回路にモノリシックに集積化される、新しいIII/V半導体を用いた、発光ダイオードおよびレーザダイオードの半導体構造及び製造方法、あるいはまた、モジュレータ構造および検出器構造への使用法を提供する。

【解決手段】ドープされたSiあるいはドープされたGaPをベースとするキャリア層A、およびそこに配設されたIII/V半導体Dを備え、組成GaxInyNaAsbPcSbdを有するモノリシック集積回路構造であって、ここで、x=70−100モル−%、y=0−30モル−%、a=0.5−15モル−%、b=67.5−99.5モル−%、c=0−32.0モル−%およびd=0−15モル−%、xとyの合計は、常に100モル−%であり、a、b、cおよびdの合計は、常に100モル−%であり、そして、一方のxとyの合計と他方のaないしdの合計の比率は、実質的に1:1である。

(もっと読む)

III−V族化合物半導体層を含む半導体素子及びその製造方法

【課題】III−V族化合物半導体層を含む半導体素子及びその製造方法を提供する。

【解決手段】III−V族物質を含む半導体素子及びその製造方法に係り、該半導体素子は、溝を含むシリコン基板30と、溝周囲の基板上に形成されたハードマスク32と、溝を充填する、ハードマスク上に形成された第1物質層34と、第1物質層上に形成された上部物質層36、及び上部物質層上に形成された素子層と、を含み、該第1物質層は、III−V族物質層であり、該上部物質層は、第1物質層の一部でもあり、該上部物質層は、第1物質層と同一物質または異なる物質であってもよい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

気相成長装置

【課題】サセプタ上の複数の領域毎に材料ガスの混合比および流量を調整する。

【解決手段】被処理基板10が載置されるサセプタ120と、サセプタ120と対向し、被処理基板10上に複数の材料ガスを供給するシャワーヘッド130と、シャワーヘッド130に複数の材料ガスのうちの所定の複数の材料ガスを混合してそれぞれ導入する複数の混合配管と、複数の材料ガスの各々において流量を調整しつつ分岐してそれぞれを、複数の混合配管のいずれかに送る複数のガス分岐機構とを備える。シャワーヘッド130は、複数の混合配管のそれぞれで混合された複数の混合ガスをサセプタ上の複数の領域にそれぞれ噴き付ける。複数の混合ガスの各々においては、上記所定の複数の材料ガスの各々の濃度および流量が調節されている。

(もっと読む)

発光ダイオード、発光ダイオードの製造方法、発光ダイオードランプ及び照明装置

【課題】光吸収の低減された発光ダイオード、製造方法、ランプ、照明装置を提供する。

【解決手段】基板1上に設けられた発光層24を含む化合物半導体層10と、基板1と化合物半導体層10との間に設けられたオーミックコンタクト電極7と、化合物半導体層10の基板1の反対側に設けられたオーミック電極11と、オーミック電極11の表面を覆うように設けられた枝部12bと枝部12bに連結されたパッド部12aとを含む表面電極12と、発光層24のうちパッド部12aと平面視で重なる領域に配置されたパッド下発光層24aと、パッド部12aと平面視で重なる領域を除く領域に配置された発光層24との間に設けられ、パッド下発光層24aに供給される電流を妨げる電流遮断部13とを備える発光ダイオード100とする。

(もっと読む)

サセプタ及びそれを用いた気相成長装置

【課題】 急激な加熱に起因するサセプタの割れ、大型化による機械的強度の低下に起因するサセプタの割れを防止することが可能なサセプタ及びそれを用いた気相成長装置を提供する。

【解決手段】 中央部の孔、及び周辺部に基板ホルダーを収納するための孔を有するサセプタであって、中央部の孔と基板ホルダーを収納するための孔の間にスリットが設けられてなるサセプタとする。また、基板ホルダーを収納するためのサセプタ、該サセプタの対面、基板を加熱するためのヒータ、該サセプタと該サセプタの対面の間隙からなる反応炉、該反応炉へ原料ガスを供給する原料ガス導入部、及び反応ガス排出部を有する気相成長装置であって、前記のサセプタを用いた気相成長装置とする。

(もっと読む)

窒化物半導体層を成長させるためのバッファ層構造を有する基板とその製造方法

【課題】窒化物半導体デバイス用の半導体積層構造を成長させるために改善されたバッファ層構造を有する基板を提供する。

【解決手段】窒化物半導体層を成長させるためのバッファ層構造を有する基板は、Si単結晶基板の(111)主面上に形成された窒化ケイ素層、この窒化ケイ素層上に堆積されたAlN結晶層、およびこのAlN層上に堆積された複数のAlxGa1−xN(1>x>0)結晶層を含み、これら複数のAlxGa1−xN結晶層においてはその下層に比べて上層ほど小さなAl組成比xを有しており、複数のAlxGa1−xN層結晶中の一層は非晶質と結晶質が混在するAlN中間層を含んでいる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法、及びエピタキシャルウエハ

【課題】AlNからなる半導体表面上に設けられると共に向上されたトランジスタ特性を有するIII族窒化物半導体電子デバイスを提供する。

【解決手段】5×107cm−2以下の転位密度を有しAlNからなる半導体表面21a上に、第1のエピタキシャル半導体層13はコヒーレントに設けられる。第2のエピタキシャル半導体層15は、第1のエピタキシャル半導体層13にヘテロ接合23aを成すように第1のエピタキシャル半導体層13上に設けられる。第1のエピタキシャル半導体層13がこの半導体表面21aへのコヒーレントな成長により、第1のエピタキシャル半導体層13は、半導体表面21aの格子定数に合わせて歪んであり、緩和していない。AlNに対してコヒーレントに設けられた第1のエピタキシャル半導体層13により、III族窒化物半導体電子デバイス11のトランジスタ特性が向上可能である。

(もっと読む)

窒化物半導体成長用基板及びその製造方法、窒化物半導体エピタキシャル基板、並びに窒化物半導体素子

【課題】低転位密度の窒化物半導体を成長することが可能な窒化物半導体成長用基板及びその製造方法、並びに窒化物半導体成長用基板を用いて作製される窒化物半導体エピタキシャル基板及び窒化物半導体素子を提供する。

【解決手段】サファイア基板のC面である主面に、前記主面に対して90°未満で傾斜した側面を有する錐状または錐台状の凸部が格子状に配置して形成されており、前記主面からの前記凸部の高さが0.5μm以上3μm以下で、隣接する前記凸部間の距離が1μm

以上6μm以下であって、前記凸部の前記側面の表面粗さRMSが10nm以下である窒化物半導体成長用基板である。

(もっと読む)

窒化物半導体エピタキシャル基板

【課題】オフ角を有するSi基板を用いて、反りが小さく結晶性の高い窒化物半導体基板を提供する。

【解決手段】(111)結晶方位面に対して2.0°以上6.0°以下のオフ角を有するSi基板Wと、Si基板W上に形成されAlN単結晶層20a上にAlxGa1−xN単結晶層(0<x<1)20bが積層された第一バッファ領域Aと、第一バッファ領域A上に形成され厚さが300nm以上450nm以下のAlyGa1−yN単結晶(0≦y<0.1)からなる第1単層30aと厚さが5nm以上20nm以下のAlzGa1−zN単結晶(0.9<z≦1)からなる第2単層30bとが交互に複数積層された第二バッファ領域Bと、第二バッファ領域B上に形成された窒化物半導体活性層50と、からなる窒化物半導体基板Z。

(もっと読む)

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ、下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ、第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ、第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

窒化物半導体構造の製造方法

【課題】平坦な表面を有し、結晶性の高い窒化物半導体下地層を、反りを抑えて、大きな成長速度で成長させることができる窒化物半導体構造の製造方法を提供する。

【解決手段】第3の窒化物半導体下地層を形成する工程において、第3の窒化物半導体下地層の成長時に単位時間当たりに供給されるV族原料ガスのモル量と単位時間当たりに供給されるIII族原料ガスのモル量との比であるV/III比を700以下とし、第3の窒化物半導体下地層の成長時の圧力を26.6kPa以上とし、第3の窒化物半導体下地層の成長速度を2.5μm/時以上とする、窒化物半導体構造の製造方法である。

(もっと読む)

半導体製造装置及び製造方法

【課題】LEDまたはSiCデバイスのコスト低減のために、GaN、AlNまたはSiCバファー膜を大量に堆積できる装置、及び、GaNまたはSiCエピタキシャル層のストレスの低減法、基板形成方法を提供する。

【解決手段】縦型ホットウォールタイプのクリーニング用プラズマ手段つき、減圧CVDおよびリモートプラズマCVD装置によりデバイスのコストを低減する。基板のデバイス形成領域の周辺に深い溝を形成することで、GaNまたはSiCエピタキシャル層のストレスを低減する。さらに基板表面を異方性、等方性パターンをエッチングにより形成する基板形成する。LEDデバイス基板に関しては、その表面にSiO2パターンを形成し、マイクロチャネルエピタキシーによって良好なエピタキシャル膜を形成し、欠陥の少ない良好な膜を得るようにする。

(もっと読む)

1 - 20 / 808

[ Back to top ]