Fターム[5F045AB13]の内容

気相成長(金属層を除く) (114,827) | 成長層の組成 (12,584) | 3−5族 (4,971) | InSb (19)

Fターム[5F045AB13]に分類される特許

1 - 19 / 19

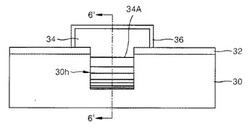

III−V族化合物半導体層を含む半導体素子及びその製造方法

【課題】III−V族化合物半導体層を含む半導体素子及びその製造方法を提供する。

【解決手段】III−V族物質を含む半導体素子及びその製造方法に係り、該半導体素子は、溝を含むシリコン基板30と、溝周囲の基板上に形成されたハードマスク32と、溝を充填する、ハードマスク上に形成された第1物質層34と、第1物質層上に形成された上部物質層36、及び上部物質層上に形成された素子層と、を含み、該第1物質層は、III−V族物質層であり、該上部物質層は、第1物質層の一部でもあり、該上部物質層は、第1物質層と同一物質または異なる物質であってもよい。

(もっと読む)

半導体積層基板およびその製造方法

【課題】様々な基板の上にシリコン以外の半導体の高品質なチャネル層によるCMOS構造が、複雑な工程を必要とせずに形成できるようにする。

【解決手段】半導体積層基板は、シリコン基板101の上に形成された酸化シリコン層102と、酸化シリコン層102の上に形成されたInAlAs層103と、InAlAs層103の上に形成されたGaAsSb層104と、GaAsSb層104の上に形成されたInGaAs層105と、InGaAs層105の上に形成されたp型のInAlAs層106と、p型のInAlAs層106の上に形成されたn型のInGaAs層107とを備える。

(もっと読む)

エピタキシャル構造体の製造方法

【課題】簡単な製造方法を有し、コストが低く、高品質のエピタキシャル構造体の製造方法を提供する。

【解決手段】エピタキシャル構造体の製造方法は、少なくとも一つの結晶面を有する基板100を提供する第一ステップと、前記基板100の結晶面101に複数の空隙を含むカーボンナノチューブ層102を配置し、前記基板100の結晶面101の一部を前記カーボンナノチューブ層102の複数の空隙によって露出させる第二ステップと、前記基板100の結晶面101にエピタキシャル層104を成長させ、前記カーボンナノチューブ層102を覆う第三ステップと、前記カーボンナノチューブ層102を除去する第四ステップと、を含む。

(もっと読む)

エピタキシャル構造体及びその製造方法

【課題】本発明は、エピタキシャル構造体及びその製造方法に関する。

【解決手段】本発明のエピタキシャル構造体の製造方法は、少なくとも一つの結晶面を有する基板を提供する第一ステップと、前記基板の結晶面に複数の空隙を含むカーボンナノチューブ層を配置する第二ステップと、前記基板の結晶面にエピタキシャル層を成長させる第三ステップと、を含む。

(もっと読む)

半導体装置の製造方法

【課題】高い結晶品質を有する量子ドットを高密度に形成しうる半導体装置の製造方法を提供する。

【解決手段】下地層10上に、自己組織化成長により量子ドット16を形成する工程と、量子ドット16を形成する工程の前又は量子ドット16を形成する工程の際に、下地層10の表面にSb又はGaSbを照射する工程と、量子ドット16の表面をAs原料ガスによりエッチングすることにより、量子ドット16の表面に析出したSbを含むInSb層18を除去する工程と、InSb層18が除去された量子ドット16上に、キャップ層22を成長する工程とを有している。

(もっと読む)

半導体基板上での逆相境界の無いIII−V化合物半導体材料およびその製造方法

【課題】逆相境界(APB)の無いIII−V化合物半導体材料およびその製造方法を提供する。

【解決手段】III−V化合物半導体材料の製造方法は、a){001}配向を有する第1半導体材料からなる基板と、基板の上に位置し、これと接触する絶縁層と、絶縁層内に、少なくとも部分的に基板を露出させる凹部領域を用意する工程と、b)凹部領域において露出基板の上に位置し、これと接触するバッファ層を形成する工程工程と、c)バッファ層の表面を粗面化するために、熱処理を印加する工程とを含み、バッファ層が、熱処理の印加後に二重ステップ表面を有する丸み形状をなし、d)凹部領域を、バッファ層の二重ステップ表面の上に位置し、これと接触するIII−V化合物半導体材料で少なくとも部分的に充填する工程をさらに含む。

(もっと読む)

半導体基板、半導体基板の製造方法、および電磁波発生装置

【課題】複数の異なる周波数を出力する半導体基板を提供する。

【解決手段】p型半導体またはn型半導体を含む第1の不純物半導体と、第1の不純物半導体に接する複数の空乏領域を有する空乏化半導体とを備え、複数の空乏領域のそれぞれは、第1の不純物半導体との第1界面と、第1界面と対向する表面とを有し、複数の空乏領域のそれぞれは、第1界面に垂直な方向における第1界面と表面との平均距離および組成の少なくとも一つが異なる半導体基板を提供する。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】トランジスタ中の電子移動度を向上させる上、デバイスの性能を向上させる高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタは、基板110と、基板110上に形成したバッファ層120と、複数のInGaAs薄膜と複数のInAs薄膜とを交互に積層して形成した超格子構造を含み、バッファ層120上に形成したチャネル層130と、チャネル層130上に形成したスペーサ層140と、スペーサ層140上に形成したショットキー層160と、ショットキー層160上に形成したキャップ層170とを備える。

(もっと読む)

蒸発器

固体前駆体送出組立体(200)は、概して、上部および下部を有する容器(202)と、入口チャンバ(238)、出口チャンバ(244)、ならびに第1の前駆体チャンバおよび第2の前駆体チャンバ(240、242)を含む容器内に画定される複数のチャンバを備える。第1の前駆体チャンバおよび第2の前駆体チャンバは、容器内に前駆体物質を保持するように構成される。焼結フリット(248、250、252)は、容器の内部部分に固定結合および封止され、容器内の複数のチャンバの少なくとも一部を画定する。焼結フリットのうちの少なくとも1つは、第1の前駆体チャンバ内で前駆体物質を上に保持するように構成され、焼結フリットのうちの少なくとも1つは、第2の前駆体チャンバ内で前駆体物質を上に保持するように構成される。入口(206)は、搬送ガスを容器に送出するために容器に結合され、出口(208)は、気化した前駆体物質および搬送ガスを容器から取り出すのに用いるために容器に結合される。 (もっと読む)

帯状に延在するガス入口区域を有するCVD反応炉及びCVD反応炉内の基板上に層を堆積する方法

プロセスチャンバ(1)の床(3)は基板(4)を受容するサセプタ(2)により形成され天井(6)は多数のガス入口開口(13,14)を具備するガス入口部品(5)の下面により形成され、ガス入口開口は帯状の第1及び第2のガス入口区域(11,12)に分割されており、第1のガス入口開口(13)は第1のプロセスガスを導入するために第1のプロセスガス供給ライン(9)に接続され、第2のガス入口開口(14)は第2のプロセスガスを導入するために第2のプロセスガス供給ライン(10)に接続され、かつ、第1及び第2のガス入口区域は互いに沿って交互に並んでおり、各々は延在方向に対して垂直な方向に一列に並んだガス入口開口を有し、隣り合うガス入口開口の間隔(D)はプロセスチャンバの高さ(H)のほぼ1/4であり、ガス入口区域の各々の幅(W)はほぼ高さ(H)に相当するCVD反応炉である。 (もっと読む)

基板の表面に均一なエピタキシャル層を成長させる方法および回転ディスク式反応器

【課題】基板キャリアの処理面の全体にわたって、反応ガスの均一な分布をもたらし、反応ガスの速度が異なることによって引き起こされる乱流を回避することができる反応器及び方法を提供する。

【解決手段】この1又は複数のガス流れはキャリアガスと反応ガスとを含み、異なる部分は異なる濃度の反応ガスを含むように、ガス流れ生成器は構成される。基板キャリアが軸を中心として回転可能に設けられている場合、異なる濃度の反応ガスを含む前記1又は複数のガス流れを、軸から異なる半径方向距離に供給するように、ガス流れ生成器は構成される。基板キャリアの軸に近い部分に向かうガスは、比較的高濃度のキャリアガスと比較的低濃度の反応ガスを含み、基板キャリアの軸から遠い部分に向かうガスは、高濃度の反応ガスを含む。これにより、実質的に均一な速度で、チャンバー内の基板キャリアに向けて送達するように構成されたガス流れ生成器を備えている。

(もっと読む)

半導体素子及びそれを備えた半導体装置

【課題】表面平坦性を大きく改善し、さらに良好な電子移動度を有するインジウム系化合物半導体薄膜を備えた半導体素子及びそれを備えた半導体装置を提供すること。

【解決手段】本発明の半導体素子は、ガリウム砒素からなる基板1上に形成されるインジウム系化合物半導体薄膜を備えている。ガリウム砒素の表面が、ガリウム砒素(100)面又はこのガリウム砒素(100)面と結晶学的に等価な面に対して(0−1−1)方向、又はガリウム砒素(100)面と結晶学的に等価な方向に、0.2度以上2.4度以下の角度で傾斜している。インジウム系化合物半導体薄膜は、p型インジウム系化合物半導体薄膜3とn型インジウム系化合物半導体薄膜2との積層構造を有する。この半導体素子は各種の光デバイスに適用可能である。

(もっと読む)

半導体量子ドット及び同形成方法

【課題】

巨大アイランドの形成による結晶品質の低下という問題を引き起こすことなく、ナノ構造の品質・形状を高品質に保つことを可能とする半導体量子ドット及び同形成方法を提供すること。

【解決手段】

本願に係る半導体量子ドット形成方法は、自己組織化機構により半導体量子ドットを形成する方法において、量子ドットDの結晶成長レート及び/もしくは埋め込み層L4の結晶成長速度として1ML/s(モノレイヤー・パー・セカンド)以上によって層形成させる。

(もっと読む)

固体有機金属化合物の充填方法

【解決手段】上部に各1か所以上のキャリアガス入口及び出口配管をそれぞれ有する容器内に固体有機金属化合物を供給し、この固体有機金属化合物をその融点以上に加熱融解した後、冷却して固体有機金属化合物を前記容器内に充填する方法において、得られた固体有機金属化合物の容器上部の出口配管を減圧に引きながら、バルブ及び配管部分を加熱してこれらバルブ及び配管部分に付着した固体有機金属化合物を出口配管から除去することを特徴とする固体有機金属化合物の充填方法。

【効果】本発明の固体有機金属化合物の充填方法によれば、使用開始の初期段階から、容器内に充填した固体有機金属化合物を安定した濃度で供給できるため、気相成長用原料として直ちに使用することができる。

(もっと読む)

中赤外光用半導体デバイスの製造方法

【課題】良質でなおかつ既存のものに比べて高性能な半導体デバイスを、安価に製造することができる、中赤外光領域で作動する半導体デバイスの製造方法を提供する。

【解決手段】

結晶基板1上にバッファ層2を積層して形成した基本積層体3上に、特定のエッチング液により選択的に除去可能な薄厚の犠牲層4を積層する犠牲層積層ステップと、その犠牲層上にデバイス層5を形成した後、犠牲層4のみをエッチング除去して前記デバイス層5を前記基本積層体3から分離するデバイス層分離ステップと、前記デバイス層分離ステップにおいてデバイス層5とともに分離された前記基本積層体3に対し、前記犠牲層積層ステップ及びデバイス生成ステップを再度施す再利用ステップと、を有するようにした。

(もっと読む)

半導体装置の製造方法

【課題】高い結晶品質を有する量子ドットを高密度に形成しうる半導体装置の製造方法を提供する。

【解決手段】下地層10上に、自己組織化成長により量子ドット16を形成する工程と、量子ドット16を形成する工程の前又は量子ドット16を形成する工程の際に、下地層10の表面にSb又はGaSbを照射する工程と、量子ドット16の表面をAs原料ガスによりエッチングすることにより、量子ドット16の表面に析出したSbを含むInSb層18を除去する工程と、InSb層18が除去された量子ドット16上に、キャップ層22を成長する工程とを有している。

(もっと読む)

Si基板上への半導体薄膜形成方法及びその構造物

【課題】 簡易な工程でありながらも、比較的安価なSi基板上に高品質な半導体薄膜を形成する方法と、その方法によって得られる半導体薄膜構造物を提供すること。

【解決手段】 Si基板上に半導体を結晶成長させて薄膜を形成する方法であって、対象の半導体を結晶成長させるSi基板の上面を、微小角度傾斜させた状態で、結晶成長装置内にSi基板をセッティングし、そのSi基板の傾斜角度は、対象半導体結晶の底面に相応する結晶軸の格子定数のSi基板上面に対する正射影が、Si基板の上面に相応する結晶軸の格子定数と略一致する角度とする。

(もっと読む)

有機金属気相沈殿によって基板に化合物を析出させる方法

【課題】

寄生的沈殿の発生なしにメチル有機気相沈殿によって基板に化合物を析出させる方法を提供すること

【解決手段】

この発明は、少なくとも一つのキャリアガスと少なくとも一つの有機金属とから成る第一混合物と、少なくとも一つのキャリアガスと少なくとも一つのグループV化合物或いはグループVI化合物とから成る第二混合物とから成り、両混合物がMOCVD装置へ別々に供給され、有機金属気相沈殿によって基板に化合物を析出させる方法に関する。少なくとも一つのキャリアガスと少なくとも一つの有機金属とから成る第一混合物は、この発明によると、基板と少なくとも一つのキャリアガスと少なくとも一つのグループV化合物或いはグループVI化合物とから成る第二混合物との間の装置に供給される。これによって、好ましくは、寄生的沈殿がMOCVD装置の壁に生じないことが奏される。それ故に、析出率は従来の技術水準の方法に比べて上昇される。  (もっと読む)

(もっと読む)

有機金属化合物

【課題】化合物半導体の製造方法を提供する。

【解決手段】基体上に第IIIA族金属を含むフィルムを堆積させる方法であって、a)気相における、式R3M(式中、Mは、第IIIA族金属であり、各Rは独立して、(C1−C10)有機基または水素である)を有する第IIIA族金属化合物を、前記基体を収容している堆積チャンバへ運搬する工程;b)気相における触媒化合物の触媒量を、前記基体を収容している堆積チャンバへ運搬する工程;c)第VA族気体化合物を、前記基体を収容している堆積チャンバへ運搬する工程;d)第IIIA族金属化合物および第VA族気体化合物を、堆積チャンバにおいて分解する工程;およびe)基体上に第IIIA族金属を含むフィルムを堆積させる工程を含み、前記触媒化合物が、第VA族気体化合物の分解を触媒する、フィルムを堆積させる方法。

(もっと読む)

1 - 19 / 19

[ Back to top ]