Fターム[5F152NN12]の内容

再結晶化技術 (53,633) | 基板材料(積層体を基板として扱う場合も含む) (4,266) | 絶縁体 (1,429) | 絶縁性金属化合物 (628)

Fターム[5F152NN12]の下位に属するFターム

サファイア (367)

Fターム[5F152NN12]に分類される特許

1 - 20 / 261

ムライトを主成分とする焼結体

III族窒化物複合基板の製造方法

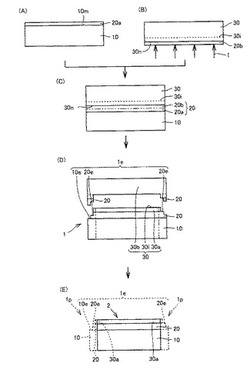

【課題】支持基板とIII族窒化物層との接合が良好なIII族窒化物複合基板の製造方法を提供する。

【解決手段】本III族窒化物複合基板の製造方法は、目標とする基板径より大きい径の主面10mを有する支持基板10と、目標とする基板径より大きい径の主面30nを有しその主面30nから所定の深さの位置にイオン注入領域30iが形成されたIII族窒化物基板30とを、中間層20を介在させて貼り合わせ、III族窒化物基板30をイオン注入領域30iにおいてIII族窒化物層30aと残りのIII族窒化物基板30bとに分離することにより、支持基板10上に中間層20を介在させてIII族窒化物層30aが接合された第1のIII族窒化物複合基板1を形成し、第1のIII族窒化物複合基板1の外周部を除去することにより目標とする基板径に等しい径の主面を有する第2のIII族窒化物複合基板2を得る。

(もっと読む)

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

β−Ga2O3系基板の製造方法、及び結晶積層構造体の製造方法

【課題】還元雰囲気や不活性ガス雰囲気下におけるドナー濃度の変化が抑えられたβ−Ga2O3系基板の製造方法、及び還元雰囲気や不活性ガス雰囲気下において品質のばらつきの小さい高品質な結晶膜をエピタキシャル成長させることのできる結晶積層構造体の製造方法を提供する。

【解決手段】IV族元素を含むβ−Ga2O3系結晶からβ−Ga2O3系基板を切り出す工程を含み、還元雰囲気及び不活性ガス雰囲気の少なくともいずれか一方を含む雰囲気下でのアニール処理が、前記β−Ga2O3系基板を切り出す前の前記β−Ga2O3系結晶、又は切り出された前記β−Ga2O3系基板に施される、β−Ga2O3系基板の製造方法を提供する。

(もっと読む)

III族窒化物複合基板

【課題】支持基板と酸化物膜との接合強度および酸化物膜とIII族窒化物層との接合強度が高いIII族窒化物複合基板を提供する。

【解決手段】本III族窒化物複合基板1は、支持基板10と酸化物膜20とIII族窒化物層30aとを含み、支持基板10は多結晶で形成され、III族窒化物層30aは少なくともc軸方向に配向しているIII族窒化物結晶で形成され、酸化物膜20は不純物が添加され、不純物の濃度は、酸化物膜20において支持基板10側の第1主面20sからIII族窒化物層30a側の第2主面20tにかけて膜厚方向で変化し、第1主面20sにおける不純物の濃度は第2主面20tにおける不純物の濃度よりも高い。

(もっと読む)

複合基板の製造方法

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成するステップと、犠牲層の一部が露出するように半導体結晶層をエッチングし、半導体結晶層を複数の分割体に分割するステップと、転写先基板に接することとなる半導体結晶層形成基板側の第1表面と、第1表面に接することとなる転写先基板側の第2表面と、が向かい合うように、半導体結晶層形成基板と転写先基板とを貼り合わせるステップと、半導体結晶層形成基板および転写先基板をエッチング液に浸漬して犠牲層をエッチングし、半導体結晶層を転写先基板側に残した状態で、転写先基板と半導体結晶層形成基板とを分離するステップと、を有し、前記半導体結晶層が、GexSi1−x(0<x≦1)からなる、複合基板の製造方法を提供する。

(もっと読む)

複合基板の製造方法および複合基板

【課題】結晶成長用基板に形成した半導体結晶層を転写先基板に転写する場合の犠牲層のエッチング速度を高める。

【解決手段】半導体結晶層形成基板の上に犠牲層および半導体結晶層を順に形成し、転写先基板に接することとなる前記半導体結晶層形成基板の第1表面と、前記第1表面に接することとなる前記転写先基板の第2表面と、が向かい合うように、前記半導体結晶層形成基板と前記転写先基板とを貼り合わせ、前記半導体結晶層形成基板および前記転写先基板の全部または一部をエッチング液に浸漬して前記犠牲層をエッチングし、前記半導体結晶層を前記転写先基板側に残した状態で、前記転写先基板と前記半導体結晶層形成基板とを分離する。ここで、前記転写先基板が、非可撓性基板と有機物層とを有し、前記有機物層の表面が、前記第2表面であるものとする。

(もっと読む)

半導体装置およびその製造方法

【課題】閾値電圧を制度良く制御することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板10上に、窒化物半導体からなるチャネル層14と、チャネル層14よりもバンドギャップエネルギーの大きい第1窒化物半導体層16と、を順次形成する工程と、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲートを形成する工程と、ダミーゲートを形成した後、第1窒化物半導体層16上のダミーゲート以外の領域に、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層18を再成長する工程と、ダミーゲートを除去した後、ダミーゲートを除去した領域の第1窒化物半導体層16上にゲート電極26を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

III族窒化物層複合基板の製造方法

【課題】支持基板上にIII族窒化物層が接合していない欠陥領域がない高品質のIII族窒化物層複合基板の製造方法を提供する。

【解決手段】本III族窒化物層複合基板の製造方法は、III族窒化物基板20にイオン注入領域20iを形成し、III族窒化物基板20のイオンが注入された側の主表面側および支持基板10の主表面側の少なくともひとつに接合用前駆体層40を形成し、III族窒化物基板20と支持基板10とを接合用前駆体層40を介在させて接合し、接合用前駆体層40をリフローさせることにより接合層50を形成し、III族窒化物基板20をイオン注入領域20iにおいて分離してIII族窒化物層21と残りのIII族窒化物基板22とにすることにより、支持基板10の主表面上に接合層40を介在させてIII族窒化物層21が接合されたIII族窒化物層複合基板1を形成する。

(もっと読む)

半導体基板の再生方法、再生半導体基板の作製方法、及びSOI基板の作製方法

【課題】半導体基板の再生に適した方法を提供する。

【解決手段】損傷半導体領域と絶縁層とを含む凸部が周縁部に存在する半導体基板に対し、絶縁層を除去するエッチング処理と、硝酸、硝酸によって酸化された半導体基板を構成する半導体材料を溶解する物質、半導体材料の酸化速度及び酸化された半導体材料の溶解速度を制御する物質、及び亜硝酸を含み、亜硝酸の濃度が10mg/l以上1000mg/l以下である混合液を用いて、未損傷の半導体領域に対して損傷半導体領域を選択的に除去するエッチング処理と、を行うことで半導体基板を再生する。

(もっと読む)

半導体装置

【課題】プラスチック支持体を用いた半導体装置を提供する。

【解決手段】プラスチック支持体上に形成されたカラーフィルタと、前記カラーフィルタ

上に形成された接着層と、前記接着層上に形成された絶縁膜と、前記絶縁膜上に形成され

た薄膜トランジスタと、前記薄膜トランジスタ上に形成された発光素子とを有する。また

は、プラスチック支持体と、前記プラスチック支持体に対向する対向基板と、前記プラス

チック支持体と前記対向基板との間に保持された液晶とを有し、前記プラスチック支持体

上に形成されたカラーフィルタと、前記カラーフィルタ上に形成された接着層と、前記接

着層上に形成された絶縁膜と、前記絶縁膜上に形成された薄膜トランジスタとを有する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体装置

【課題】高周波数動作が可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に設けられたGaN電子走行層14と、GaN電子走行層14上に設けられたAlNスペーサ層16と、AlNスペーサ層16上に設けられたInAlN電子供給層18と、InAlN電子供給層18上に設けられたゲート電極24とゲート電極24を挟むソース電極26およびドレイン電極28と、を備え、AlNスペーサ層16の膜厚が、0.5nm以上1.25nm以下の半導体装置である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】InAlN電子供給層上にGaN層を形成する場合でも、InAlN電子供給層の品質の悪化を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、基板10上にGaN電子走行層14を形成する工程と、GaN電子走行層14上にInAlN電子供給層18を形成する工程と、InAlN電子供給層18を形成した後、In含有ガスを供給しつつ、基板10を昇温させる工程と、昇温が終了した後、InAlN電子供給層18上にGaN層20を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

【課題】ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する。

【解決手段】SiC層10にSiO2層を形成し、次いで、熱伝導率を高めるためにダイアモンド層11を形成する。そして、SiC層10の厚さを低減し、ダイアモンド層11及びSiC層10の向きを逆にしてダイアモンド11を基板とする。次いで、SiC層10上に、バッファ層16、ヘテロ構造層14及び15を形成する。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】より安定した電気的特性の酸化インジウム亜鉛でなる酸化物半導体膜を提供する。また、当該酸化物半導体膜を用いることにより、半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】酸化インジウム亜鉛でなる酸化物半導体膜において、当該酸化物半導体膜は、a−b面が酸化物半導体膜表面に概略平行である六方晶の結晶構造と、a−b面が該酸化物半導体膜表面に概略平行である菱面体晶の結晶構造と、を有する酸化物半導体膜である。

(もっと読む)

半導体ウエハの製造方法、複合基体および複合基板

【課題】半導体デバイスを効率よく製造するために、基体の種類の如何を問わずに効率よく半導体ウエハを製造することができる半導体ウエハの製造方法、ならびにかかる製造方法に好適に用いられる複合基体および複合基板を提供する。

【解決手段】本半導体ウエハの製造方法は、基体10上に、表面のRMS粗さが10nm以下の基体表面平坦化層12を形成して複合基体1を得る工程と、複合基体1の基体表面平坦化層12側に半導体結晶層20aを貼り合わせて複合基板3A,3B,3Cを得る工程と、複合基板3A,3B,3Cの半導体結晶層20a上に少なくとも1層の半導体層30を成長させる工程と、基体表面平坦化層12をウェットエッチングで除去することにより、基体10から半導体結晶層20aを分離して、半導体結晶層20aおよび半導体層30を含む半導体ウエハ5を得る工程と、を含む。

(もっと読む)

複合基体および複合基板

【課題】焼結基体と半導体結晶層とが貼り合わせられた複合基板およびかかる複合基板に好適に用いられる複合基体を提供する。

【解決手段】本複合基体1は、焼結基体10と、焼結基体10上に配置された基体表面平坦化層12と、を含み、基体表面平坦化層12の表面のRMS粗さが10nm以下である。本複合基板は、複合基体1と、複合基体1の基体表面平坦化層12側に配置された半導体結晶層と、を含み、焼結基体10の熱膨張係数と半導体結晶層の熱膨張係数との差が4.5×10-6K-1以下である。

(もっと読む)

1 - 20 / 261

[ Back to top ]