Fターム[5F140AA30]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 目的 (9,335) | 大電流化 (642) | 低オン抵抗化 (457)

Fターム[5F140AA30]に分類される特許

81 - 100 / 457

半導体装置

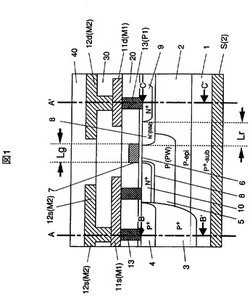

【課題】ドレインオフセット領域を有する高周波増幅用MOSFETにおいて、微細化およびオン抵抗低減を図る。

【解決手段】ソース領域10、ドレイン領域9およびリーチスルー層3(4)上に電極引き出し用の導体プラグ13(p1)が設けられている。その導体プラグ13(p1)にそれぞれ第1層配線11s、11d(M1)が接続され、さらにそれら第1層配線11s、11d(M1)に対して、導体プラグ13(p1)上で裏打ち用の第2層配線12s、12dが接続されている。

(もっと読む)

電界効果トランジスタ

【課題】オン抵抗が低く耐圧および信頼性が高い電界効果トランジスタを提供する。

【解決手段】基板1上に形成されたキャリア走行層3と、前記キャリア走行層上に形成され前記キャリア走行層よりもバンドギャップエネルギーが高いキャリア供給層4a、4bと、前記キャリア供給層から前記キャリア走行層の表面または内部に到る深さまで形成されたリセス部5と、前記キャリア供給層上に形成されたドレイン電極11と、前記リセス部に形成され、前記ドレイン電極側のキャリア供給層と重畳するように延設したゲート電極7と、前記リセス部の底面と前記ゲート電極との間に形成された第1絶縁膜6と、前記ゲート電極と前記ドレイン電極側のキャリア供給層との間に形成され前記第1絶縁膜よりも誘電率が高い第2絶縁膜8aとを備える。

(もっと読む)

双方向素子および半導体装置

【課題】高耐圧でオン電圧を低くできる双方向素子および半導体装置を提供すること。

【解決手段】分割半導体領域にpオフセット領域5とその表面に第1、第2nソース領域9、10を形成することで、第1、第2nソース領域9、10の平面距離を短縮してセルの高密度化を図り、トレンチに沿って耐圧を維持させることで高耐圧化を図り、ゲート電極7の電圧を第1、第2nソース電極11、12より高くすることで、トレンチ側壁にチャネルを形成して、双方向へ電流が流れる高耐圧で低オン電圧の双方向LMOSFETとすることができる。

(もっと読む)

半導体装置の製造方法

【課題】高耐電圧により大電流化が可能で、オン抵抗が低く高速動作が可能で、高集積化と省エネルギーが可能で、素子間分離の容易な、電気熱変換素子駆動用の半導体装置を提供する。

【解決手段】電気熱変換素子とそれに通電するためのスイッチング素子とがp型半導体基体1に集積化されている。スイッチング素子は、半導体基体1の表面に設けられたn型ウェル領域2と、それに隣接して設けられチャネル領域を提供するp型ベース領域6と、その表面側に設けられたn型ソース領域7と、n型ウェル領域2の表面側に設けられたn型ドレイン領域8,9と、チャネル領域上にゲート絶縁膜を介して設けられたゲート電極4とを有する絶縁ゲート型電界効果トランジスタである。ベース領域6は、ドレイン領域8,9を横方向に分離するように設けられた、ウェル領域2より不純物濃度の高い半導体からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】 LDMOS型トランジスタなどの半導体装置が動作中に生ずる経時的な特性変動を抑制すると共に、高耐圧かつ低オン抵抗が実現される半導体装置およびその製造方法を提供する。

【解決手段】 N型半導体層102に、深さが1μmより小さいP型の第1ドレインオフセット領域103と、深さが第1ドレインオフセット領域103より小さく、不純物濃度が第1ドレインオフセット領域103より大きいP型の第2ドレインオフセット領域105と、第1ドレインオフセット領域103より深いN型のボディ領域106と、N型のソース領域107およびドレイン領域104とを設ける。またLOCOS酸化膜からなる絶縁膜110と、ゲート絶縁膜108を介して形成されたゲート電極109とをN型半導体層102上に備える構造とする。

(もっと読む)

多勾配ドレインドーピング特性を持つ高電圧縦型トランジスタ

【課題】デバイスのオン状態及びオフ状態の両方の破壊電圧を同時に最適化する高電圧トランジスタ構造。

【解決手段】高電圧トランジスタは、半導体基板のメサを定める第一及び第二の溝を含む。第一及び第二のフィールドプレート部材は、それぞれ、第一及び第二の溝に配置され、第一及び第二のフィールドプレート部材の各々は、誘電体層でメサから分離されている。メサは複数の部分を含み、各部分は、実質的に一定のドーピング濃度勾配を持ち、一の部分の勾配は、他の部分の勾配よりも少なくとも10%大きい。

(もっと読む)

ノーマリオフ型GaN系電界効果トランジスタ

【課題】ゲート耐電圧が高くかつオン抵抗が低減されたノーマリオフ型GaN系FETを提供する。

【解決手段】ノーマリオフ型GaN系FETは、第1種GaN系半導体からなるチャネル層4と、このチャネル層上で互いに隔てて設けられた第2種GaN系半導体からなる一対の電子供給層5と、これら電子供給層の間でチャネル層を覆うゲート絶縁膜7と、チャネル層にオーミックコンタクトしているソース電極およびドレイン電極と、ゲート絶縁膜上に形成されたゲート電極とを備え、ゲート絶縁膜はチャネル層上に順次堆積された第1と第2の絶縁層を含み、第1絶縁層7aはSiの酸化物、窒化物および酸窒化物のいずれかからなりかつ5nm以下の厚さを有し、第2絶縁層7bは第1絶縁層に比べて大きなε×Ecを有し、ここでεは誘電率を表し、Ecは絶縁破壊電界を表している。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 高い閾値電圧と、低いオン抵抗とを両立可能であり、かつ、パラレル伝導を抑制できる電界効果トランジスタを提供する。

【解決手段】

基板601上に、III族窒化物のバッファ層602、チャネル層603、障壁層605、およびキャップ層606が、前記順序で積層され、

各半導体層の上面は、(0001)結晶軸に垂直なIII族原子面であり、

バッファ層602は、格子緩和され、

障壁層605は、引っ張り歪みを有し、

チャネル層603およびキャップ層606が圧縮歪みを有するか、または、チャネル層603が格子緩和され、キャップ層606が引っ張り歪みを有し、

障壁層605上の一部の領域に、キャップ層606、ゲート絶縁膜607、およびゲート電極608が、前記順序で積層され、他の領域に、ソース電極609とドレイン電極610が形成されていることを特徴とする電界効果トランジスタ。

(もっと読む)

電界効果トランジスタ、およびその製造方法

【課題】高い移動度、低いオン抵抗を備えたノーマリオフ型の電界効果トランジスタを提供する。

【解決手段】III族窒化物系化合物半導体からなるチャネル層104と、前記チャネル層上に形成されたAlInGaNからなる界面層106と、前記界面層上に形成され、前記界面層に達するリセス部を備えたIII族窒化物系化合物半導体からなる電子供給層108と、前記リセス部を挟んで、前記電子供給層108上に形成されたソース電極110およびドレイン電極112と、前記リセス部の内表面に形成された絶縁膜120と、前記絶縁膜上に形成されたゲート電極114とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧とオン抵抗とのトレードオフ関係を改善する。

【解決手段】ゲート絶縁膜及びLOCOS領域の下、及びドレイン領域を囲むようにドレイン領域に接してオフセット領域を設け、オフセット領域を、第1オフセット領域と、第1オフセット領域の上にドレイン領域を囲み且つLOCOS酸化膜の下に形成される第2オフセット領域と、前記オフセット領域のソース領域側の端部からLOCOSのソース領域側の端部までの間のみに形成される第3オフセット領域とで形成し、第2オフセット領域の不純物濃度を、第1オフセット領域及び第3オフセット領域よりも高くする。高濃度の第2オフセット領域を設けることによりオン抵抗の低減を図り且つ高濃度の第2オフセット領域を低濃度のオフセット領域で挟むことにより、第2オフセット領域の深さ方向の空乏化を促進し電界の緩和を図り耐圧の向上を図る。

(もっと読む)

酸化後のシリコントレンチ底部形状の構造及び形成方法

【課題】効率的に形成されかつボイドが僅かであるかまたは実質的に存在しないFCC構造を提供する。

【解決手段】基板内で上表面からある深さまで垂直に伸長し、かつ第1の側壁、第1の底部、及びトレンチの当該第1の底部近傍の当該第1の側壁に形成されているパターン215を有する第1のトレンチ210を基板内に形成するステップと、第1のトレンチの第1の側壁及び第1の底部上に酸化層235を形成するステップと、を含むLFCCデバイスの製造方法であって、酸化層は、第1のトレンチ内に配されかつ酸化層によって第1のトレンチから分離されている第2のトレンチをもたらす。第2のトレンチは、パターンを呈さず実質的に垂直な第2の側壁及び実質的に平坦な第2の底部を有する。当該パターンは、第1のトレンチの底部と第1の側壁との間の酸化レートの差を補償する。当該LFCC構造は、当該パターンを有する第1のトレンチを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧性の維持と低オン抵抗化との両立が可能なLDMOSトランジスタを提供する。

【解決手段】半導体装置は、第1導電型のドリフト拡散領域10と、第2導電型のボディ拡散領域2と、第1導電型のソース拡散領域6と、ドリフト拡散領域10の上部に形成されたトレンチ内に埋め込まれ、ボディ拡散領域2とは離間した位置に形成された絶縁膜14と、ドリフト拡散領域10の上部に形成され、絶縁膜14から見てソース拡散領域6と逆の方向に隣接する第1導電型のドレイン拡散領域7と、ボディ拡散領域2上からドリフト拡散領域10上を越えて絶縁膜14上にまで形成されたゲート電極5とを備えている。また、ドリフト拡散領域10は、基板内部領域11と、基板内部領域11よりも高濃度の第1導電型不純物を含む表面領域12とを有している。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の低いパワーMOS等の半導体装置を提供する。

【解決手段】ゲート酸化膜を介しゲート電極22を形成するゲート電極形成工程と、ゲート電極間よりも広い第1の開口部を有する第1のレジストパターンを形成する工程と、第1の開口部において露出している表面に第1の導電型の不純物元素をイオン注入する第1のイオン注入工程と、ゲート電極間よりも狭い第2の開口部31を有する層間絶縁膜30を形成する層間絶縁膜形成工程と、第2の開口部よりも広い第3の開口部を有する第2のレジストパターン32を形成する工程と、第3の開口部33において露出している表面に第2の導電型の不純物元素をイオン注入する第2のイオン注入工程と、を有し、第2のイオン注入工程において注入される第2の導電型の不純物元素の濃度は、第1のイオン注入工程において注入される第1の導電型の不純物元素の濃度の2倍以上であることを特徴とする。

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

III族窒化物系へテロ電界効果トランジスタ

【課題】オン動作時には電子移動の抵抗が低く、かつオフ動作時にはゲート電極と2次元電子ガスとのゲートリーク電流が発生しにくいIII族窒化物系へテロ電界効果トランジスタを提供する。

【解決手段】本発明のIII族窒化物系へテロ電界効果トランジスタは、基板と、該基板の上に設けられるキャリア走行層と、該キャリア走行層上に、ヘテロ界面を形成するように設けられる障壁層と、該障壁層上の一部からキャリア走行層の内部まで掘り込まれたリセス構造と、該リセス構造上に設けられる絶縁層と、該絶縁層上に設けられるゲート電極とを含み、キャリア走行層および障壁層はいずれも、III族窒化物半導体からなり、絶縁層は、リセス構造の側面上に形成される側面絶縁層と、リセス構造の底面上に形成される底面絶縁層とからなり、側面絶縁層の厚みは、前記底面絶縁層の厚みよりも厚いことを特徴とする。

(もっと読む)

半導体装置

【課題】電子回路の小型化を実現する。

【解決手段】MOSトランジスタ20が、格子状に形成されたゲート電極22と、ゲート電極22で囲まれたソース領域23およびドレイン領域24と、ゲート電極22の格子の一方向に沿って配置され、ソース領域23およびドレイン領域24とコンタクトを介して接続するソース用メタル配線27およびドレイン用メタル配線28を有する。ソース領域23およびドレイン領域24のそれぞれは、各メタル配線の長さ方向に長辺を有する長方形状に形成される。ソース用メタル配線27およびドレイン用メタル配線28は、その長さ方向にジグザグ形状に形成されて、それぞれソース用コンタクト25およびドレイン用コンタクト26に接続する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート閾値電圧を低下させることなく、チャネル移動度を向上できる炭化珪素MOSFETを提供する。

【解決手段】炭化珪素半導体装置200は、炭化珪素基板10と、炭化珪素基板10上に形成された炭化珪素層20と、炭化珪素層20上に形成されたゲート絶縁膜30と、ゲート絶縁膜30を介して炭化珪素層20上の所定位置に形成され、III族軽元素であるB、AlまたはGaをp型ドーパントとして含む多結晶シリコンからなるゲート電極40とを有する。そして、ゲート電極40中の上記p型ドーパントを、ゲート電極40直下の炭化珪素層20とゲート絶縁膜30との界面近傍に拡散させ、上記p型ドーパントによって界面近傍の不純物準位をパッシベーションする。

(もっと読む)

ドープされたエピタキシャル領域を有する半導体装置およびその製造方法

本発明の実施例として、半導体装置上のエピタキシャル領域を示した。ある実施例では、エピタキシャル領域は、成膜−エッチングプロセスを経て基板に成膜される。周期的な成膜−エッチングプロセスの間に、スペーサの下側に形成されるキャビティは、エピタキシャルキャップ層によって埋め戻される。エピタキシャル領域およびエピタキシャルキャップ層は、チャネル領域での電子移動度を改善し、短チャネル効果が抑制され、寄生抵抗が低下する。  (もっと読む)

(もっと読む)

誘電体分離型半導体装置

【課題】高耐圧かつ、電流駆動能力が高く、かつ電流集中による素子破壊の起こりにくい誘電体分離型半導体装置を提供する。

【解決手段】半導体支持基板の上に、絶縁された第一導電型の半導体領域とを有する誘電分離基板に形成した誘電体分離型半導体装置において、第一導電型の半導体領域と絶縁分離領域の間と、前記第1導電型の半導体領域の基板表面側と、に形成されたドレイン領域と、第一導電型のソースと第二導電型の半導体領域のチャネルからなる複数個の単位ソース領域と、第一導電型の半導体領域の基板表面側に形成されたドレイン領域と前記複数個の単位ソース領域の間を制御する複数個のゲート電極とを、備え、隣接する前記単位ソース領域間に絶縁分離領域が、基板底面側から基板表面側に向けて突き出した形状とされ、この絶縁分離領域上の素子表面領域が前記第一導電型の半導体領域より抵抗値が高い。

(もっと読む)

81 - 100 / 457

[ Back to top ]