Fターム[5F140AB02]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 複合(回路要素) (3,149) | MOSIC、MISIC (2,326) | E/EMOS、E/DMOSを構成するもの (22)

Fターム[5F140AB02]に分類される特許

1 - 20 / 22

ゲート電極が駆動する電界効果型トランジスタおよびそれを有するセンサデバイス

【課題】 ゲート電極が可動な電界効果型トランジスタを提供する。

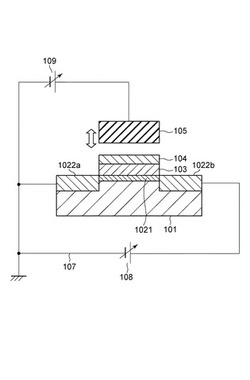

【解決手段】 半導体層と、前記半導体層内に少なくとも2つの活性領域と、前記活性領域に接するソース電極およびドレイン電極と、前記ソース電極と前記ドレイン電極との間の半導体層の上に絶縁層とゲート電極とを有する電界効果型トランジスタであって、

前記電界効果型トランジスタは前記ゲート電極および前記絶縁層の間に配置される、分子を吸着するための吸着部位を有し、

前記ゲート電極を駆動するための駆動手段を有することを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

ターンオン防止付き複合半導体デバイス

【課題】ターンオン防止付き複合半導体デバイスを提供する。

【解決手段】本明細書は、ターンオン防止制御を有する複合III-窒化物半導体デバイスの種々の実現を開示する。1つの好適な実現では、ノーマリオフ複合半導体デバイスが、ノーマリオンIII-窒化物パワートランジスタ、及びこのノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイスを具えて、ノーマリオフ複合半導体デバイスを形成する。このLVデバイスは、ノイズを伴う環境内で、ノイズ電流が、ノーマリオンIII-窒化物パワートランジスタのチャネルを通って流れることを防止することによって、ノーマリオフ複合半導体デバイスに、ターンオン防止制御を与えるように構成されている。

(もっと読む)

半導体装置および基準電圧生成回路

【課題】所望の温度特性を有することによって回路規模を小さくできるMOSトランジスタを提供する。

【解決手段】ゲート絶縁膜30は、ソース領域51とドレイン領域52との間の領域の上に設けられる。ゲート電極40は、ゲート絶縁膜30の上に設けられる。空乏層42は、P型半導体層41とP型半導体層41の下層(ゲート絶縁膜30)との接合面に生じる。温度が変化すると、ゲート電極40内部の空乏層42の領域が変化し、チャネル形成に対するゲート電圧の影響が変化するので、閾値電圧は通常のMOSトランジスタの場合よりも変化する。このことを利用し、MOSトランジスタが所望の温度特性を有するよう制御されるので、温度補正回路が不要になる。よって、回路規模が小さくなる。

(もっと読む)

半導体装置及びその製造方法

【課題】製造工程数を増加させることなく、ESD保護素子としてのLDMOSトランジスタのスナップバック電圧をESD被保護素子としてのLDMOSトランジスタのスナップバック電圧より低くし、且つESD保護素子としてのLDMOSトランジスタの熱破壊電流値をスナップバック電圧の改善前より大きくする。

【解決手段】 ESD保護素子としてのLDMOSトランジスタ32は、N型エピタキシャル層3と、N+型埋め込み層2と、N型エピタキシャル層3の表面に形成されたドリフト層11と、エピタキシャル層3の表面に形成されたP型のボディ層10と、Pボディ層10の表面に形成されたN+型ソース層14と、エピタキシャル層3の表面上に形成されたゲート絶縁膜5、6と、ゲート絶縁膜5、6上に形成されたゲート電極8と、を具備し、N+型ソース層14の下方のボディ層10の底部にP型ボディ層窪み部10aが形成されている。

(もっと読む)

高電圧動作電界効果トランジスタとそのバイアス回路およびその高電圧動作回路要素

【課題】 ICまたはLSIの標準電源電圧用のトランジスタ構成部分ないしはプロセス技術を活用して高電圧動作電界効果トランジスタを該IC中に作りこむ。

【解決手段】 電界効果トランジスタの動作電圧を大きくするために、ゲートにドレイン電位に応じて変化する電位分布を設ける手段をとる。

(もっと読む)

半導体装置の製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを半導体基板上に集積する場合に製造コストを低減できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、ディプレッション型電界効果トランジスタの形成予定領域12Daでゲート電極12に開口部32,33を形成する工程と、ゲート電極12をマスクとして、アクティブ領域21に不純物を斜めイオン注入することにより、開口部32,33の下方にゲート電極12の両側の一方から他方にかけて連続的に分布する不純物拡散領域を形成すると同時に、ゲート電極12の両側にそれぞれ不純物拡散領域を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】エンハンスメント型FETとディプレッション型FETとを集積する場合に製造工程数の削減を実現できる半導体装置の製造方法を提供する。

【解決手段】この製造方法は、アクティブ領域11を横断しゲート電極10Aよりも長さが短いゲート電極10Bを形成する工程と、ゲート電極10A,10Bをマスクとして、アクティブ領域11に不純物を斜めイオン注入することにより、ゲート電極10Aのゲート長方向両側の領域に互いに連続しない不純物拡散領域20a,20bを形成するとともに、ゲート電極10Bのゲート長方向両側の一方の領域から他方の領域に亘って連続する不純物拡散領域20g,20hを形成する斜めイオン注入工程とを含む。

(もっと読む)

不揮発性半導体記憶装置及びディプレッション型MOSトランジスタ

【課題】トランジスタの耐圧を向上し、動作信頼性を向上出来る不揮発性半導体記憶装置及びディプレッション型MOSトランジスタを提供すること。

【解決手段】ゲート電極26と、第1不純物濃度を有するチャネル領域22と、第1不純物濃度よりも大きな第2不純物濃度を有するソース・ドレイン拡散領域21と、チャネル領域22とソース・ドレイン拡散領域21とが重複する領域に形成され、第2不純物濃度よりも大きな第3不純物濃度を有する重複領域24と、第2不純物濃度よりも大きな第4不純物濃度を有するコンタクト領域23と、ソース・ドレイン拡散領域21の一部領域内に形成され、第2不純物濃度よりも大きく且つ第4不純物濃度よりも小さい第5不純物濃度を有する不純物拡散領域27とを備え、不純物拡散領域27は、コンタクト領域23に接し且つ重複領域24に離隔するようにして形成される。

(もっと読む)

基準電圧発生回路装置

【課題】デプレッション型MOSトランジスタとエンハンス型MOSトランジスタによって形成される基準電圧発生回路装置の面積を大きくすることなく基準電圧の温度特性を向上させる。

【解決手段】デプレッション型MOSトランジスタの濃度プロファイルを、第一導電型チャネル領域の基板表面側の不純物濃度が薄く、かつ前記第一導電型チャネル領域と第二導電型の基板領域もしくはウェル領域にて形成されるPN接合付近の前記第一導電型チャネル領域の不純物濃度が濃くなるように制御することで基準電圧の温度特性を向上させる。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタの製造方法

【課題】オン抵抗が低く、耐圧性及びチャネル移動度が高い電界効果トランジスタ及び電界効果トランジスタの製造方法を提供すること。

【解決手段】MOS構造を有し、窒化化合物半導体からなる電界効果トランジスタであって、基板上に形成されたi型または所定の導電型を有する半導体層と、エピタキシャル成長によって半導体層とソース電極およびドレイン電極のそれぞれとの間に形成された、所定の導電型とは反対の導電型を有するコンタクト層と、エピタキシャル成長によってドレイン電極側のコンタクト層と半導体層との間にゲート電極と重畳するように形成された、所定の導電型とは反対の導電型を有するとともに該コンタクト層よりもキャリア濃度が低い電界緩和層と、エピタキシャル成長によって半導体層上の電界緩和層に隣接する領域に形成された、i型または所定の導電型を有する媒介層と、媒介層上に形成したゲート絶縁膜と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 チャネル抵抗の上昇を最小限に抑えつつ、トランジスタのコンダクタンス特性に優れた半導体装置を提供する。

【解決手段】 半導体基板上にMOS型トランジスタが形成してある半導体装置において、MOS型トランジスタは、ウェルと逆導電の不純物をチャネルドープすることにより形成されるデプレッション型トランジスタであって、かつ、MOS型トランジスタのチャネル領域が、多結晶シリコン層もしくはアモルファスシリコン層からなる第1のチャネル領域と、単結晶シリコン層からなる第2のチャネル領域と、が順次設けられた積層構造を有しており、更に、第1のチャネル領域が、チャネルドープされた領域とウェルとの境界に形成されるPN接合よりも表面側に位置している。

(もっと読む)

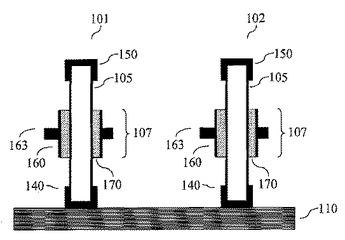

ナノスケール電界効果トランジスタの構体

本発明は、ラップゲート構造を有する縦型ナノワイヤトランジスタに関する。縦型ナノワイヤトランジスタの閾値電圧は、ナノワイヤの直径、ナノワイヤの不純物添加レベル、ナノワイヤへのヘテロ構造のセグメントの導入、ナノワイヤを取り囲むシェル構造における不純物添加、ゲートスタックの仕事関数の適応、歪み調整、誘電体材料の制御又はナノワイヤ材料の選択により制御される。異なる閾値電圧を有するトランジスタが同一の基板上に形成されることにより、直接結合フィールドロジックと同様に、閾値電圧の変化を利用する最先端回路の設計が可能になる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】DMOSトランジスタを含む半導体装置において、チップ面積を小さくすること、及びオン抵抗が低く、電流駆動能力の高いDMOSトランジスタを提供することを目的とする。

【解決手段】N型のエピタキシャル層2の表面に逆導電型(P型)のP+W層4を形成し、当該P+W層4内にDMOSトランジスタ70を形成する。エピタキシャル層2とドレイン領域とは、P+W層4によって絶縁される。そのため、絶縁分離層15で囲まれた一つの領域内に、DMOSトランジスタと他のデバイス素子を混載できる。また、ゲート電極6の下方におけるP+W層4の表面領域にN型のFN層20を形成する。ゲート電極6のドレイン層12側の端部に隣接したN+D層23を形成する。また、ドレイン層12のコンタクト領域の下方に、ドレイン層12よりも深いP型不純物層(P+D層22,FP層24)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ディプリーション型MOSトランジスタのパターン面積を増大させずに、その抵抗を大きくする。

【解決手段】 半導体基板1上にイオン注入することでチャネル領域となる低濃度不純物領域3を形成する。次に、ゲート絶縁膜4及びゲート電極5を形成する。次に、半導体基板1の全面に層間絶縁膜6を形成し、その後当該層間絶縁膜6を選択的にエッチングし、ソース形成領域及びドレイン形成領域をそれぞれ一部露出させるコンタクトホール7を形成する。次に、コンタクトホール7を介してイオン注入・熱処理(アニーリング)し、ソース領域8及びドレイン領域9を形成する。ソース領域8及びドレイン領域9はゲート電極5とオーバーラップせず、ゲート電極5の端部から数μm以上(例えば、3μm)離間して形成されている。

(もっと読む)

応力変形させた半導体装置およびその製造方法

【課題】応力を調整し、性能向上を図った半導体装置、およびその製造法を提供すること。

【解決手段】ゲート電極104は、半導体基板(バルクシリコン基板、SOI層など)102から電気的に絶縁されている。第1側壁スペーサ110がゲート電極104の側壁に沿って形成される。上記犠牲側壁スペーサが第1側壁スペーサ110と隣接するように形成される。上記犠牲側壁スペーサおよび第1側壁スペーサ110は半導体基板102を覆っている。平坦化層は、該平坦化層の一部が上記犠牲側壁スペーサと隣接するように、半導体基板102を覆って形成されている。上記犠牲側壁スペーサが取り除かれ、エッチングによって半導体基板102内にくぼみが形成される。実質的に、上記くぼみは第1側壁スペーサ110と上記平坦化層の一部との間に配置されている。半導体材料(SiGe、SiCなど)116は上記くぼみに堆積される。

(もっと読む)

半導体装置及び該半導体装置を動作させる方法

本発明は、ドレイン延長部(8)を備えるラテラルDMOSTに特に関する。既知のトランジスタにおいて、更なる金属ストリップ(20)は、ゲート電極コンタクトストリップと、ソース領域コンタクト(15)に電気的に接続されているドレインコンタクト(16)との間に位置される。本特許出願において提案される装置において、更なる金属ストリップ(20)とソースコンタクト(15,12)との間の接続部は、コンデンサ(30)を有し、更なる金属ストリップ(20)は更なる金属ストリップ(20)に電圧を供給するための更なるコンタクト領域(35)を備えている。このようにして、改善された線形性が実現可能であり、当該装置の実用性が、特に、高電力及び高周波数において改善される。好ましくは、コンデンサ(30)は、単一の半導体基体(1)内にトランジスタと一体化されている。本発明は、更に、本発明による装置(10)を動作させる方法を有する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 ドレイン電流を低下させることなくドレイン耐圧を向上させることができる半導体装置を提供する。

【解決手段】 半導体装置100は、半導体層(2)上に設けられたゲート電極(3)と、ゲート電極(3)を挟むように半導体層(2)上に設けられたソース電極(5)およびドレイン電極(9)と、半導体層(2)上のゲート電極(3)とドレイン電極(9)との間に設けられた電極(10)とを備え、電極(10)の半導体層(2)側の先端部におけるゲート・ドレイン電極間方向の幅は、10nm以上300nm以下であることを特徴とする。

(もっと読む)

半導体集積回路装置

【課題】微細化されたMISFETのしきい値電圧のばらつきを低減する。

【解決手段】MISFET(Q1)のゲート電極9aは、素子分離溝2によって周囲を規定されたアクティブ領域Lの基板1上に形成され、アクティブ領域Lを横切ってその一端から他端に延在している。このゲート電極9aは、アクティブ領域Lと素子分離溝2との境界領域におけるゲート長がアクティブ領域Lの中央部におけるゲート長よりも大きく、全体としてH形の平面パターンで構成されている。また、このゲート電極9aは、アクティブ領域Lと素子分離溝2との境界領域のゲート長方向に沿った一辺の全体とゲート幅方向に沿った二辺の一部とを覆っている。

(もっと読む)

Nチャネルプルアップ素子および論理回路

【課題】相補型(CMOS)集積回路におけるプルアップデバイスとしてPMOSFETの代替品となる新たな種類のnチャネルMOSFETを提供する。

【解決手段】切換可能な負性微分抵抗(SNDR)特性を有するnチャネルFETを開示している。このSNDRFETをデプリーションモードデバイスとして構成し、実質的にpチャネルデバイスとして動作するようにバイアスをかける。このデバイスはnチャネルデバイスであるから、動作速度は高く、一方、大規模回路として設計製造する際のプロセス技術の複雑性は緩和される。このデバイスはCMOSに匹敵する性能を達成するので論理ゲート(インバータに含まれるものなど)におけるpチャネルプルアップデバイスの代替品として好適である。

(もっと読む)

1 - 20 / 22

[ Back to top ]